# Single-channel HOTLink II™ Transceiver

### Features

- Second-generation HOTLink<sup>®</sup> technology

- Compliant to multiple standards

ESCON<sup>®</sup>, DVB-ASI, Fibre Channel and Gigabit Ethernet (IEEE802.3z)

- CPRI™ compliant

- CYW15G0101DXB compliant to OBSAI-RP3

- CYV15G0101DXB compliant to SMPTE 259M and SMPTE 292M

- 8B/10B encoded or 10-bit unencoded data

- Single-channel transceiver operates from 195 to 1500 MBaud serial data rate

- CYW15G0101DXB operates from 195 to 1540 MBaud

- · Selectable parity check/generate

- Selectable input clocking options

- Selectable output clocking options

- MultiFrame™ Receive Framer

- -Bit and Byte alignment

- Comma or full K28.5 detect

- Single- or Multi-Byte framer for byte alignment

- -Low-latency option

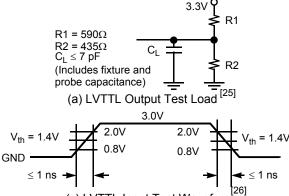

- Synchronous LVTTL parallel input and parallel output interface

- Internal phase-locked loops (PLLs) with no external PLL components

- Dual differential PECL-compatible serial inputs

—Internal DC-restoration

- Dual differential PECL-compatible serial outputs

Source matched for driving 50Ω transmission lines

- -No external bias resistors required

- -Signaling-rate controlled edge-rates

- Optional Elasticity Buffer in Receive Path

- Optional Phase Align Buffer in Transmit Path

- Compatible with

- -Fiber-optic modules

- Copper cables

- -Circuit board traces

- JTAG boundary scan

- Built-In Self-Test (BIST) for at-speed link testing

- Per-channel Link Quality Indicator

- —Analog signal detect

- Digital signal detect

- Low power 1.25W @ 3.3V typical

- Single 3.3V supply

- 100-ball BGA

- Pb-Free package option available

- 0.25µ BiCMOS technology

### **Functional Description**

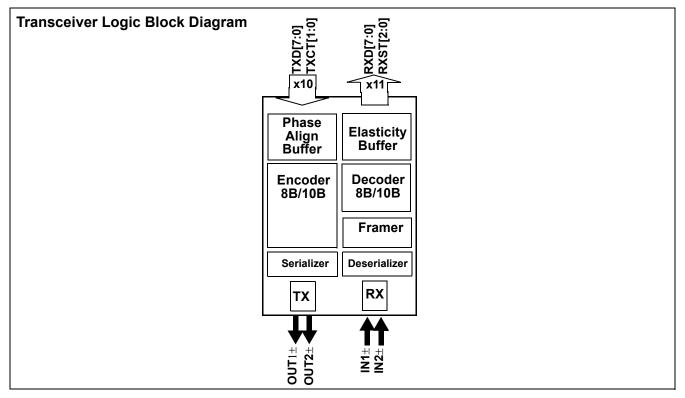

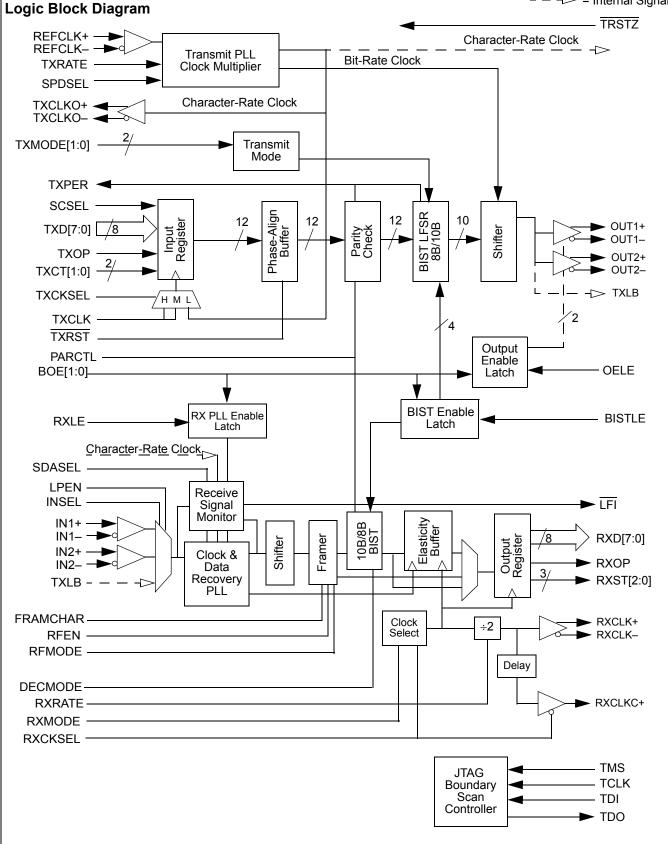

The CYP(V)15G0101DXB<sup>[1]</sup> single-channel HOTLink II™ transceiver is a point-to-point communications building block allowing the transfer of data over a high-speed serial link (optical fiber, balanced, and unbalanced copper transmission lines) at signaling speeds ranging from 195 to 1500 MBaud.

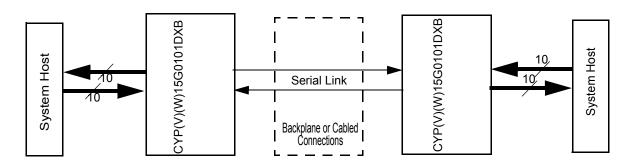

The transmit channel accepts parallel characters in an Input Register, encodes each character for transport, and converts it to serial data. The receive channel accepts serial data and converts it to parallel data, frames the data to character boundaries, decodes the framed characters into data and special characters, and presents these characters to an Output Register. Figure 1 illustrates typical connections between independent host systems and corresponding CYP(V)(W)15G0101DXB parts. As a second-generation HOTLink device, the CYP(V)(W)15G0101DXB extends the HOTLink II family with enhanced levels of integration and faster data rates, while maintaining serial-link compatibility (data, command, and BIST) with other HOTLink devices.

#### Note:

Figure 1. HOTLink II System Connections

CYV15G0101DXB refers to SMPTE 259M and SMPTE 292M compliant devices. CYW15G0101DXB refers to OBSAI RP3 compliant devices (maximum operating data rate is 1540 MBaud). CYP15G0101DXB refers to devices not compliant to SMPTE 259M and SMPTE 292M pathological test requirements and also OBSAI RP3 operating datarate of 1536 MBaud. CYP(V)(W)15G0101DXB refers to all three devices.

**Cypress Semiconductor Corporation** Document #: 38-02031 Rev. \*J 3901 North First Street

The CYW15G0101DXB<sup>[1]</sup> operates from 195 to 1540 MBaud, which includes operation at the OBSAI RP3 datarate of both 1536 MBaud and 768 MBaud.

The CYV15G0101DXB satisfies the SMPTE 259M and SMPTE 292M compliance as per the EG34-1999 Pathological Test Requirements. The transmit (TX) section of the CYP(V)(W)15G0101DXB single-channel HOTLink II consists of a byte-wide channel. The channel can accept either eight-bit data characters or pre-encoded 10-bit transmission characters. Data characters are passed from the Transmit Input Register to an embedded 8B/10B Encoder to improve their serial transmission characteristics. These encoded characters are then serialized and output from dual Positive ECL (PECL)-compatible differential transmission-line drivers at a bit-rate of either 10 or 20 times the input reference clock.

The receive (RX) section of the CYP(V)(W)15G0101DXB Single-channel HOTLink II consists of a byte-wide channel. The channel accepts a serial bit-stream from one of two PECL-compatible differential Line Receivers and, using a completely integrated PLL Clock Synchronizer, recovers the timing information necessary for data reconstruction. The recovered bit-stream is deserialized and framed into characters, 8B/10B decoded, and checked for transmission errors. Recovered decoded characters are then written to an internal Elasticity Buffer, and presented to the destination host system. The integrated 8B/10B Encoder/Decoder may be bypassed for systems that present externally encoded or scrambled data at the parallel interface. The parallel I/O interface may be configured for numerous forms of clocking to provide the highest flexibility in system architecture. In addition to clocking the transmit path interfaces from one or multiple sources, the receive interface may be configured to present data relative to a recovered clock or to a local reference clock.

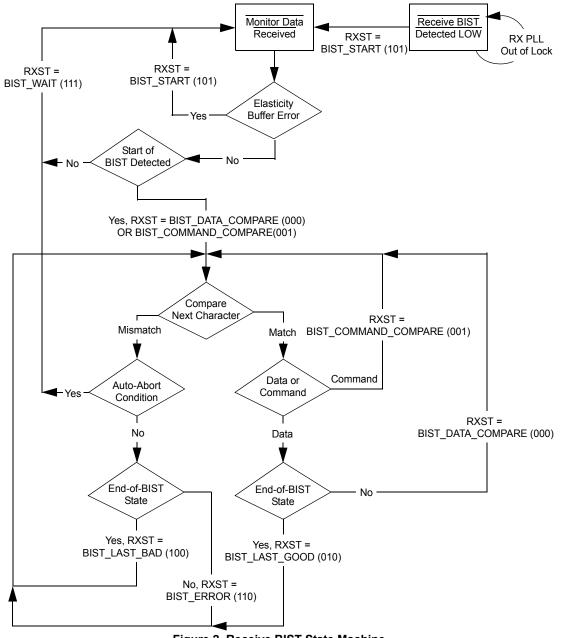

The transmit and the receive channels contain BIST pattern generators and checkers, respectively. This BIST hardware allows at-speed testing of the high-speed serial data paths in both transmit and receive sections, as well as across the interconnecting links.

HOTLink II devices are ideal for a variety of applications where parallel interfaces can be replaced with high-speed, point-to-point serial links. Some applications include interconnecting backplanes on switches, routers, base-stations, servers and video transmission systems.

The CYV15G0101DXB is verified by testing to be compliant to all the pathological test patterns documented in SMPTE EG34-1999, for both the SMPTE 259M and 292M signaling rates. The tests ensure that the receiver recovers data with no errors for the following patterns:

- 1. Repetitions of 20 ones and 20 zeros.

- 2. Single burst of 44 ones or 44 zeros.

- 3. Repetitions of 19 ones followed by 1 zero or 19 zeros followed by 1 one.

- - - - → = Internal Signal

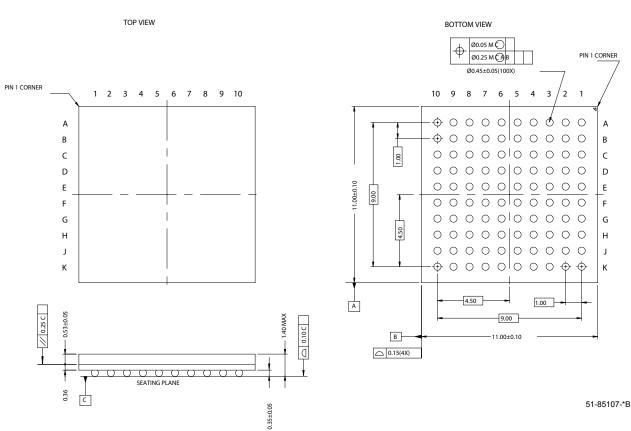

**Pin Configuration**

**Top View**

|   | 1               | 2           | 3               | 4       | 5          | 6         | 7      | 8                  | 9                  | 10                 |

|---|-----------------|-------------|-----------------|---------|------------|-----------|--------|--------------------|--------------------|--------------------|

| A | V <sub>CC</sub> | IN2+        | V <sub>CC</sub> | OUT2-   | RXMODE     | TXMODE[1] | IN1+   | V <sub>CC</sub>    | OUT1-              | V <sub>CC</sub>    |

| в | V <sub>CC</sub> | IN2-        | TDO             | OUT2+   | TXRATE     | TXMODE[0] | IN1–   | #NC <sup>[2]</sup> | OUT1+              | V <sub>CC</sub>    |

| с | RFEN            | LPEN        | RXLE            | RXCLKC+ | RXRATE     | SDASEL    | SPDSEL | PARCTL             | RFMODE             | INSEL              |

| D | BOE[0]          | BOE[1]      | FRAMCHA<br>R    | GND     | GND        | GND       | GND    | TMS                | TRSTZ              | TDI                |

| Е | BISTLE          | DECMOD<br>E | OELE            | GND     | GND        | GND       | GND    | TCLK               | RXCKSEL            | TXCKSEL            |

| F | RXST[2]         | RXST[1]     | RXST[0]         | GND     | GND        | GND       | GND    | TXPER              | REFCLK-            | REFCLK+            |

| G | RXOP            | RXD[1]      | RXD[5]          | GND     | GND        | GND       | GND    | TXOP               | TXCLKO+            | TXCLKO-            |

| н | RXD[0]          | RXD[2]      | RXD[6]          | LFI     | TXCT[1]    | TXD[6]    | TXD[3] | TXCLK              | TXRST              | #NC <sup>[2]</sup> |

| J | V <sub>CC</sub> | RXD[3]      | RXD[7]          | RXCLK-  | TXCT[0]    | TXD[5]    | TXD[2] | TXD[0]             | #NC <sup>[2]</sup> | V <sub>CC</sub>    |

| к | V <sub>CC</sub> | RXD[4]      | V <sub>CC</sub> | RXCLK+  | TXD[7]     | TXD[4]    | TXD[1] | $V_{CC}$           | SCSEL              | V <sub>CC</sub>    |

|   |                 |             |                 |         | Rottom Via |           |        |                    | •                  |                    |

#### **Bottom View**

| 10                 | 9                  | 8                  | 7      | 6         | 5       | 4       | 3               | 2           | 1               |   |

|--------------------|--------------------|--------------------|--------|-----------|---------|---------|-----------------|-------------|-----------------|---|

| V <sub>CC</sub>    | OUT1-              | V <sub>CC</sub>    | IN1+   | TXMODE[1] | RXMODE  | OUT2-   | V <sub>CC</sub> | IN2+        | V <sub>CC</sub> | A |

| V <sub>CC</sub>    | OUT1+              | #NC <sup>[2]</sup> | IN1–   | TXMODE[0] | TXRATE  | OUT2+   | TDO             | IN2-        | V <sub>CC</sub> | В |

| INSEL              | RFMODE             | PARCTL             | SPDSEL | SDASEL    | RXRATE  | RXCLKC+ | RXLE            | LPEN        | RFEN            | с |

| TDI                | TRSTZ              | TMS                | GND    | GND       | GND     | GND     | FRAMCHA<br>R    | BOE[1]      | BOE[0]          | D |

| TXCKSEL            | RXCKSEL            | TCLK               | GND    | GND       | GND     | GND     | OELE            | DECMOD<br>E | BISTLE          | E |

| REFCLK+            | REFCLK-            | TXPER              | GND    | GND       | GND     | GND     | RXST[0]         | RXST[1]     | RXST[2]         | F |

| TXCLKO-            | TXCLKO+            | TXOP               | GND    | GND       | GND     | GND     | RXD[5]          | RXD[1]      | RXOP            | G |

| #NC <sup>[2]</sup> | TXRST              | TXCLK              | TXD[3] | TXD[6]    | TXCT[1] | LFI     | RXD[6]          | RXD[2]      | RXD[0]          | н |

| V <sub>CC</sub>    | #NC <sup>[2]</sup> | TXD[0]             | TXD[2] | TXD[5]    | TXCT[0] | RXCLK-  | RXD[7]          | RXD[3]      | V <sub>CC</sub> | J |

| V <sub>CC</sub>    | SCSEL              | V <sub>CC</sub>    | TXD[1] | TXD[4]    | TXD[7]  | RXCLK+  | V <sub>CC</sub> | RXD[4]      | V <sub>CC</sub> | к |

Note:

2. #NC = Do Not Connect.

| <b>h Data Signals</b><br>LVTTL Output,<br>changes relative to<br>REFCLK↑ <sup>[3]</sup>               | <b>Transmit Path Parity Error</b> . Active HIGH. Asserted (HIGH) if parity checking is enabled (PARCTL $\neq$ LOW) and a parity error is detected at the Encoder. This output is HIGH for one transmit character-clock period to indicate detection of a parity error in the character presented to the Encoder.<br>If a parity error is detected, the character in error is replaced with a C0.7 character to force                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| changes relative to                                                                                   | (PARCTL $\neq$ LOW) and a parity error is detected at the Encoder. This output is HIGH for one transmit character-clock period to indicate detection of a parity error in the character presented to the Encoder.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                       | If a parity error is detected, the character in error is replaced with a C0.7 character to force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1                                                                                                     | a corresponding bad-character detection at the remote end of the link. This replacement takes place regardless of the encoded/un-encoded state of the interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                       | When BIST is enabled for the specific transmit channel, BIST progress is presented on this output. Once every 511 character times (plus a 16-character Word Sync Sequence when the receive channel is clocked by REFCLK, i.e., RXCKSEL = LOW), the TXPER signal pulses HIGH for one transmit-character clock period (if RXCKSEL = MID) or seventeen transmit-character clock periods (if RXCKSEL = LOW or HIGH) to indicate a complete pass through the BIST sequence. For RXCKSEL = LOW or HIGH, If TXMODE[1:0] = LL, then no Word Sync Sequence is sent in BIST, and TXPER pulses HIGH for one transmit-character clock period. |

|                                                                                                       | This output also provides an indication of a Phase-Align Buffer underflow/overflow condition. When the Phase-Align Buffer is enabled (TXCKSEL $\neq$ LOW, or TXCKSEL = LOW and TXRATE = HIGH), and an underflow/overflow condition is detected, TXPER is asserted and remains asserted until either an atomic Word Sync Sequence is transmitted or TXRST is sampled LOW to recenter the Phase-Align Buffer.                                                                                                                                                                                                                       |

| LVTTL Input,<br>synchronous,<br>sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup>                        | <b>Transmit Control</b> . These inputs are captured on the rising edge of the transmit interface clock as selected by TXCKSEL, and are passed to the Encoder or Transmit Shifter. They identify how the TXD[7:0] characters are interpreted. When the Encoder is enabled, these inputs determine if the TXD[7:0] character is encoded as Data, a Special Character code, a K28.5 fill character or a Word Sync Sequence. When the Encoder is bypassed, these inputs are interpreted as data bits. See <i>Table 1</i> for details.                                                                                                 |

| LVTTL Input,<br>synchronous,                                                                          | <b>Transmit Data Inputs</b> . These inputs are captured on the rising edge of the transmit interface clock as selected by TXCKSEL, and passed to the Encoder or Transmit Shifter.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup>                                                        | When the Encoder is enabled (TXMODE[1] $\neq$ LOW), TXD[7:0] specify the specific data or command character to be sent. When the Encoder is bypassed, these inputs are interpreted as data bits of the 10-bit input character. See <i>Table 1</i> for details.                                                                                                                                                                                                                                                                                                                                                                    |

| LVTTL Input,<br>synchronous,<br>internal pull-up,<br>sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup>   | <b>Transmit Path Odd Parity</b> . When parity checking is enabled (PARCTL $\neq$ LOW), the parity captured at this input is XORed with the data on the TXD bus (and sometimes TXCT[1:0]) to verify the integrity of the captured character. See <i>Table 2</i> for details.                                                                                                                                                                                                                                                                                                                                                       |

| LVTTL Input,<br>synchronous,<br>internal pull-down,<br>sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup> | <b>Special Character Select</b> . Used in some transmit modes along with TXCTx[1:0] to encode special characters or to initiate a Word Sync Sequence. When the transmit path is configured to select TXCLK to clock the input register (TXCKSEL = MID or HIGH), SCSEL is captured relative to TXCLK <sup>↑</sup> .                                                                                                                                                                                                                                                                                                                |

|                                                                                                       | synchronous,<br>sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup><br>LVTTL Input,<br>synchronous,<br>sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup><br>LVTTL Input,<br>synchronous,<br>internal pull-up,<br>sampled by TXCLK↑<br>or REFCLK↑ <sup>[3]</sup><br>LVTTL Input,<br>synchronous,<br>internal pull-down,<br>sampled by TXCLK↑                                                                                                                                                                                                                                                                                               |

Note: 3. When REFCLK is configured for half-rate operation (TXRATE = HIGH), this input is sampled (or the outputs change) relative to both the rising and falling edges of REFCLK.

| Pin Name          | I/O Characteristics                                                                        | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXRST             | LVTTL Input,<br>asynchronous,<br>internal pull-up,<br>sampled by<br>REFCLK <sup>1[3]</sup> | <b>Transmit Clock Phase Reset</b> . Active LOW. When sampled LOW, the transmit Phase-align Buffer is allowed to adjust its data-transfer timing (relative to the selected input clock) to <u>allow cl</u> ean transfer of data from the Input Register to the Encoder or Transmit Shifter. When TXRST is sampled HIGH, the internal phase relationship between the TXCLK and the internal character-rate clock is fixed and the device operates normally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   |                                                                                            | When configured for half-rate REFCLK sampling of the transmit character stream (TXCKSEL = LOW and TXRATE = HIGH), assertion of TXRST is only used to clear Phase-align buffer faults caused by highly asymmetric reference clock periods or reference clocks with excessive cycle-to-cycle jitter. During this alignment period, one or more characters may be added to or lost from all the associated transmit paths as the transmit Phase-align Buffers are adjusted. TXRST must be sampled LOW by a minimum of two consecutive rising edges of REFCLK to ensure the reset operation is initiated correctly on all channels. This input is ignored when both TXCKSEL and TXRATE are LOW, since the phase align buffer is bypassed. In all other configurations, TXRST should be asserted during device initialization to ensure proper operation of the Phase-align buffer. TXRST should be asserted after the assertion and deassertion of TRSTZ, after the presence of a valid TXCLK and after allowing enough time for the TXPLL to lock to the reference clock (as specified by parameter $t_{TXLOCK}$ ). |

|                   | h Clock and Clock C                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

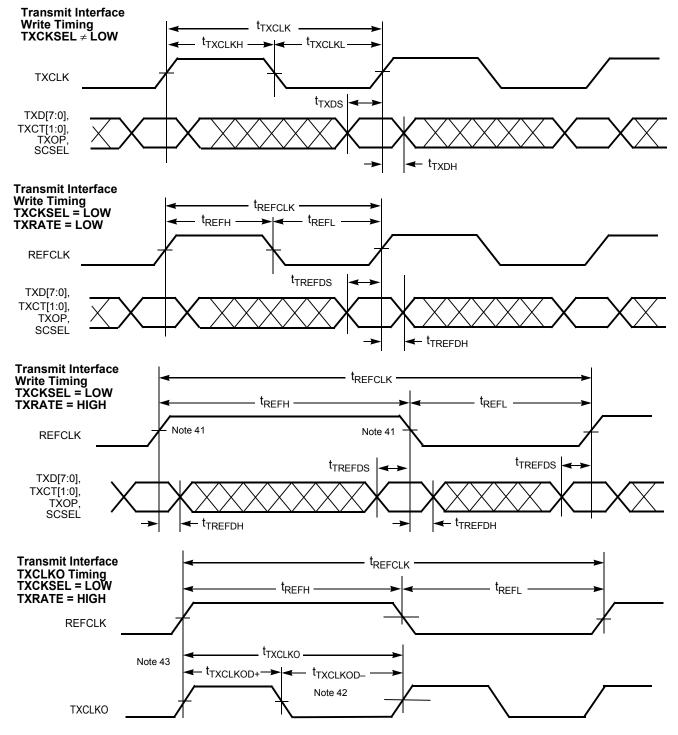

| TXCKSEL           | 3-Level Select static control input <sup>[4]</sup>                                         | <b>Transmit Clock Select</b> . Selects the clock source used to write data into the Transmit Input Register of the transmit channel. When LOW, the Input Register is clocked by REFCLK <sup>1,3</sup> When HIGH or MID, TXCLK <sup>↑</sup> is the Input Register clock for TXD[7:0] and TXCT[1:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                   |                                                                                            | When TXRATE=HIGH, configuring TXCKSEL = HIGH or MID is an invalid mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

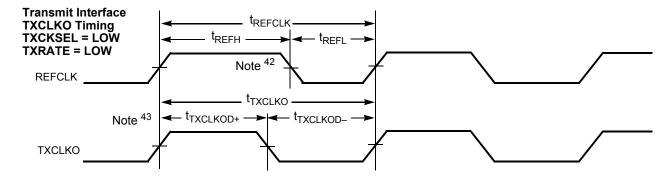

| TXCLKO±           | LVTTL Output                                                                               | <b>Transmit Clock Output</b> . This true and complement output clock is synthesized by the transmit PLL and is synchronous to the internal transmit character clock. It has the same frequency as REFCLK (when TXRATE = LOW), or twice the frequency of REFCLK (when TXRATE = HIGH). This output clock has no direct phase relationship to REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TXRATE            | LVTTL Input,<br>Static Control input,                                                      | <b>Transmit PLL Clock Rate Select</b> . When TXRATE = HIGH, the Transmit PLL multiplies REFCLK by 20 to generate the serial bit-rate clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   | internal pull-down                                                                         | When TXRATE = LOW, the transmit PLL multiplies REFCLK by 10 to generate the serial bit-rate clock. See <i>Table 9</i> for a list of operating serial rates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                            | When REFCLK is selected to clock the receive parallel interfaces (RXCKSEL = LOW), the TXRATE input also determines if the clocks on the RXCLK $\pm$ and RXCLKC+ outputs are full or half-rate. When TXRATE = HIGH (REFCLK is half-rate), the RXCLK $\pm$ and RXCLKC+ output clocks are also half-rate clocks and follow the frequency and duty cycle of the REFCLK input. When TXRATE = LOW (REFCLK is full-rate), the RXCLK $\pm$ and RXCLKC+ output clocks are also full-rate clocks and follow the frequency and duty cycle of the REFCLK is are also full-rate clocks and follow the frequency and duty cycle of the REFCLK input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                            | When TXRATE=HIGH, configuring TXCKSEL = HIGH or MID is an invalid mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TXCLK             | LVTTL Clock Input,<br>internal pull-down                                                   | <b>Transmit Path Input Clock</b> . This clock must be frequency-coherent to TXCLKO±, but may be offset in phase. The internal operating phase of the input clock (relative to REFLCK or TXCLKO+) is adjusted when TXRST = LOW and locked when TXRST = HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Transmit Pat      | h Mode Control                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| in an on inter at |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

4. 3-Level select inputs are used for static configuration. They are ternary (not binary) inputs that make use of non-standard logic levels of LOW, MID, and HIGH. The LOW level is usually implemented by direct connection to V<sub>SS</sub> (ground). The HIGH level is usually implemented by direct connection to V<sub>CC</sub> (power). When not connected or allowed to float, a 3-Level select input will self-bias to the MID level.

| Pin Name    | I/O Characteristics                                                                                 | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | h Data Signals                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

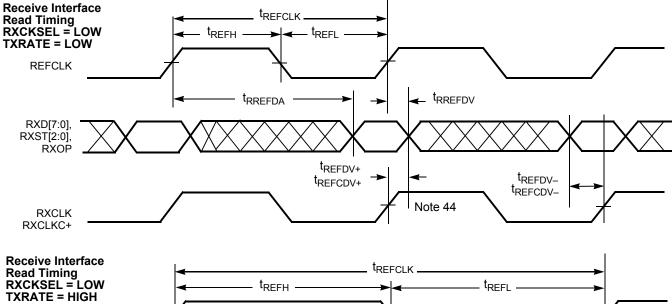

| RXD[7:0]    | LVTTL Output,<br>synchronous to the                                                                 | <b>Parallel Data Output</b> . These outputs change following the rising edge of the selected receive interface clock.                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | RXCLK↑ output<br>(or REFCLK↑ input <sup>[3]</sup><br>when RXCKSEL =<br>LOW)                         | When the Decoder is enabled (DECMODE = HIGH or MID), these outputs represent either received data or a special character. The status of the received data is represented by the values of RXST[2:0].                                                                                                                                                                                                                                                                                                                   |

|             |                                                                                                     | When the Decoder is bypassed (DECMODE = LOW), RXD[7:0] become the higher order bits of the 10-bit received character. See <i>Table 13</i> for details.                                                                                                                                                                                                                                                                                                                                                                 |

| RXST[2:0]   | LVTTL Output,<br>synchronous to the                                                                 | <b>Parallel Status Output</b> . These outputs change following the rising edge of the selected receive interface clock.                                                                                                                                                                                                                                                                                                                                                                                                |

|             | RXCLK <sup>↑</sup> output<br>(or REFCLK <sup>↑</sup> input <sup>[3]</sup><br>when RXCKSEL =<br>LOW) | When the Decoder is bypassed (DECMODE = LOW), RXST[1:0] become the two low-order bits of the 10-bit received character, while RXST[2] = HIGH indicates the presence of a Comma character in the Output Register.                                                                                                                                                                                                                                                                                                       |

|             |                                                                                                     | When the Decoder is enabled (DECMODE = HIGH or MID), RXST[2:0] provide status of the received signal. See <i>Table 16</i> for a list of Receive Character status.                                                                                                                                                                                                                                                                                                                                                      |

| RXOP        | 3-state, LVTTL<br>Output, synchronous                                                               | <b>Receive Path Odd Parity.</b> When parity generation is enabled (PARCTL $\neq$ LOW), the parity output is valid for the data on the RXD bus bits.                                                                                                                                                                                                                                                                                                                                                                    |

|             | to the RXCLK↑<br>output (or REFCLK↑<br>input <sup>[3]</sup> when<br>RXCKSEL = LOW)                  | When parity generation is disabled (PARCTL = LOW), this output driver is disabled (High-Z).                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Receive Pat | h Clock and Clock Co                                                                                | potrol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

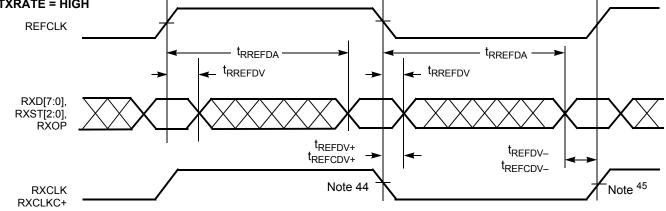

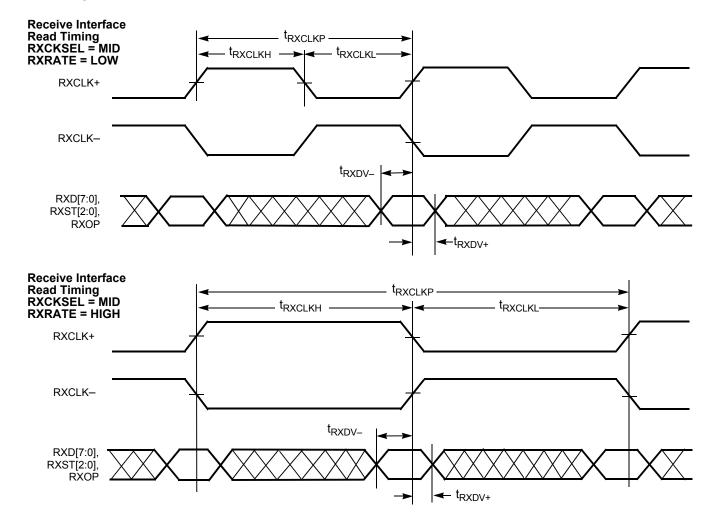

| RXCLK±      | 3-state, LVTTL<br>Output clock                                                                      | <b>Receive Character Clock Output</b> . When configured such that the output data path is clocked by the recovered clock (RXCKSEL = MID), these true and complement clocks are the receive interface clocks which are used to control timing of output data (RXD[7:0], RXST[2:0] and RXOP). This clock is output continuously at either the dual-character rate (1/20 <sup>th</sup> the serial bit-rate) or character rate (1/10 <sup>th</sup> the serial bit-rate) of the data being received, as selected by RXRATE. |

|             |                                                                                                     | When configured such that the output data path is clocked by REFCLK instead of recovered clock (RXCKSEL = LOW), the RXCLK± output drivers present a buffered and delayed form of REFCLK. In this mode, RXCLK± and RXCLKC+ are buffered forms of REFCLK that are slightly different in phase, but follow the frequency and duty cycle of REFCLK. This phase difference allows the user to select the optimal set-up/hold timing for their specific interface.                                                           |

| RXCLKC+     | 3-state, LVTTL<br>Output                                                                            | <b>Delayed REFCLK+ when RXCKSEL = LOW</b> . Delayed form of REFCLK+, used for transfer of output data to a host system. This output is only enabled when the receive parallel interface is configured to present data relative to REFCLK (RXCKSEL = LOW). When RXCKSEL = LOW, the RXCLKC+ follows the frequency and duty cycle of REFCLK+.                                                                                                                                                                             |

| RXRATE      | LVTTL Input<br>Static Control Input,<br>internal pull-down                                          | <b>Receive Clock Rate Select</b> . When LOW, the RXCLK± recovered clock outputs are comple-<br>mentary clocks operating at the recovered character rate. Data for the receive channel<br>should be latched on either the rising edge of RXCLK+ or falling edge of RXCLK–.                                                                                                                                                                                                                                              |

|             |                                                                                                     | When HIGH, the RXCLK $\pm$ recovered clock outputs are complementary clocks operating at half the character rate. Data for the receive channel should be latched alternately on the rising edge of RXCLK+ and RXCLK–.                                                                                                                                                                                                                                                                                                  |

|             |                                                                                                     | When the output register is operated with REFCLK clocking (RXCKSEL = LOW), RXRATE is not interpreted and RXCLK± follows the frequency and duty cycle of REFCLK.                                                                                                                                                                                                                                                                                                                                                        |

| RFEN        | LVTTL input,<br>asynchronous,<br>internal pull-down                                                 | <b>Reframe Enable</b> . Active HIGH. When HIGH, the Framer in the receive channel is enabled to frame per the presently enabled framing mode and selected framing character.                                                                                                                                                                                                                                                                                                                                           |

| RXMODE      | 3-Level Select <sup>[4]</sup><br>static control input                                               | <b>Receive Operating Mode</b> . This input selects one of two RXST channel status reporting modes and is only interpreted when the Decoder is enabled (DECMODE $\neq$ LOW). See <i>Table 12</i> for details.                                                                                                                                                                                                                                                                                                           |

| Pin Name     | I/O Characteristics                                    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAMCHAR     | 3-Level Select <sup>[4]</sup><br>static control input  | Framing Character Select. Used to select the character or portion of a character used for character framing of the received data streams.                                                                                                                                                                                                                                                                                                                                                                               |

|              |                                                        | When MID, the Framer looks for both positive and negative disparity versions of the eight-bit Comma character.                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |                                                        | When HIGH, the Framer looks for both positive and negative disparity versions of the K28.5 character.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                                                        | Configuring FRAMCHAR = LOW is reserved for component test.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RFMODE       | 3-Level Select<br>static control input <sup>[4]</sup>  | <b>Reframe Mode Select</b> . Used to select the type of character framing used to adjust the character boundaries (based on detection of one or more framing characters in the data stream. This signal operates in conjunction with the type of framing character selected.                                                                                                                                                                                                                                            |

|              |                                                        | When LOW, the Low-Latency Framer is selected. This will frame on each occurrence of the selected framing character(s) in the received data stream. This mode of framing stretches the recovered character-rate clock for one or multiple cycles to align that clock with the recovered data.                                                                                                                                                                                                                            |

|              |                                                        | When MID, the Cypress-mode Multi-Byte parallel Framer is selected. This requires a pair of the selected framing character(s), on identical 10-bit boundaries, within a span of 50 bits (five characters), before the character boundaries are adjusted. The recovered character clock remains in the same phase regardless of character offset.                                                                                                                                                                         |

|              |                                                        | When HIGH, the Alternate-mode Multi-Byte parallel Framer is selected. This requires detection of the selected framing character(s) in the received data stream, on identical 10-bit boundaries, on four directly adjacent characters. The recovered character clock remains in the same phase regardless of character offset.                                                                                                                                                                                           |

| PARCTL       | 3-Level Select                                         | Parity Check/Generate Control. Used to control the parity check and generate functions.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | static control input <sup>[4]</sup>                    | When LOW, parity checking is disabled, and the RXOP output is disabled (High-Z).                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              |                                                        | When MID, and the 8B/10B Encoder and Decoder are enabled (TXMODE[1] $\neq$ LOW, DECMODE $\neq$ LOW), TXD[7:0] inputs are checked (along with TXOP) for valid ODD parity, and ODD parity is generated for the RXD[7:0] outputs and presented on RXOP. When the 8B/10B Encoder and Decoder are disabled (TXMODE[1] = LOW, DECMODE = LOW), the TXD[7:0] and TXCT[1:0] inputs are checked (along with TXOP) for valid ODD parity, and ODD parity is generated for the RXD[7:0] and RXST[1:0] outputs and presented on RXOP. |

|              |                                                        | When HIGH, parity generation and checking are enabled. The TXD[7:0] and TXCT[1:0] inputs are checked (along with TXOP) for valid ODD parity, and ODD parity is generated for the RXD[7:0] and RXST[2:0] outputs and presented on RXOP.                                                                                                                                                                                                                                                                                  |

|              |                                                        | See Table 2 and Table 15 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DECMODE      | 3-Level Select<br>static control input <sup>[4]</sup>  | <b>Decoder Mode Select</b> . When LOW, the Decoder is bypassed and raw 10-bit characters are passed to the Output Register. When the Decoder is bypassed, RXCKSEL must be MID.                                                                                                                                                                                                                                                                                                                                          |

|              |                                                        | When MID, the Cypress Decoder table for Special Code Characters is used. When HIGH, the alternate Decoder table for Special Code Characters is used. See <i>Table 21</i> for a list of the Special Codes supported in both encoded modes.                                                                                                                                                                                                                                                                               |

| RXCKSEL      | 3-Level Select <sup>[4]</sup><br>static control input  | <b>Receive Clock Mode</b> . Selects the receive clock source used to transfer data to the Output Registers and configures the Elasticity Buffer in the receive path.                                                                                                                                                                                                                                                                                                                                                    |

|              |                                                        | When LOW, the Output Register is clocked by REFCLK. RXCLK $\pm$ and RXCLKC+ present buffered and delayed forms of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                               |

|              |                                                        | When MID, the RXCLK $\pm$ output follows the recovered clock as selected by RXRATE and the Elasticity Buffer is bypassed. When the 10B/8B Decoder and Elasticity Buffer are bypassed (DECMODE=LOW), RXCKSEL must be MID.                                                                                                                                                                                                                                                                                                |

|              |                                                        | Configuring RXCKSEL = HIGH is an invalid mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Device Contr |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SPDSEL       | 3-Level Select, <sup>[4]</sup><br>static control input | Serial Rate Select. This input specifies the operating bit-rate range of both transmit and receive PLLs. LOW = 195–400 MBaud, MID = 400–800 MBaud, HIGH = 800–1500 MBaud (800–1540 MBaud for CYW15G0101DXB). When SPDSEL=LOW, setting TXRATE=HIGH (Half-rate Reference Clock) is invalid.                                                                                                                                                                                                                               |

| Pin Name     | I/O Characteristics                                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK±      | Differential LVPECL<br>or single-ended<br>LVTTL input clock   | <b>Reference Clock</b> . This clock input is used as the timing reference for the transmit PLL. It is also used as the centering frequency of the Range Controller block of the Receive CDR PLLs. This input clock may also be selected to clock the transmit and receive parallel interfaces.                                                                                                                                                                                                                                                                                                                                                                            |

|              |                                                               | When driven by a single-ended LVCMOS or LVTTL clock source, the clock source may be connected to either the true or complement REFCLK input, with the alternate REFCLK input left open (floating). When driven by an LVPECL clock source, the clock must be a differential clock, using both inputs. When TXCKSEL = LOW, REFCLK is also used as the clock for the parallel transmit data (input) interface. When RXCKSEL = LOW and Decoder is enabled, the Elasticity buffer is enabled and REFCLK is used as the clock source for the parallel receive data (output) interface.                                                                                          |

|              |                                                               | If the Elasticity Buffer is used, framing characters will be inserted or deleted to/from the data stream to compensate for frequency differences between the reference clock and recovered clock. When addition happens, a K28.5 will be appended immediately after a framing character is detected in the Elasticity Buffer. When deletion happens, a framing character will be removed from the data stream when detected in the Elasticity Buffer.                                                                                                                                                                                                                     |

|              | LVTTL Input,                                                  | Device Reset. Active LOW. Initializes all state machines and counters in the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TRSTZ        | internal pull-up                                              | When sampled LOW by the rising edge of REFLCK, this input resets the internal state machines <u>and sets</u> the Elasticity Buffer pointers to a nominal offset. When the reset is removed (TRSTZ sampled HIGH by REFCLK <sup>↑</sup> ), the status and data outputs will become deterministic in less than 16 REFCLK cycles. The BISTLE, OELE, and RXLE latches are reset by TRSTZ. If the Elasticity Buffer or the Phase-Align Buffer are used, TRSTZ should be applied after power up to initialize the internal pointers into these memory arrays.                                                                                                                    |

| Analog I/O a | and Control                                                   | be applied aller power up to initialize the internal pointers into these memory arrays.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OUT1±        | CML Differential<br>Output                                    | <b>Primary Differential Serial Data Outputs</b> . These PECL-compatible CML outputs (+3.3V referenced) are capable of driving terminated transmission lines or standard fiber-optic transmitter modules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OUT2±        | CML Differential<br>Output                                    | <b>Secondary Differential Serial Data Outputs</b> . These PECL-compatible CML outputs (+3.3V referenced) are capable of driving terminated transmission lines or standard fiber-optic transmitter modules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IN1±         | LVPECL Differential<br>Input, with internal<br>DC restoration | <b>Primary Differential Serial Data Inputs</b> . These inputs accept the serial data stream for deserialization and decoding. The IN1 $\pm$ serial stream is passed to the receiver Clock and Data Recovery (CDR) circuit to extract the data content when INSEL = HIGH.                                                                                                                                                                                                                                                                                                                                                                                                  |

| IN2±         | LVPECL Differential<br>Input, with internal<br>DC restoration | <b>Secondary Differential Serial Data Inputs</b> . These inputs accept the serial data stream for deserialization and decoding. The IN2 $\pm$ serial stream is passed to the receiver CDR circuit to extract the data content when INSEL = LOW.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INSEL        | LVTTL Input,<br>asynchronous                                  | <b>Receive Input Selector</b> . Determines which external serial bit stream is passed to the receiver CDR. When HIGH, the IN1 $\pm$ input is selected. When LOW, the IN2 $\pm$ input is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDASEL       | 3-Level Select, <sup>[4]</sup><br>static control input        | <b>Signal Detect Amplitude Level Select</b> . Allows selection of one of three predefined amplitude trip points for a valid signal indication, as listed in <i>Table 10</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LPEN         | LVTTL Input,<br>asynchronous,<br>internal pull-down           | <b>Loop-Back-Enable</b> . Active HIGH. When asserted (HIGH), the transmit serial data is internally routed to the receiver CDR circuit.All enabled serial drivers are forced to differential logic "1." All serial data inputs are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OELE         | LVTTL Input,<br>asynchronous,<br>internal pull-up             | <b>Serial Driver Output Enable Latch Enable</b> . Active HIGH. When OELE = HIGH, the signals on the BOE[1:0] inputs directly control the OUTx $\pm$ differential drivers. When the BOE[x] input is HIGH, the associated OUTx $\pm$ differential driver is enabled. When the BOE[x] input is LOW, the associated OUTx $\pm$ differential driver is powered down. When OELE returns LOW, the last values present on BOE[1:0] are captured in the internal Output Enable Latch. The specific mapping of BOE[1:0] signals to transmit output enables is listed in <i>Table 8</i> . If the device is reset (TRSTZ is sampled LOW), the latch is reset to disable both outputs. |

| Pin Name        | I/O Characteristics                               | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BISTLE          | LVTTL Input,<br>asynchronous,<br>internal pull-up | <b>Transmit and Receive BIST Latch Enable</b> . Active HIGH. When BISTLE = HIGH, the signals on the BOE[1:0] inputs directly control the transmit and receive BIST enables. When the BOE[x] input is LOW, the associated transmit or receive channel is configured to generate or compare the BIST sequence. When the BOE[x] input is HIGH, the associated transmit or receive channel is configured for normal data transmission or reception. When BISTLE returns LOW, the last values present on BOE[1:0] are captured in the internal BIST Enable latch. The specific mapping of BOE[1:0] signals to transmit and receive BIST enables is listed in <i>Table 8</i> . When the latch is closed, if the device is reset (TRSTZ is sampled LOW), the latch is reset to disable BIST on both the transmit and receive channels. |