# Ultra Low Dropout 1A, 2A, 3A Low Input Voltage NMOS LDOs

## ISL80111, ISL80112, ISL80113

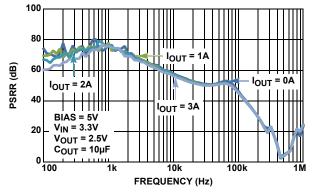

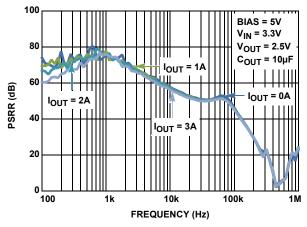

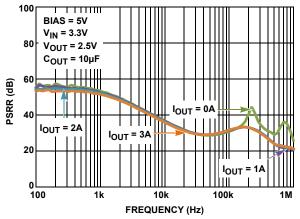

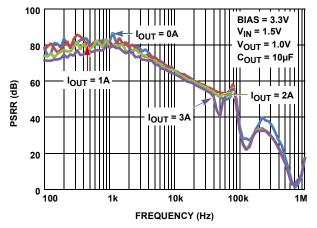

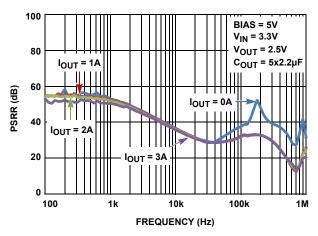

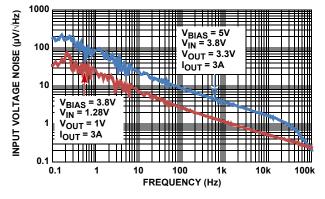

The ISL80111, ISL80112, and ISL80113 are ultra low dropout LDOs providing the optimum balance between performance, size and power consumption in size constrained designs for data communication, computing, storage and medical applications. These LDOs are specified for 1A, 2A and 3A of output current and are optimized for low voltage conversions. Operating with a VIN of 1V to 3.6V and with a legacy 3.3V to 5V on the BIAS, the  $V_{OUT}$  is adjustable from 0.8V to 3.3V. With a  $V_{IN}$  PSRR greater than 40dB at 100kHz makes these LDOs an ideal choice in noise sensitive applications. The guaranteed  $\pm 1.6\%\ V_{OUT}$  accuracy overall conditions lends these parts to suppling an accurate voltage to the latest low voltage digital ICs.

An enable input allows the part to be placed into a low quiescent current shutdown mode. A submicron CMOS process is utilized for this product family to deliver best-in-class analog performance and overall value for applications in need of input voltage conversions typically below 2.5V. It also has the superior load transient regulation unique to a NMOS power stage. These LDOs consume significantly lower quiescent current as a function of load compared to bipolar LDOs.

#### **Features**

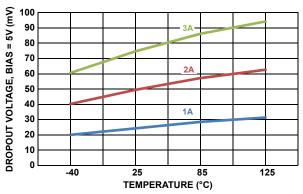

- Ultra Low Dropout: 75mV at 3A, (typ)

- Excellent VIN PSRR: 70dB at 1kHz (typ)

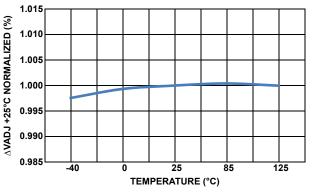

- ±1.6% Guaranteed V<sub>OUT</sub> Accuracy for -40°C < T<sub>I</sub> < +125°C

- · Very Fast Load Transient Response

- Extensive Protection and Reporting Features

- V<sub>IN</sub> Range: 1V to 3.6V, V<sub>OUT</sub> Range: 0.8V to 3.3V

- Small 10 Ld 3x3 DFN Package

## **Applications**

- . Noise-sensitive Instrumentation and Medical Systems

- Data Acquisition and Data Communication Systems

- . Storage, Telecommunications and Server Equipment

- Low Voltage DSP, FPGA and ASIC Core Power Supplies

- Post-regulation of Switched Mode Power Supplies

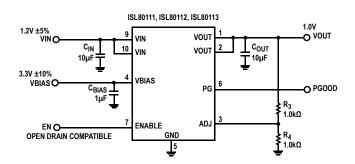

FIGURE 1. TYPICAL APPLICATION SCHEMATIC

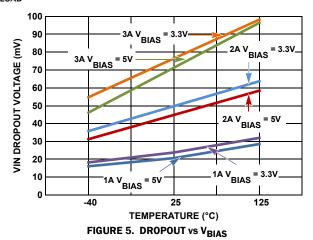

FIGURE 2. DROPOUT VOLTAGE OVER-TEMP AND IOUT

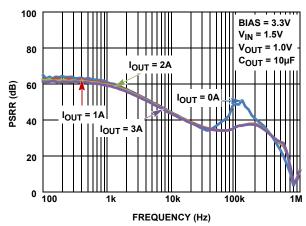

FIGURE 3. V<sub>IN</sub> PSRR vs LOAD CURRENT (ISL80113)

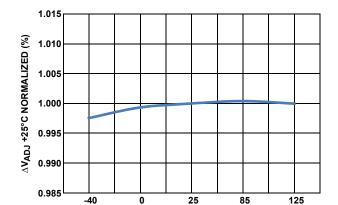

FIGURE 4.  $\Delta V_{ADJ}$  vs TEMPERATURE

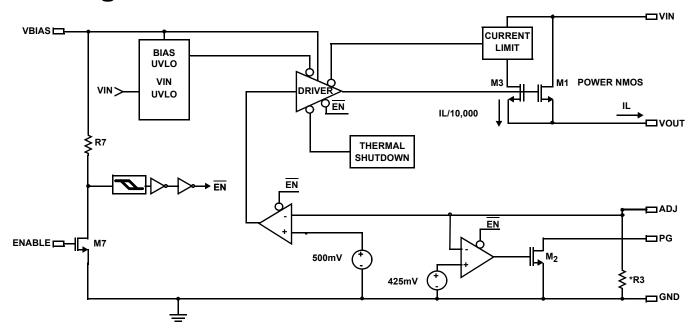

## **Block Diagram**

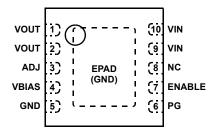

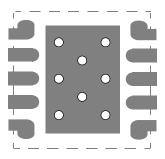

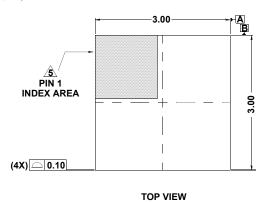

## **Pin Configuration**

ISL80111, ISL80112, ISL80113 (10 LD 3X3 DFN) TOP VIEW

## **Pin Descriptions**

| PIN<br>NUMBER | PIN NAME | DESCRIPTION                                                                                                           |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 1, 2          | VOUT     | Output voltage pin. Range 0.8V to 3.3V                                                                                |

| 3             | ADJ      | ADJ pin for externally setting V <sub>OUT</sub> . Range 0.5V to V <sub>OUT</sub>                                      |

| 4             | VBIAS    | Bias voltage pin for internal control circuits.<br>Range 2.9V to 5.5V                                                 |

| 5             | GND      | Ground pin                                                                                                            |

| 6             | PG       | V <sub>OUT</sub> in regulation signal. Logic low defines when V <sub>OUT</sub> is not in regulation. Range OV to BIAS |

| 7             | ENABLE   | $\rm V_{IN}$ independent chip enable. TTL and CMOS compatible. Range OV to $\rm V_{BIAS}$                             |

| 8             | NC       | No Connect                                                                                                            |

| 9, 10         | VIN      | Input supply pins. Range 1.0V to 3.6V                                                                                 |

|               | EPAD     | EPAD at ground potential. It is recommended to solder the EPAD to the ground plane.                                   |

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART MARKING              | V <sub>OUT</sub> VOLTAGE<br>(Note 3) | AMBIENT TEMP<br>RANGE (°C) | PACKAGE<br>(Pb-Free) | PKG DWG. # |  |

|--------------------------------|---------------------------|--------------------------------------|----------------------------|----------------------|------------|--|

| ISL80111IRAJZ                  | 1ADJ                      | ADJ                                  | -40 to +85                 | 10 Ld 3x3 DFN        | L10.3x3    |  |

| ISL80112IRAJZ                  | 2ADJ                      | ADJ                                  | -40 to +85                 | 10 Ld 3x3 DFN        | L10.3x3    |  |

| ISL80113IRAJZ                  | 3ADJ                      | ADJ                                  | -40 to +85                 | 10 Ld 3x3 DFN        | L10.3x3    |  |

| ISL80111EVAL1Z                 | ISL80111 Evaluation B     | ISL80111 Evaluation Board            |                            |                      |            |  |

| ISL80112EVAL1Z                 | ISL80112 Evaluation B     | ISL80112 Evaluation Board            |                            |                      |            |  |

| ISL80113EVAL1Z                 | ISL80113 Evaluation Board |                                      |                            |                      |            |  |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information pages for <u>ISL80111</u>, <u>ISL80112</u>, and <u>ISL80113</u>. For more information on MSL please see Tech Brief <u>TB363</u>.

#### Absolute Maximum Ratings (Note4)

| V <sub>IN</sub> Relative to GND                 | 0.3 to +6V  |

|-------------------------------------------------|-------------|

| V <sub>OUT</sub> Relative to GND                | 0.3 to +4V  |

| PG, ENABLE, SENSE/ADJ, Relative to GND (Note 5) | 0.3 to +6V  |

| V <sub>BIAS</sub> Relative to GND               | 0.3V to +6V |

| PG Rated Current (Note 6)                       | 10mA        |

| ESD Rating                                      |             |

| Human Body Model (Tested per JESD22-A114E)      | 4000V       |

| Machine Model (Tested per JESD22-115-A)         | 300V        |

| Charged Device Model                            | 2000V       |

| Latch Up                                        | 100mA       |

#### **Thermal Information**

| Thermal Resistance (Notes 7, 8)         | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------------|----------------------|----------------------|

| 10 Ld 3x3 DFN Package                   | 48                   | 4                    |

| Storage Temperature Range               | 6                    | 5°C to +150°C        |

| Pb-Free Reflow Profile                  |                      | see link below       |

| http://www.intersil.com/pbfree/Pb-FreeR | eflow.asp            |                      |

#### **Recommended Operating Conditions (Notes 4, 6)**

| Junction Temperature Range                          | 40°C to +125°C                  |

|-----------------------------------------------------|---------------------------------|

| V <sub>IN</sub> Relative to GND (ISL80113) (Note 9) | . V <sub>OUT</sub> + 0.4V to 5V |

| V <sub>IN</sub> Relative to GND (ISL80112) (Note 9) | . V <sub>OUT</sub> + 0.3V to 5V |

| V <sub>IN</sub> Relative to GND (ISL80111) (Note 9) | . V <sub>OUT</sub> + 0.2V to 5V |

| Nominal V <sub>OUT</sub> Range                      | 800mV to 3.3V                   |

| PG, ENABLE, SENSE/ADJ, SS Relative to GND           |                                 |

| V <sub>BIAS</sub> Relative to GND                   | 0V to 5.5V                      |

| V <sub>BIAS</sub> Relative to V <sub>OUT</sub>      | +0.8V minimum                   |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. Absolute maximum ratings define limits of safe operation. Extended operation at these conditions may compromise reliability. Exceeding these limits will result in damage. Recommended operating conditions define limits where specifications are guaranteed.

- 5. Absolute maximum voltage rating is defined as the voltage applied for a lifetime average duty cycle above 6V of 1%.

- 6. Electromigration specification defined as lifetime average junction temperature of +110 °C where maximum rated DC current = lifetime average current.

- 7. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 8. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 9. Minimum operating voltage applied to  $V_{IN}$  is 1V if  $V_{IN}$   $V_{DO}$  < 1V

Electrical Specifications Unless otherwise noted, all parameters are guaranteed over the conditions specified as follows:

$V_{IN} = V_{OUT} + 0.4V, V_{BIAS} = 2.9V, V_{OUT} = 1.2V, C_{BIAS} = 1\mu\text{F}, C_{IN} = 10\mu\text{F}, C_{OUT} = 2.2\mu\text{F}, T_J = +25\,^{\circ}\text{C}, I_L = 0\text{mA}. \text{ Applications must follow thermal guidelines of the package to determine worst-case junction temperature. Please refer to "Power Dissipation" on page 13 and Tech Brief <u>TB379</u>.$

Boldface limits apply over junction temperature (T<sub>j</sub>) range, -40°C to +125°C. Pulse load techniques used by ATE to ensure T<sub>j</sub> = T<sub>A</sub> where datasheet limits are defined.

| PARAMETER                         | SYMBOL                           | TEST CONDITIONS                                                                                                                                                                                                                 | MIN<br>(Note 10) | TYP  | MAX<br>(Note 10) | UNITS |

|-----------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------------------|-------|

| DC CHARACTERISTICS                |                                  |                                                                                                                                                                                                                                 |                  | ı    | '                |       |

| V <sub>BIAS</sub> UVLO            | UVLO_BIAS_r                      | V <sub>BIAS</sub> Rising                                                                                                                                                                                                        |                  | 2.3  | 2.9              | ٧     |

|                                   | UVLO_BIAS_f                      | V <sub>BIAS</sub> Falling                                                                                                                                                                                                       | 1.55             | 2.1  | 2.8              | ٧     |

| V <sub>BIAS</sub> UVLO Hysteresis | UVLO <sub>B_HYS</sub>            |                                                                                                                                                                                                                                 |                  | 0.2  |                  | ٧     |

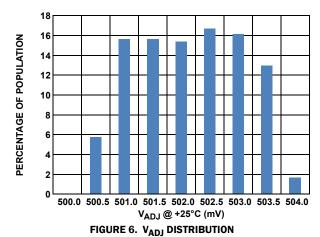

| DC ADJ Pin Voltage Accuracy       | V <sub>ADJ</sub>                 | $ \begin{aligned} \textbf{1.0V} &\leq \textbf{V}_{IN} \leq \textbf{3.6V}, \ \textbf{I}_{LOAD} = \textbf{0A}, \ \textbf{2.9V} \leq \textbf{V}_{BIAS} \leq \textbf{5.5V}, \\ \textbf{V}_{OUT} &= \textbf{V}_{ADJ} \end{aligned} $ | 494              | 502  | 510              | mV    |

| DC Input Line Regulation          | ΔV <sub>OUT</sub>                | $V_{OUT} + 0.4V \le V_{IN} \le 3.6V$                                                                                                                                                                                            |                  | 0.01 | 0.9              | m۷    |

| DC Bias Line Regulation           | $\Delta V_{OUT}$                 | 2.9V <v<sub>BIAS&lt;5.5V with respect to ADJ pin</v<sub>                                                                                                                                                                        |                  | 0.3  | 1.4              | m۷    |

| DC Output Load Regulation         | $\Delta V_{OUT}$                 | $0A \le I_{LOAD} \le 3A$                                                                                                                                                                                                        | -2               | -0.2 | 2                | m۷    |

| Feedback Input Current            |                                  | V <sub>ADJ</sub> = 0.5V                                                                                                                                                                                                         |                  | 10   | 80               | nA    |

| V <sub>IN</sub> Quiescent Current | I <sub>Q</sub> (V <sub>IN)</sub> | VOUT = 2.5V                                                                                                                                                                                                                     |                  | 8    | 10               | mA    |

| V <sub>IN</sub> Quiescent Current | I <sub>Q</sub> (V <sub>IN)</sub> | VOUT = 3.3,                                                                                                                                                                                                                     |                  | 10.6 |                  | mA    |

**Electrical Specifications** Unless otherwise noted, all parameters are guaranteed over the conditions specified as follows:

$V_{IN} = V_{OUT} + 0.4V$ ,  $V_{BIAS} = 2.9V$ ,  $V_{OUT} = 1.2V$ ,  $C_{BIAS} = 1\mu$ F,  $C_{IN} = 10\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{IN} = 10\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{IN} = 10\mu$ F,  $C_{OUT} = 1.2V$ ,  $C_{BIAS} = 10\mu$ F,  $C_{OUT} = 1.2V$ ,  $C_{BIAS} = 10\mu$ F,  $C_{OUT} = 1.2V$ ,  $C_{IN} = 10\mu$ F,  $C_{IN} =$

Boldface limits apply over Junction temperature (T<sub>J</sub>) range, -40 °C to +125 °C. Pulse load techniques used by ATE to ensure T<sub>J</sub> = T<sub>A</sub> where datasheet limits are defined. (Continued)

| PARAMETER                                    | SYMBOL                           | TEST CONDITIONS                                                                                                                 | MIN<br>(Note 10) | TYP | MAX<br>(Note 10) | UNITS                                   |

|----------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|-----------------------------------------|

| V <sub>IN</sub> Quiescent Current            | I <sub>Q</sub> (V <sub>IN)</sub> | VOUT = 1.0V                                                                                                                     |                  | 3.5 |                  | mA                                      |

| V <sub>BIAS</sub> Quiescent Current          | $I_Q(V_{BIAS})$                  | $0 \le I_L \le 3A, V_{BIAS} = 5.5V$                                                                                             |                  | 2.9 | 4.6              | mA                                      |

| Ground Pin Current in<br>Shutdown            | I <sub>SHDN</sub>                | ENABLE Pin = 0.2V, T <sub>J</sub> = +125°C                                                                                      |                  | 3   | 20               | μΑ                                      |

| V <sub>IN</sub> Dropout Voltage              | V <sub>DO(VIN)</sub>             | $I_{LOAD}$ = 1A, $V_{OUT}$ = 1.2V, 2.9V $\leq V_{BIAS} \leq 5V$                                                                 |                  | 27  | 90               | mV                                      |

| (Note 11)                                    |                                  | $I_{LOAD}$ = 2A, $V_{OUT}$ = 1.2V, 2.9V $\leq V_{BIAS} \leq 5V$                                                                 |                  | 53  | 115              | mV                                      |

|                                              |                                  | $I_{LOAD}$ = 3A, $V_{OUT}$ = 1.2V, 2.9V $\leq V_{BIAS} \leq 5V$                                                                 |                  | 75  | 140              | mV                                      |

| V <sub>BIAS</sub> Dropout Voltage            | V <sub>DO(BIAS)</sub>            | I <sub>LOAD</sub> = 1A, V <sub>OUT</sub> = 1.2V                                                                                 |                  | 1.1 | 1.3              | V                                       |

| (Note 11)                                    |                                  | I <sub>LOAD</sub> = 2A, V <sub>OUT</sub> = 1.2V                                                                                 |                  | 1.2 | 1.4              | V                                       |

|                                              |                                  | I <sub>LOAD</sub> = 3A, V <sub>OUT</sub> = 1.2V                                                                                 |                  | 1.3 | 1.5              | ٧                                       |

| OVERCURRENT PROTECTION                       |                                  |                                                                                                                                 |                  |     |                  |                                         |

| Output Short Circuit Current (3A Version)    | ISC                              | V <sub>OUT</sub> = 0.2V                                                                                                         |                  | 5.2 |                  | Α                                       |

| Output Short Circuit Current<br>(2A Version) |                                  | V <sub>OUT</sub> = 0.2V                                                                                                         |                  | 3.2 |                  | Α                                       |

| Output Short Circuit Current<br>(1A Version) |                                  | V <sub>OUT</sub> = 0.2V                                                                                                         |                  | 2.2 |                  | Α                                       |

| OVER-TEMPERATURE PROTE                       | CTION                            |                                                                                                                                 |                  |     |                  |                                         |

| Thermal Shutdown<br>Temperature              | TSD                              |                                                                                                                                 |                  | 160 |                  | °C                                      |

| Thermal Shutdown<br>Hysteresis               | TSDn                             |                                                                                                                                 |                  | 20  |                  | °C                                      |

| AC CHARACTERISTICS                           |                                  |                                                                                                                                 |                  |     |                  |                                         |

| Input Supply Ripple Rejection                | PSRR(V <sub>IN</sub> )           | f = 120Hz, I <sub>LOAD</sub> = 1A                                                                                               |                  | 80  |                  | dB                                      |

|                                              | PSRR(V <sub>BIAS</sub> )         | f = 120Hz, I <sub>LOAD</sub> = 1A                                                                                               |                  | 60  |                  | dB                                      |

| Output Noise Voltage                         | e <sub>N(RMS)</sub>              | $I_{LOAD}$ = 10mA, BW = 100Hz $\leq$ f $\leq$ 100kHz                                                                            |                  | 100 |                  | μV <sub>RMS</sub>                       |

| Spectral Noise Density                       | e <sub>N</sub>                   | I <sub>LOAD</sub> = 3A, f = 10Hz                                                                                                |                  | 7   |                  | μV/√Hz                                  |

|                                              |                                  | I <sub>LOAD</sub> = 3A, f = 100Hz                                                                                               |                  | 3   |                  | $\mu V_{/} \sqrt{Hz}$                   |

| DEVICE START-UP CHARACTER                    | ISTICS                           | ,                                                                                                                               | "                |     |                  |                                         |

| EN Start-up Time                             | t <sub>EN</sub>                  | C <sub>OUT</sub> = 10μF, I <sub>LOAD</sub> = 1A                                                                                 |                  | 50  |                  | μs                                      |

| BIAS Start-up Time                           | t <sub>BIAS</sub>                | C <sub>OUT</sub> = 10μF, EN = BIAS                                                                                              |                  | 100 |                  | μs                                      |

| ENABLE PIN CHARACTERIST                      | cs                               | ,                                                                                                                               | "                |     |                  |                                         |

| Turn-on Threshold (Rising)                   |                                  | $V_{OUT} + 0.4V \le V_{IN} \le 3.6V,  2.9V \le V_{BIAS} \le 5.5V$                                                               | 400              | 680 | 850              | m۷                                      |

| Hysteresis (Rising Threshold)                |                                  | $\textbf{1.2V} \leq \textbf{V}_{\mbox{IN}} \leq \textbf{3.6V},  \textbf{2.9V} \leq \textbf{V}_{\mbox{BIAS}} \leq \textbf{5.5V}$ | 60               | 260 | 330              | mV                                      |

| PG PIN CHARACTERISTICS                       |                                  | 1                                                                                                                               | <u> </u>         | 1   | 1                |                                         |

| PG Flag Falling Threshold                    | PG <sub>TH</sub>                 | 2.9V ≤ V <sub>BIAS</sub> ≤ 5.5V                                                                                                 | 71               | 82  | 93               | %Уоит                                   |

| 0 0                                          |                                  |                                                                                                                                 |                  |     |                  | • • • • • • • • • • • • • • • • • • • • |

**Electrical Specifications** Unless otherwise noted, all parameters are guaranteed over the conditions specified as follows:  $V_{IN} = V_{OUT} + 0.4V$ ,  $V_{BIAS} = 2.9V$ ,  $V_{OUT} = 1.2V$ ,  $C_{BIAS} = 1\mu$ F,  $C_{IN} = 10\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $T_{J} = +25^{\circ}$ C,  $I_{L} = 0$ mA. Applications must follow thermal guidelines of the package to determine worst-case junction temperature. Please refer to "Power Dissipation" on page 13 and Tech Brief <u>TB379</u>. **Boldface limits apply over junction temperature** ( $T_{J}$ ) range, -40°C to +125°C. Pulse load techniques used by ATE to ensure  $T_{J} = T_{A}$  where datasheet limits are defined. (**Continued**)

| PARAMETER               | SYMBOL | TEST CONDITIONS               | MIN<br>(Note 10) | TYP | MAX<br>(Note 10) | UNITS |

|-------------------------|--------|-------------------------------|------------------|-----|------------------|-------|

| PG Flag Low Voltage     |        | I <sub>SINK</sub> = 500μA     |                  | 90  | 130              | m۷    |

| PG Flag Leakage Current |        | PG = V <sub>BIAS</sub> = 5.5V |                  | 11  | 300              | nA    |

| PG Flag Sink Current    |        |                               | 7                | 10  |                  | mA    |

#### NOTES:

- 10. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 11. Dropout is defined by the difference in supply (V<sub>IN</sub>, V<sub>BIAS</sub>) and V<sub>OUT</sub> when the supply produces a 2% drop in V<sub>OUT</sub> from its nominal value, output voltage set to 2.5V.

- 12. For normal operation, V<sub>IN</sub> must always be less than or equal to the voltage applied to V<sub>BIAS</sub>. Part is protected against fault conditions where V<sub>IN</sub> can be greater than V<sub>BIAS</sub>.

FN7841.1

June 18, 2012

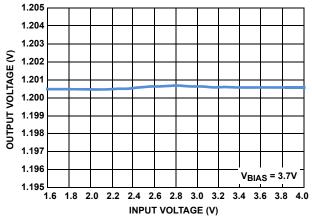

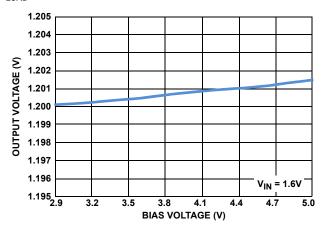

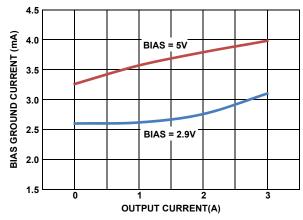

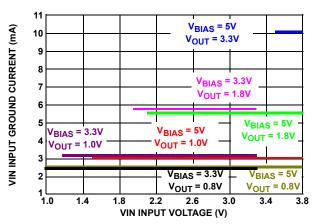

**Typical Operating Performance** Unless otherwise noted,  $V_{IN}$  = 1.8V,  $V_{BIAS}$  = 3.3V,  $V_{OUT}$  = 1.2V,  $C_{IN}$  =  $C_{OUT}$  = 10 $\mu$ F,  $T_J$  = +25°C,  $I_{LOAD}$  = 0A.

TEMPERATURE (°C)

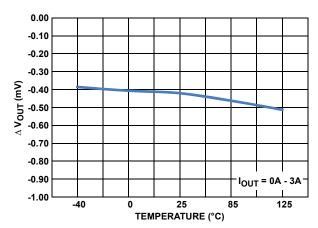

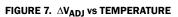

FIGURE 8. LOAD REGULATION vs TEMPERATURE

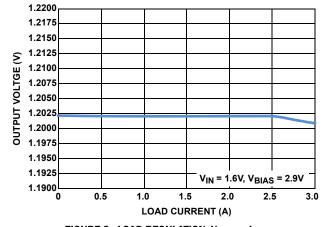

FIGURE 9. LOAD REGULATION,  $V_{OUT}$  vs  $I_{OUT}$

FIGURE 10. V<sub>IN</sub> LINE REGULATION

**Typical Operating Performance** Unless otherwise noted,  $V_{IN}$  = 1.8V,  $V_{BIAS}$  = 3.3V,  $V_{OUT}$  = 1.2V,  $C_{IN}$  =  $C_{OUT}$  = 10 $\mu$ F,  $T_J$  = +25°C,  $I_{LOAD}$  = 0A. (Continued)

FIGURE 11. VBIAS LINE REGULATION

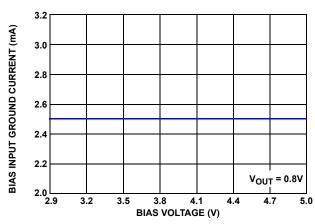

FIGURE 12. BIAS GROUND CURRENT vs LOAD CURRENT

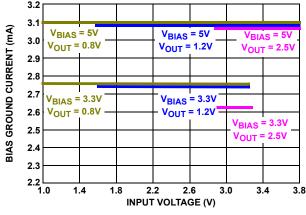

FIGURE 13. INPUT GROUND CURRENT vs V<sub>IN</sub> & V<sub>OUT</sub>

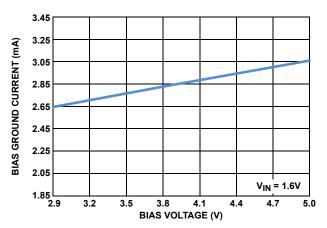

FIGURE 14. INPUT GROUND CURRENT vs VBIAS

FIGURE 15. BIAS GROUND CURRENT vs  $V_{\text{IN}}$  &  $V_{\text{OUT}}$

FIGURE 16. BIAS GROUND CURRENT vs VBIAS

**Typical Operating Performance** Unless otherwise noted,  $V_{IN} = 1.8V$ ,  $V_{BIAS} = 3.3V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = C_{OUT} = 10\mu F$ ,  $T_J = +25^{\circ}C$ ,  $I_{LOAD} = 0A$ . (Continued)

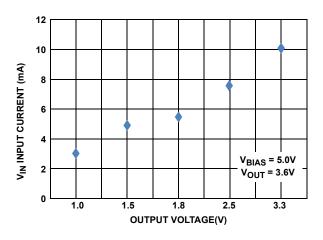

FIGURE 17.  $V_{IN} I_{O}$  vs VOUT VOLTAGE

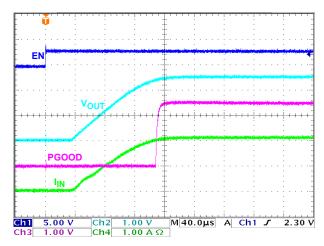

FIGURE 18. ENABLE START-UP WITH PGOOD

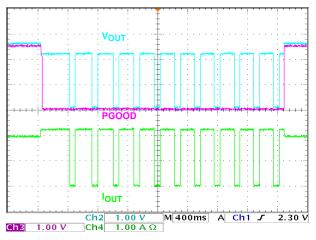

FIGURE 19. ISL8011X INTO AND OUT OF THERMAL SHUTDOWN

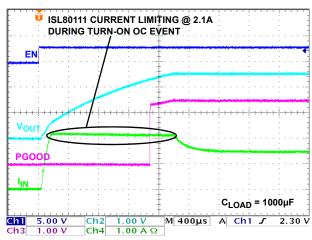

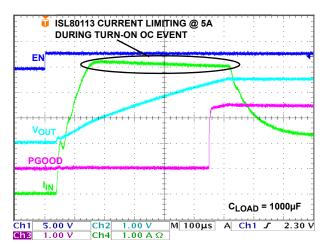

FIGURE 20. ISL80111 ENABLED INTO OVERCURRENT

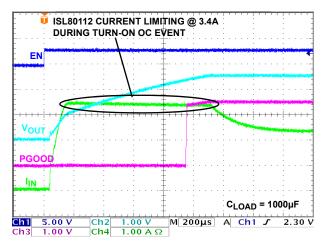

FIGURE 21. ISL80112 ENABLED INTO OVERCURRENT

FIGURE 22. ISL80113 ENABLED INTO OVERCURRENT

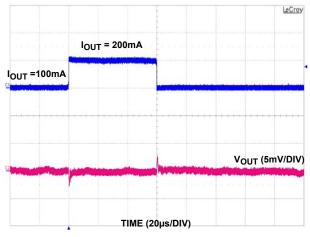

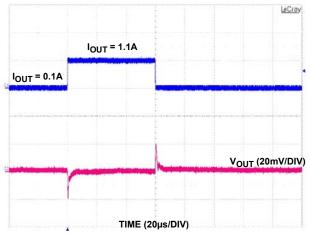

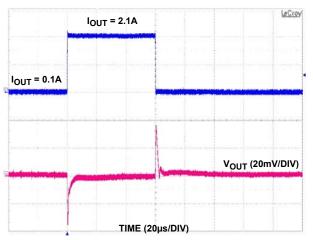

## **Typical Operating Performance** Unless otherwise noted, $V_{IN}$ = 1.8V, $V_{BIAS}$ = 3.3V, $V_{OUT}$ = 1.2V, $C_{IN}$ = $C_{OUT}$ = 10 $\mu$ F, $T_J$ = +25°C, $I_{LOAD}$ = 0A. (Continued)

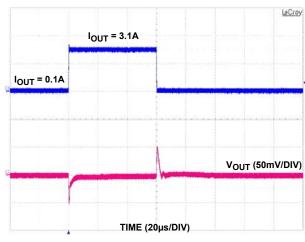

FIGURE 23. 100mA LOAD TRANSIENT RESPONSE

FIGURE 24. 1A LOAD TRANSIENT RESPONSE

FIGURE 25. 2A LOAD TRANSIENT RESPONSE

FIGURE 26. 3A LOAD TRANSIENT RESPONSE

FIGURE 27. VIN PSRR vs LOAD CURRENT

FIGURE 28. BIAS PSRR vs LOAD CURRENT

## **Typical Operating Performance** Unless otherwise noted, $V_{IN}$ = 1.8V, $V_{BIAS}$ = 3.3V, $V_{OUT}$ = 1.2V, $C_{IN}$ = $C_{OUT}$ = 10 $\mu$ F, $T_J$ = +25°C, $I_{LOAD}$ = 0A. (Continued)

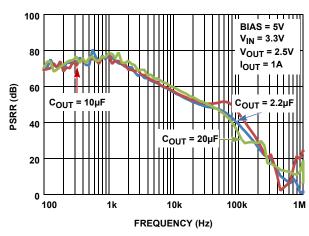

FIGURE 29. V<sub>VIN</sub> PSRR vs LOAD CURRENT

FIGURE 30. VBIAS PSRR vs LOAD CURRENT

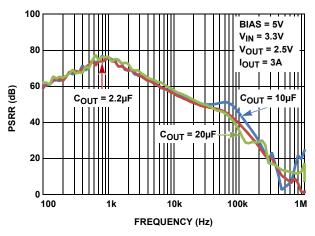

FIGURE 31. VIN PSRR vs COUT

FIGURE 32.  $V_{IN}$  PSRR vs  $C_{OUT}$

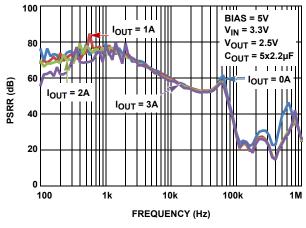

FIGURE 33. V<sub>IN</sub> PSRR vs LOAD CURRENT

FIGURE 34. V<sub>BIAS</sub> PSRR vs LOAD CURRENT

**Typical Operating Performance** Unless otherwise noted,  $V_{IN} = 1.8V$ ,  $V_{BIAS} = 3.3V$ ,  $V_{OUT} = 1.2V$ ,  $C_{IN} = C_{OUT} = 10\mu F$ ,  $T_J = +25^{\circ}C$ ,  $I_{LOAD} = 0A$ . (Continued)

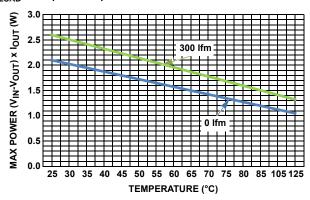

FIGURE 35. CONTINUOUS POWER LIMIT vs AIR TEMP AND FLOW

FIGURE 36. INPUT VOLTAGE NOISE vs BIAS VOLTAGE

## **Functional Description**

The ISL80111, ISL80112 and ISL80113 are high-performance, low-dropout regulators featuring an NMOS pass device. Benefits of using an NMOS as a pass device include low input voltage, stability over a wide range of output capacitors, and ultra low dropout voltage. The ISL80111, ISL80112 and ISL80113 are ideal for post regulation of switch mode power supplies.

The ISL80111, ISL80112 and ISL80113 also integrate enable, power-good indicator, current limit protection, and thermal shutdown functions into a space-saving 3x3 DFN package.

#### **Input Voltage Requirements**

The VIN pin provides the high current to the drain of the NMOS pass transistor. The specified minimum input voltage is 1V and dropout voltage for this family of LDOs has been conservatively specified.

#### **Bias Voltage Requirements**

The  $V_{BIAS}$  input powers the internal control circuits, reference voltage, and LDO gate driver. The difference between the  $V_{BIAS}$  voltage and the output voltage must be greater than the  $V_{BIAS}$  dropout voltage specified in the "Electrical Specifications" table beginning on page 4. The minimum  $V_{BIAS}$  input is 2.9V.

#### **Enable Operation**

The ENABLE turn-on threshold is typically 600mV with a hysteresis of 100mV. This pin must not be left floating. When this pin is not used, it must be tied to  $V_{BIAS}.$  A  $1 k\Omega$  to  $10 k\Omega$  pull-up resistor is required for applications that use open collector or open drain outputs to control the ENABLE pin.

#### **Soft-start Operation**

The ISL8011x has an internal 100µs typical soft-start function to prevent excessive in-rush current during start-up.

#### **Power-good Operation**

The PGOOD flag is an open-drain NMOS that can sink up to 10mA during a fault condition. Applications not using this feature must connect this pin to ground. The PGOOD pin requires an external pull-up resistor, which is typically connected to the  $V_{OUT}$  pin. The

PGOOD pin should not be pulled up to a voltage source greater than  $V_{BIAS}$ . A PGOOD fault can be caused by the output voltage going below 84% of the nominal output voltage. PGOOD does not function during thermal shutdown as the  $V_{OUT}$  is less than the minimum regulation voltage during that time.

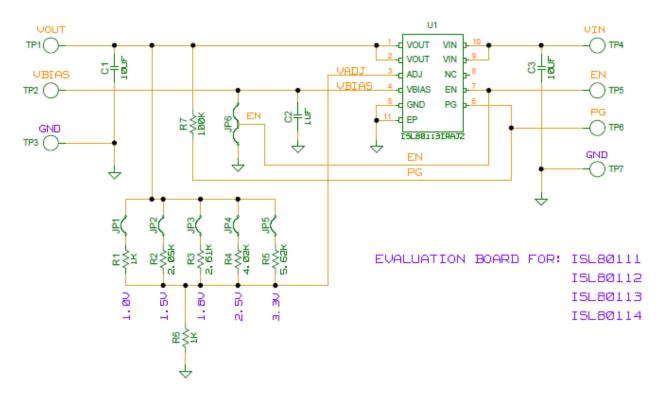

#### **Output Voltage Selection**

An external resistor divider is used to scale the output voltage relative to the internal reference voltage. This voltage is then fed back to the error amplifier. The output voltage can be programmed to any level between 0.8V and 4V. Referring to Figure 1 the external resistor divider,  $R_3$  and  $R_4$ , is used to set the output voltage as shown in Equation 1. The recommended value for  $R_4$  is  $500\Omega$  to  $1k\Omega$ .  $R_3$  is then chosen according to Equation 2.

$$V_{OUT} = 0.5 V \times \left(\frac{R_3}{R_4} + 1\right)$$

(EQ. 1)

$$R_3 = R_4 \times \left(\frac{V_{OUT}}{0.5V} - 1\right)$$

(EQ. 2)

#### **Current Limit Protection**

The ISL80111, ISL80112, and ISL80113 incorporate protection against overcurrent due to a short, overload condition applied to the output and the in-rush current that occurs at start-up. The LDO performs as a constant current source when the output current exceeds the current limit threshold noted in "Electrical Specifications" on page 4. If the short or overload condition is removed from V<sub>OUT</sub>, then the output returns to normal voltage mode regulation. In the event of an overload condition, the LDO might begin to cycle on and off due to the die temperature exceeding the thermal fault condition.

#### **Thermal Fault Protection**

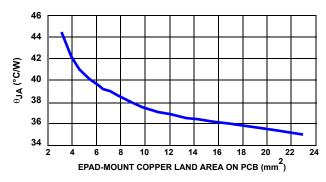

If the die temperature exceeds (typically)  $+160\,^{\circ}$  C, the LDO output shuts down until the die temperature cools to (typically)  $+140\,^{\circ}$  C. The level of power, combined with the thermal impedance of the package ( $+48\,^{\circ}$  C/W), determines whether the junction temperature exceeds the thermal shutdown temperature.

See Figure 35 for maximum continuous power dissipation guidance for ambient temperature and linear air flow rate. This graph ignores the insignificant power dissipation contribution of the BIAS pin.

## External Capacitor Requirements

External capacitors are required for proper operation. To ensure optimal performance, careful attention must be paid to the layout guidelines and selection of capacitor type and value.

#### **Input Capacitor**

The minimum input capacitor required for proper operation is  $10\mu F$  with a ceramic dielectric. This minimum capacitor must be connected to the  $V_{IN}$  and ground pins of the LDO no further than 0.5cm away.

#### **Output Capacitor**

The ISL8011x applies state-of-the-art internal compensation to simplify selection of the output capacitor. Stable operation over the full temperature range,  $V_{\text{IN}}$  range,  $V_{\text{OUT}}$  range, and load extremes is guaranteed for all capacitor types and values, assuming a 1µF X5R/X7R is used for local bypass on  $V_{\text{OUT}}$ . This minimum capacitor must be connected to the  $V_{\text{OUT}}$  and ground pins of the LDO no further than 0.5cm away.

Lower-cost Y5V and Z5U type ceramic capacitors are acceptable, if the size of the capacitor is larger, to compensate for the significantly lower tolerance over X5R/X7R types. Additional capacitors of any value, in ceramic, POSCAP, or alum/tantalum electrolytic types, can be placed in parallel to improve PSRR at higher frequencies or load-transient AC output voltage tolerances.

#### **Bias Capacitor**

The minimum input capacitor required for proper operation is  $1\mu F$  with a ceramic dielectric. This minimum capacitor must be connected to the  $V_{BIAS}$  and ground pins of the LDO no further than 0.5cm away. When the VBIAS pin is connected to the  $V_{IN}$  pin, a total of  $10\mu F$  of X5R/X7R connected to the  $V_{IN}$  pin and ground is sufficient.

## **Power Dissipation and Thermals**

#### **Power Dissipation**

Junction temperature must not exceed the range specified in the "Recommended Operating Conditions" section on page 4. Power dissipation can be calculated with Equation 3.

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{BIAS} \times IQ(BIAS) + V_{IN} \times IQ(V_{IN})$$

(Eq. 3)

The maximum allowable junction temperature,  $T_{J(MAX)}$ , and the maximum expected ambient temperature,  $T_{A(MAX)}$ , determine the maximum allowable power dissipation, as shown in Equation 4, where  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

$$P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$$

(EQ. 4)

FIGURE 37. 3mmx3mm-10 PIN DFN ON 4-LAYER PCB WITH THERMAL VIAS  $\theta_{JA}$  vs EPAD-MOUNT COPPER LAND AREA ON PCB

For safe operation, ensure that power dissipation calculated in Equation 3 ( $P_D$ ) is less than the maximum allowable power dissipation,  $P_{D(MAX)}$ .

The DFN package uses the copper area on the PCB as a heat sink. For heat sinking, the EPAD of this package must be soldered to the copper plane (GND plane). Figure 37 shows a curve for the  $\theta_{JA}$  of the DFN package for different copper area sizes

#### **General PowerPAD Design Considerations**

The following is an example of how to use vias to remove heat from the IC.

Filling the thermal pad area with vias is recommended. A typical via array is to fill the thermal pad footprint with vias spaced such that they are center on center 3x the radius apart from each other. Keep the vias small but not so small that their inside diameter prevents solder from wicking through the holes during reflow.

FIGURE 38. PCB VIA PATTERN

Connect all vias to the round plane. For efficient heat transfer, it is important that the vias have low thermal resistance. Do not use "thermal relief" patterns to connect the vias. It is important to have a complete connection of the plated through-hole to each plane.

## ISL80111, ISL80112, ISL80113 Split Supply LDO Evaluation Board User Guide

## **Description**

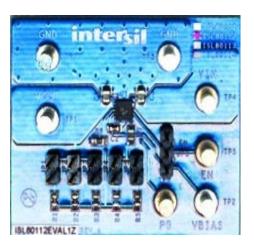

The ISL8011XEVAL1Z provides a simple platform to evaluate performance of the ISL8011X family of split supply LDOs. Jumpers are provided to easily set popular output voltages.

The ISL80111, ISL80112, and ISL80113 are single-output LDOs specified for 1A, 2A, 3A of output current and are optimized for less than 2.5V and less output voltage conversions. The ISL8011X supports  $V_{IN}$  voltages down to 1V, provided a standard legacy 3.3V or 5V is applied on the  $V_{BIAS}$  pin. The output voltage is adjustable from 0.8V to 3.3V.

An enable input, having a threshold < 1V, allows the part to be placed into a low quiescent current shutdown mode. A submicron CMOS process is utilized for this product family to deliver best-in-class analog performance and overall value for applications in need of input voltage conversions to typically below 2.5V. It also has the superior load transient regulation unique to a NMOS power stage.

These LDOs consume significantly lower quiescent current as a function of load compared to bipolar LDOs. This lower consumption translates into higher efficiency and the ability to consider packages with smaller footprints. The quiescent current has been modestly compromised in design to enable leading class fast load transient response and load regulation.

#### What's Inside

- . The evaluation kit contains the following:

- The ISL80113EVAL1Z with the appropriate parts installed

- The ISL80111, ISL80112, ISL80113 data sheet

### **Test Steps**

- Select the desired output voltage by shorting one of the jumpers from JP2 through JP5.

- Connect both the BIAS and VIN supplies and the load. Enable the IC using jumper JP6 (bottom position) or via a signal on the center post, observe the output.

- 3. The shipped configuration is enabled and  $V_{OUT}$  = 3.3V.

- 4. Scope shots taken from ISL8011XEVAL1Z boards.

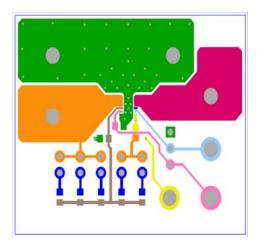

FIGURE 39. ISL80113EVAL1Z (TOP PCB LEFT, PHOTOGRAPH RIGHT)

## **Schematic**

## **Bill of Materials**

| REFERENCE<br>DESIGNATOR         | VALUE                | DESCRIPTION                                                     | MANUFACTURER | PART<br>NUMBER                                    |

|---------------------------------|----------------------|-----------------------------------------------------------------|--------------|---------------------------------------------------|

| U1                              |                      | ISL80111, ISL80112 or ISL80113 as noted on the evaluation board | Intersil     | ISL80111IRAJZ,<br>ISL80112IRAJZ,<br>ISL80113IRAJZ |

| C1, C3                          | <b>1</b> 0μ <b>F</b> | CAP, SMD, 0805, 50V, 10%                                        | Generic      |                                                   |

| C2                              | 1µF                  | CAP, SMD, 0603                                                  | Generic      |                                                   |

| R1                              | 1kΩ                  | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| R2                              | 2.05kΩ               | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| R3                              | 2.61kΩ               | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| R4                              | 4.02kΩ               | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| R5                              | 5.62kΩ               | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| R6                              | 1kΩ                  | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| R7                              | <b>100</b> kΩ        | RES, SMD, 0603, 1%                                              | Generic      |                                                   |

| JP1, JP2, JP3,<br>JP4, JP5, JP6 |                      | Jumper                                                          | Generic      |                                                   |

| TP1, TP2, TP3<br>TP4, TP5, TP6  |                      | Terminal Connector                                              | Generic      |                                                   |

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE          | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 5, 2012  | FN7841.1 | Ordering Information table on page 3: Changed evaluation board names from: ISL80111IRAJEVALZ, ISL80112IRAJEVALZ and ISL80113IRAJEVALZ to ISL80111EVAL1Z, ISL80112EVAL1Z and ISL80113VAL1Z                                                                                                                                                                                                                                |

|               |          | Changed POD L10.3x3 on page 17 to latest revision from Rev 6 to Rev 7. Change to POD is as follows: Removed package outline and included center to center distance between lands on recommended land pattern. Removed Note 4 "Dimension b applies to the metallized terminal and is measured between 0.18mm and 0.30mm from the terminal tip." since it is not applicable to this package. Renumbered notes accordingly. |

|               |          | Figure 6 VADJ Distribution , corrected "Y" scale units from (0.18, 0.16, 0.14, 0.12, 0.10, 0.08, 0.06, 0.04, 0.02, and 0.00) to (18, 16,14,12,10, 8, 6, 4, 2, and 0)                                                                                                                                                                                                                                                     |

|               |          | Electrical Specifications table on page 4 "Added UVLO rising spec to show max of 2.9V so implementation at 3.3V is not a math problem".                                                                                                                                                                                                                                                                                  |

| March 30 2012 | FN7841.0 | Initial Release and Added "UVLO _BIAS _r" spec on pg 4. Modified Figures 13 - 17                                                                                                                                                                                                                                                                                                                                         |

#### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: ISL80111, ISL80112, ISL80113.

To report errors or suggestions for this data sheet, please go to: www.intersil.com/askourstaff

FITs are available from our website at: http://rel.intersil.com/reports/search.php

16

intersil

For additional products, see <a href="www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

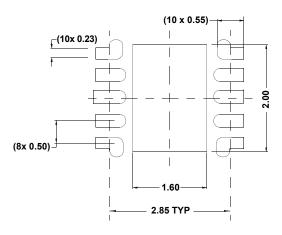

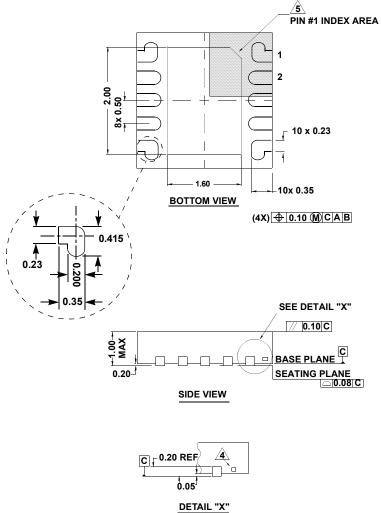

## **Package Outline Drawing**

L10.3x3

10 LEAD DUAL FLAT PACKAGE (DFN)

Rev 7, 10/11

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm$  0.05

- 4. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.