Data Sheet

#### February 27, 2009

FN6742.0

## Filterless High Efficiency 1.5W Class D Mono Amplifier

intercil

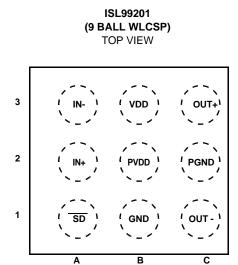

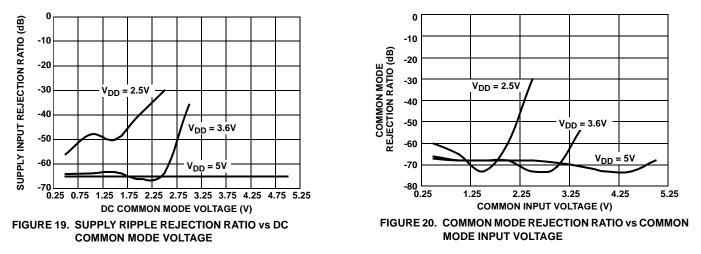

The ISL99201 is a fully integrated high efficiency class-D mono amplifier. It is designed to maximize performance for mobile phone applications. The application circuit requires a minimum requirement of external components and operates from a 2.4V to 5.5V input supply. It is capable of delivering 1.4W of continuous output power with less than 1% THD+N driving a 8 $\Omega$  load from a 5V supply.

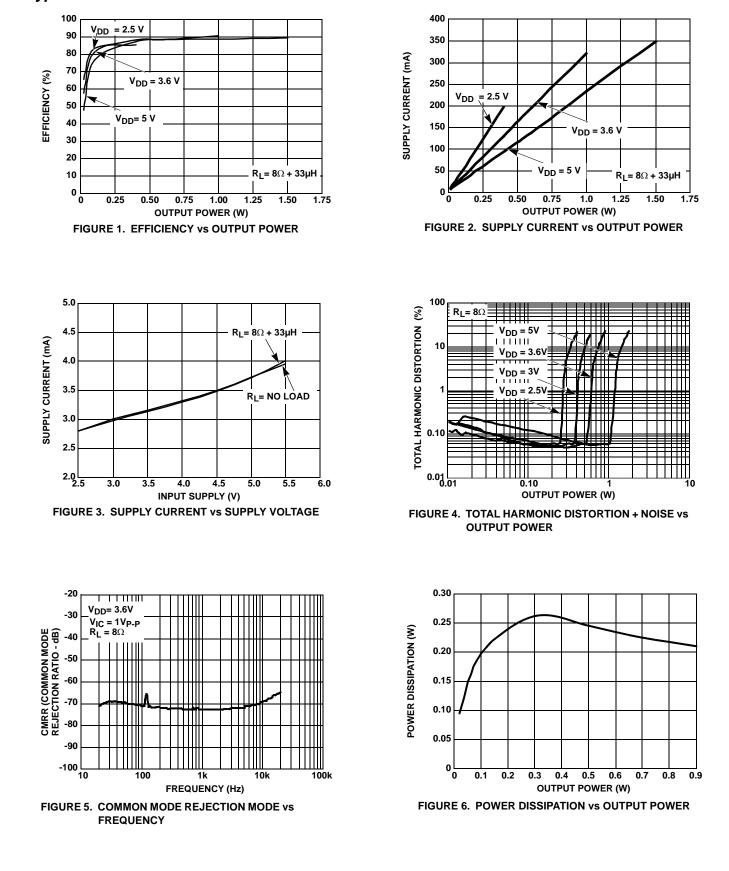

The ISL99201 features a high-efficiency, low-noise modulation scheme. It operates with 86% efficiency at 400mW into 8 $\Omega$  and has a signal-to-noise ratio (SNR) that is better than 95dB. The ISL99201 has a micro-power shutdown mode with a typical shutdown current of 200nA. Shutdown is enabled by applying a logic low to the  $\overline{\text{SD}}$  pin.

The architecture of the devices allows it to achieve very low level of pop-and-click. This minimizes voltage glitches at the output during turn-on and turn-off, thus reducing audible noise on activation and deactivation.

The fully differential input of the ISL99201 provides excellent rejection of common mode noise on the input typically 75dB. EMI suppression is achieved by SRC (Slew Rate Control).

The ISL99201 oscillator can be synchronized to an external clock through the SYNC input, allowing the switching frequency to be externally defined. The SYNC input also allows multiple ISL99201 to be cascaded and frequency locked; minimizing interference due to clock intermodulation. SYNC is available only in DFN version.

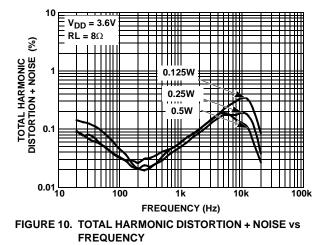

The ISL99201 also has excellent rejection of power supply noise, including noise caused by GSM transmission bursts and RF rectification. PSRR is typically 75dB at 217Hz. There will be 4 versions of the part; they will consist of three fixed gain settings (6dB, 9.6dB, 12dB) and one user programmable gain setting (need external resistors).

The ISL99201 has built-in thermal shutdown and output short-circuit protection.

#### Features

- Filterless Class D with Efficiency > 86% at 400mW

- Click-Pop Suppression

- Slew Rate Control

- Spread Spectrum Switching

- Optional SYNC Pin for Master/Slave Operation Without Interface (Only in TDFN)

- 1.4W into  $8\Omega$  with Less than 1% THD+N

- 2.4V to 5.5V Single Supply Voltage

- · Built-in Resistors to Reduce Board Component Count

- Only One External Component Required (Fixed Gain Mode)

- Short Circuit and Thermal Protection

- Gain Programmable 6dB, 9.6dB, 12dB and User Programmable

- Pb-Free (RoHS compliant)

#### Applications

- Mobile Phones

- MP3 Players

- Portable Gaming

- Portable Electronics

- Educational Toys

1

### **Ordering Information**

| PART NUMBER                     | PART MARKING | GAIN SETTING<br>(dB) | TEMP. RANGE<br>(°C) | PACKAGE<br>Tape & Reel<br>(Pb-Free) | PKG. DWG. # |

|---------------------------------|--------------|----------------------|---------------------|-------------------------------------|-------------|

| ISL99201IRTAZ-T (Notes 1, 2)    | 201A         | 6                    | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTAZ-TK (Notes 1, 2)   | 201A         | 6                    | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTBZ-T (Notes 1, 2)    | 201B         | 9.6                  | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTBZ-TK (Notes 1, 2)   | 201B         | 9.6                  | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTCZ-T (Notes 1, 2)    | 201C         | 12                   | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTCZ-TK (Notes 1, 2)   | 201C         | 12                   | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTDZ-T (Notes 1, 2)    | 201D         | Prog.                | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IRTDZ-TK (Notes 1, 2)   | 201D         | Prog.                | -40 to +85          | 8 Ld 3x3 TDFN                       | L8.3x3A     |

| ISL99201IIAZ-T (Notes 1, 3, 4)  | 201A         | 6                    | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IIAZ-TK (Notes 1, 3, 4) | 201A         | 6                    | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IIBZ-T (Notes 1, 3, 4)  | 201B         | 9.6                  | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IIBZ-TK (Notes 1, 3, 4) | 201B         | 9.6                  | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IICZ-T (Notes 1, 3, 4)  | 201C         | 12                   | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IICZ-TK (Notes 1, 3, 4) | 201C         | 12                   | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IIDZ-T (Notes 1, 3, 4)  | 201D         | Prog.                | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

| ISL99201IIDZ-TK (Notes 1, 3, 4) | 201D         | Prog.                | -40 to +85          | 9 Ball WLCSP                        | W3x3.9C     |

#### NOTES:

1. Please refer to TB347 for details on reel specifications.

These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. These Intersil Pb-free WLCSP and BGA packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free WLCSP and BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

4. Please contact factory for ordering details.

#### Absolute Maximum Ratings (Reference to GND)

| Supply Voltage | -0.3                     | ′ to 6V |

|----------------|--------------------------|---------|

| Input Voltage  | -0.3V to V <sub>DD</sub> | +0.3V   |

#### **Recommended Operating Conditions**

| Ambient Temperature Range                      | 40°C to +85°C |

|------------------------------------------------|---------------|

| Operating Supply Voltage (V <sub>DD</sub> Pin) | 2.4V to 5.5V  |

#### **Thermal Information**

| Thermal Resistance (Typical Note 5)                 | θ <sub>JA</sub> (°C/W) |

|-----------------------------------------------------|------------------------|

| WLCSP Package                                       | 102                    |

| TDFN Package                                        | 53                     |

| Maximum Junction Temperature (Plastic Package) -65° | °C to +150°C           |

| Maximum Storage Temperature Range65°                | °C to +150°C           |

| Power Dissipation Ratings                           |                        |

| 8 Ld 3x3 TDFN                                       |                        |

| Derating Factor                                     | .21.8mW/°C             |

| Power Ratings                                       |                        |

| T <sub>A</sub> = +25°C                              | 2.7W                   |

| T <sub>A</sub> = +70°C                              | 1.7W                   |

| T <sub>A</sub> = +85°C                              | 1.4W                   |

| 9 Ball WLCSP                                        |                        |

| Derating Factor                                     | 7.5mW/°C               |

| Power Ratings                                       |                        |

| T <sub>A</sub> = +25°C                              |                        |

| T <sub>A</sub> = +70°C                              | 0.67W                  |

| $T_A = +85^{\circ}C$                                | 0.56W                  |

| Pb-Free Reflow Profile                              | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp    |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTE:

**Electrical Specifications**

5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

----

. . . .

× 11 · ·

Typical Values Are Tested at V<sub>DD</sub> = 5V and the Ambient Temperature at +25°C. Parameters with MIN and/or

| PARAMETER                          | SYMBOL              | TEST CONDITIONS                                                               | MIN | TYP  | MAX | UNITS |

|------------------------------------|---------------------|-------------------------------------------------------------------------------|-----|------|-----|-------|

| Output Power                       | Po                  | $R_L$ = 8 $\Omega$ , THD = 10%, f = 1kHz, 20kHz BW, $V_{DD}$ = 5.0V           |     | 1.4  |     | W     |

|                                    |                     | $R_L$ = 8 $\Omega$ , THD = 10%, f = 1kHz, 20kHz BW, $V_{DD}$ = 3.6V           |     | 0.75 |     | W     |

|                                    |                     | R <sub>L</sub> = 8Ω, THD = 10%, f = 1kHz, 20kHz BW, V <sub>DD</sub> = 2.5V    |     | 0.4  |     | W     |

|                                    |                     | $R_L$ = 8Ω, THD = 1%, f = 1kHz, 20kHz BW, $V_{DD}$ = 5.0V                     |     | 1.15 |     | W     |

| Efficiency                         | η                   | $P_{OUT} = 1.4W, 8\Omega + 33\mu H, V_{DD} = 5.0V$                            |     | 90   |     | %     |

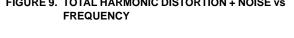

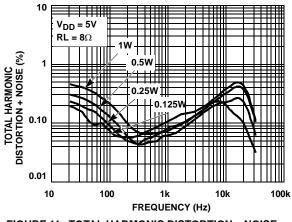

| Total Harmonic Distortion + Ratio  | THD+N               | $P_O = 1W$ into $8\Omega$ each channel, f = 1kHz, $V_{DD} = 5.0V$             |     | 0.05 |     | %     |

|                                    |                     | $P_O = 0.5W$ into $8\Omega$ each channel, f = 1kHz, $V_{DD} = 3.6V$           |     | 0.05 |     | %     |

|                                    |                     | $P_{O}$ = 0.2W into 8 $\Omega$ each channel, f = 1kHz, V <sub>DD</sub> = 3.6V |     | 0.09 |     | %     |

| Common-Mode Rejection Ratio        | CMRR                | $V_{IC}$ = 0.5V to (V_{DD} - 0.8V); R_L= 8\Omega, V_{DD} = 2.5V to 5.5V       |     | -60  |     | dB    |

|                                    | CMRR <sub>GSM</sub> | $V_{CM} = 2.5V \pm 1V_{P-P}$ at 217Hz, R <sub>L</sub> = 8 $\Omega$            |     | -60  |     | dB    |

| Average Switching Frequency        | f <sub>sw</sub>     | V <sub>DD</sub> = 5V                                                          | 300 | 375  | 450 | kHz   |

| Differential Output Offset Voltage | V <sub>OOS</sub>    | G = 6dB; 9.6dB; 12dB; 28dB.                                                   |     | 0.2  | 5.0 | mV    |

| POWER SUPPLY                       |                     |                                                                               |     |      |     |       |

| Supply Voltage Range               | V <sub>DD</sub>     |                                                                               | 2.4 |      | 5.5 | V     |

| Power Supply Rejection Ratio       | PSRR                | V <sub>DD</sub> = 2.5V to 5.0V                                                |     | -65  |     | dB    |

|                                    | PSRR <sub>GSM</sub> | $V_{RIPPLT} = 100mV_{RMS}$ at 217Hz (Input AC-Coupled with 2µF capacitor)     |     | -65  |     | dB    |

### Electrical Specifications

Typical Values Are Tested at V<sub>DD</sub> = 5V and the Ambient Temperature at +25°C. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued)

| PARAMETER                    | SYMBOL                  | TEST CONDITIONS                                                                                  | MIN  | TYP   | MAX  | UNITS |

|------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Supply Current               | I <sub>IN</sub>         | $V_{IN} = 0V$ , No load, $V_{DD} = 5V$                                                           |      | 3.9   |      | mA    |

|                              |                         | $V_{IN} = 0V$ , No load, $V_{DD} = 3.6V$                                                         |      | 3.2   | 3.75 | mA    |

|                              |                         | $V_{IN} = 0V, 8\Omega + 33\mu H, V_{DD} = 5V$                                                    |      | 3.9   |      | mA    |

|                              |                         | $V_{\text{IN}} = 0\text{V}, 8\Omega + 33\mu\text{H}, \text{V}_{\text{DD}} = 3.6\text{V}$         |      | 3.8   |      | mA    |

|                              | I <u>SD</u><br>(Note 6) | SD = GND                                                                                         |      | 0.2   | 0.4  | μA    |

| GAIN CONTROL                 |                         |                                                                                                  |      |       |      |       |

| Closed-Loop Gain             |                         | D version user program<br>( Max Gain, Ri = 0Ω)                                                   | 27.5 | 28.5  | 29.5 | dB    |

|                              |                         | A version                                                                                        | 5.7  | 6     | 6.3  | dB    |

|                              |                         | B version                                                                                        | 9.2  | 9.6   | 10   | dB    |

|                              |                         | C version                                                                                        | 11.5 | 12    | 12.5 | dB    |

| Differential Input Impedance | Z <sub>IN</sub>         | $\overline{SD} = V_{DD}$ , A version                                                             |      | 70    |      | kΩ    |

|                              |                         | $\overline{SD} = V_{DD}$ , B version                                                             |      | 46.25 |      | kΩ    |

|                              |                         | $\overline{SD} = V_{DD}$ , C version                                                             |      | 35    |      | kΩ    |

|                              |                         | $\overline{SD} = V_{DD}$ , D version, Ri = 2.5k $\Omega$                                         |      | 7.5   |      | kΩ    |

|                              |                         | SD = GND                                                                                         |      | 100   |      | kΩ    |

| SHUTDOWN CONTROL             |                         |                                                                                                  |      |       | 1    | L     |

| Input Voltage High           | VIH                     |                                                                                                  |      | 1.2   |      | V     |

| Input Voltage Low            | VIL                     |                                                                                                  |      | 0.5   |      | V     |

| Turn-on Time                 | t <sub>WU</sub>         | $\overline{\text{SD}}$ rising edge from GND to V <sub>DD</sub>                                   |      | 3.5   |      | ms    |

| Turn-off Time                | t <sub>SD</sub>         | SD falling edge from V <sub>DD</sub> to GND                                                      |      | 5     |      | μs    |

| Output Impedance             | Z <sub>OUT</sub>        | SD = GND                                                                                         |      | >100  |      | kΩ    |

| NOISE PERFORMANCE            | 1                       |                                                                                                  | 1    | 1     | 1    | 1     |

| Output Voltage Noise         | En                      | $V_{DD}$ = 3.6V, f = 20Hz to 20kHz, inputs are AC grounded, $A_V$ = 6dB, A-weighting             |      | 27    |      | μV    |

|                              |                         | $V_{DD}$ = 3.6V, f = 20Hz to 20kHz, inputs are AC grounded, A <sub>V 0</sub> = 6dB, no weighting |      | 35    |      | μV    |

| Signal-to-Noise Ratio        | SNR                     | P <sub>OUT</sub> = 1W, R <sub>L</sub> = 8Ω                                                       |      | 102   |      | dB    |

NOTE:

6. Limits established by Characterization and are not production tested

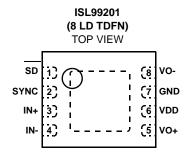

## **Pin Descriptions**

## SD

Shutdown Active Low. This signal is used to shut down and activate the part. It is 1.8V to 5V compatible. During shutdown, the part draws less than 100nA input current. Coming out of shutdown takes 3.5ms and going into shutdown is instantaneous.

## SYNC

External clock input (available only in DFN). This pin allows the chip to be synchronized to a system clock. This helps in folding the spectral components and the switching harmonic out of band of interest. The range of SYNC frequency is from 250kHz to 800kHz.

### IN+

Positive Differential Input.

#### IN-

Negative Differential Input.

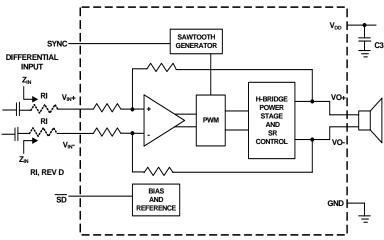

## Block Diagram (Notes \*)

V<sub>O</sub>+

Positive BTL output.

#### GND

Ground (Analog ground in CSP)

### V<sub>DD</sub>

Power Supply (Analog VDD in CSP)

# V<sub>O</sub>-

Negative BTL output

## PVDD

Power Supply (CSP only)

## PGND

Power Ground (CSP only)

Notes:

Gain = 6dB, 9.6dB, 12dB (gain setting)

Gain =  $\frac{140k\Omega}{(Ri + 5k\Omega)}$ ; with external resistor \*TDFN only

#### **Typical Performance Characteristics**

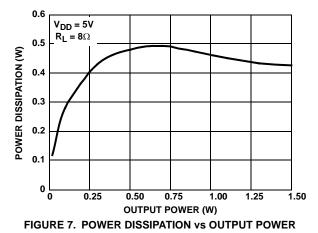

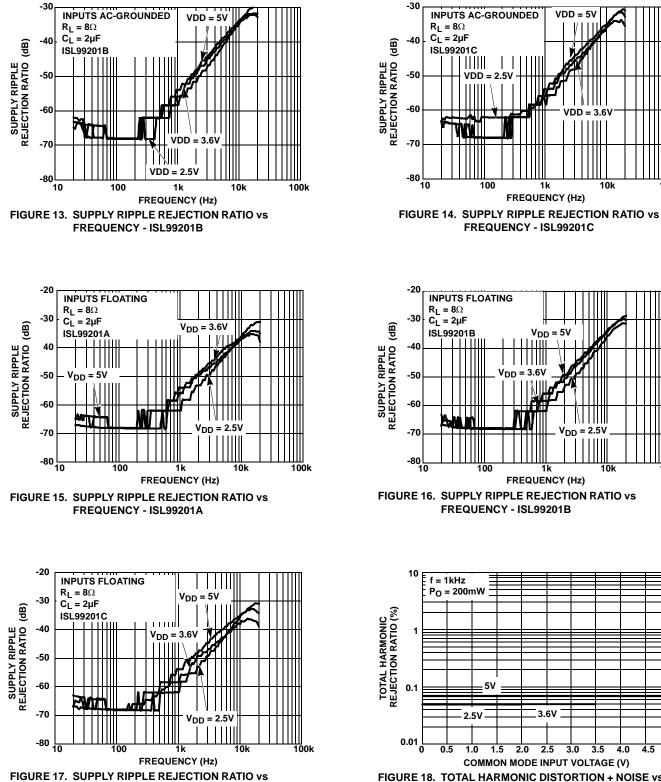

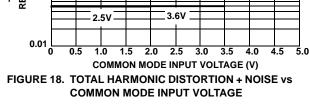

Typical Performance Characteristics (Continued)

FIGURE 8. OUTPUT POWER vs SUPPLY VOLTAGE

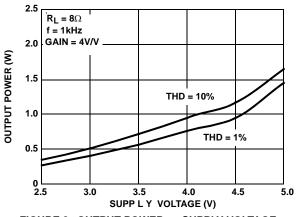

#### Typical Performance Characteristics (Continued)

FREQUENCY - ISL99201C

10k

= 2.5V

10

100k

100k

## Typical Performance Characteristics (Continued)

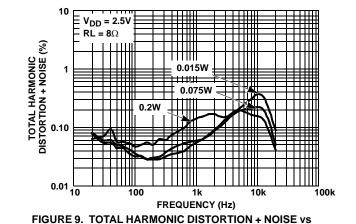

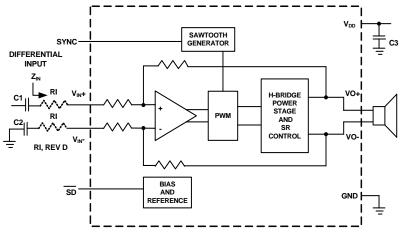

**Typical Applications**

FIGURE 22. TYPICAL CIRCUIT WITH DIFFERENTIAL INPUT AND INPUT CAPACITORS

# Typical Applications (Continued)

FIGURE 23. TYPICAL CIRCUIT WITH SINGLE-ENDED INPUT

11

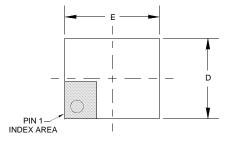

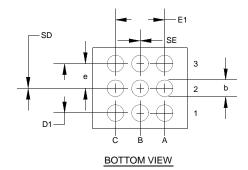

## Wafer Level Chip Scale Package (WLCSP 0.4mm Ball Pitch)

TOP VIEW

#### W3x3.9C

#### 3x3 ARRAY 9 BALL WAFER LEVEL CHIP SCALE PACKAGE

| SYMBOL         | MILLIMETERS                     |

|----------------|---------------------------------|

| А              | 0.445 Min, 0.495 Nom, 0.545 Max |

| A <sub>1</sub> | 0.190 ±0.025                    |

| A <sub>2</sub> | 0.305 ±0.025                    |

| b              | 0.270 ±0.030                    |

| D              | 1.315 ±0.020                    |

| D <sub>1</sub> | 0.800 BASIC                     |

| E              | 1.535 ±0.020                    |

| E <sub>1</sub> | 0.800 BASIC                     |

| е              | 0.400 BASIC                     |

| SD             | 0 BASIC                         |

| SE             | 0 BASIC                         |

| Ν              | umber of Bumps: 9               |

|                | Rev. 0 5/08                     |

NOTES:

1. Dimensions are in Millimeters.

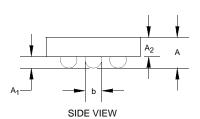

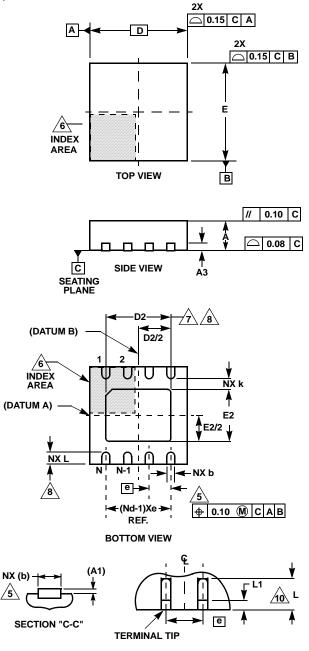

## Thin Dual Flat No-Lead Plastic Package (TDFN)

Dual Flat No - Lead Plastic package (DFN)

FOR EVEN TERMINAL/SIDE

#### L8.3x3A

8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE

| SYMBOL | MIN  | NOMINAL  | MAX  | NOTES       |

|--------|------|----------|------|-------------|

| А      | 0.70 | 0.75     | 0.80 | -           |

| A1     | -    | 0.02     | 0.05 | -           |

| A3     |      | 0.20 REF |      | -           |

| b      | 0.25 | 0.30     | 0.35 | 5, 8        |

| D      |      | 3.00 BSC |      | -           |

| D2     | 2.20 | 2.30     | 2.40 | 7, 8, 9     |

| E      |      | 3.00 BSC |      |             |

| E2     | 1.40 | 1.50     | 1.60 | 7, 8, 9     |

| е      |      | 0.65 BSC |      |             |

| k      | 0.25 | -        | -    | -           |

| L      | 0.20 | 0.30     | 0.40 | 8           |

| Ν      | 8    |          |      | 2           |

| Nd     |      | 4        |      | 3           |

|        |      |          |      | Rev. 3 11/0 |

NOTES:

Dimensioning and tolerancing conform to ASME Y14.5-1994.

2. N is the number of terminals.

- 3. Nd refers to the number of terminals on D.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- 9. Compliant to JEDEC MO-WEEC-2 except for the "L" min dimension.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com