ISL94212

Multi-Cell Li-Ion Battery Manager

FN7938 Rev 1.00 April 23, 2015

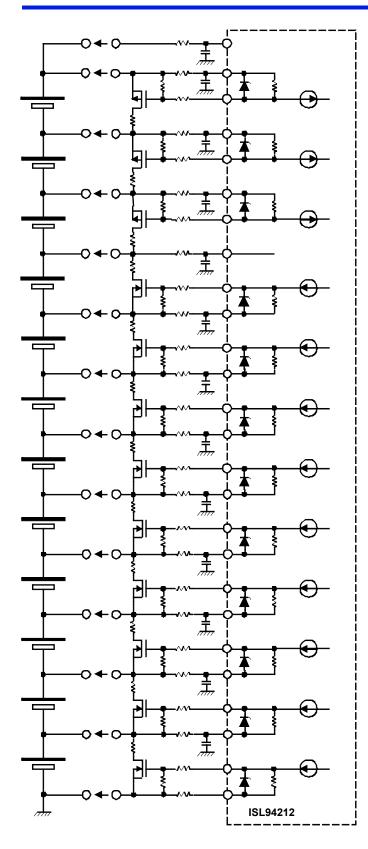

The ISL94212 Li-ion battery manager IC supervises up to 12 series connected cells. The part provides accurate monitoring, cell balancing and extensive system diagnostics functions. Three cell balancing modes are provided: Manual Balancing mode, Timed Balancing mode and Auto Balance mode. The Auto Balance mode terminates balancing functions when a charge transfer value has been met.

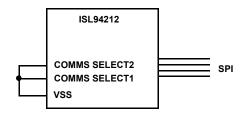

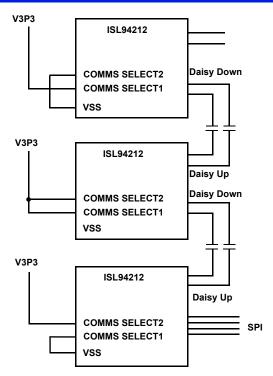

The ISL94212 communicates to a host microcontroller via an SPI interface and to other ISL94212 devices using a robust, proprietary, two-wire Daisy Chain system.

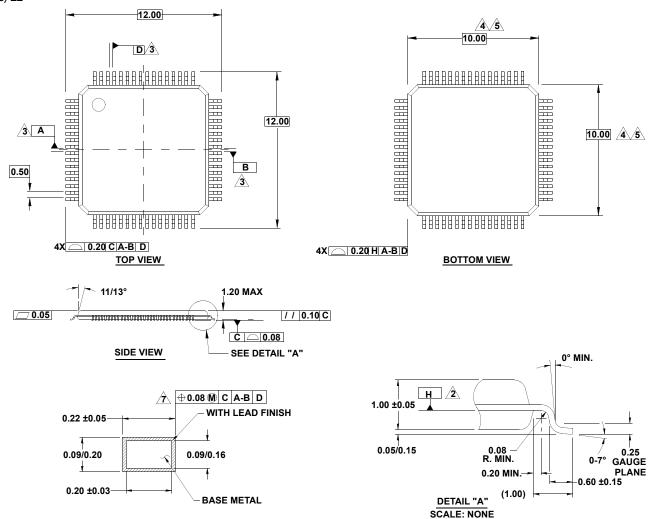

The ISL94212 is offered in a 64 Ld TQFP package and is specified for an operational temperature range of -40°C to +85°C.

### **Applications**

- · Light electric vehicle (LEV); E-Moto; E-Bike

- . Battery backup systems; Energy Storage Systems (ESS)

- Solar Farms

- · Portable and semi-portable equipment

#### **Features**

- Up to 12-cell voltage monitors, support Li-lon CoO<sub>2</sub>, Li-ion Mn<sub>2</sub>O<sub>4</sub>, and Li-ion FePO4 chemistries

- Cell voltage measurement accuracy ±10mV

- · 13-bit cell voltage measurement

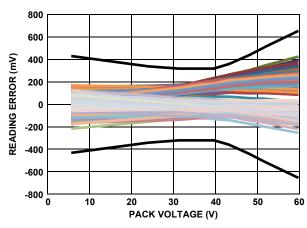

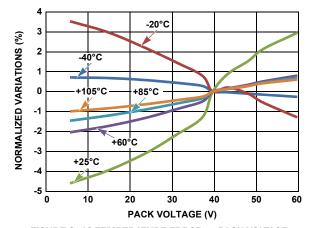

- Pack voltage measurement accuracy ±180mV

- 14-bit pack voltage and temperature measurements

- Cell voltage scan rate of 19.5µs per cell (234µs to scan 12 cells)

- · Internal temperature monitoring

- · Up to four external temperature inputs

- · Robust daisy chain communications system

- · Integrated system diagnostics for all key internal functions

- · Hardwired and communications based fault notification

- Integrated watchdog shuts down device if communication is lost

- 7μA shutdown current: Enable = V<sub>SS</sub>

- · 2Mbps SPI

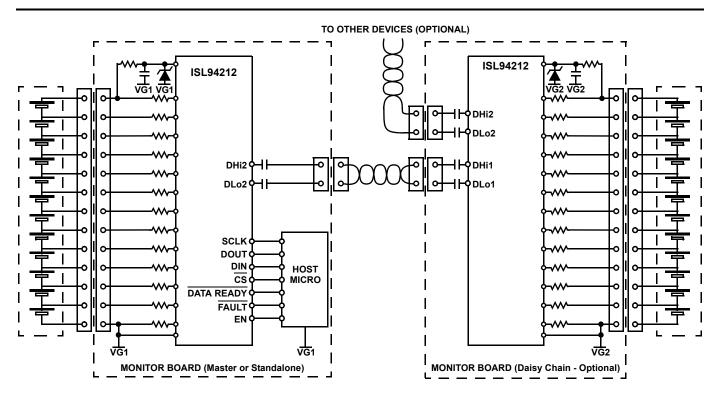

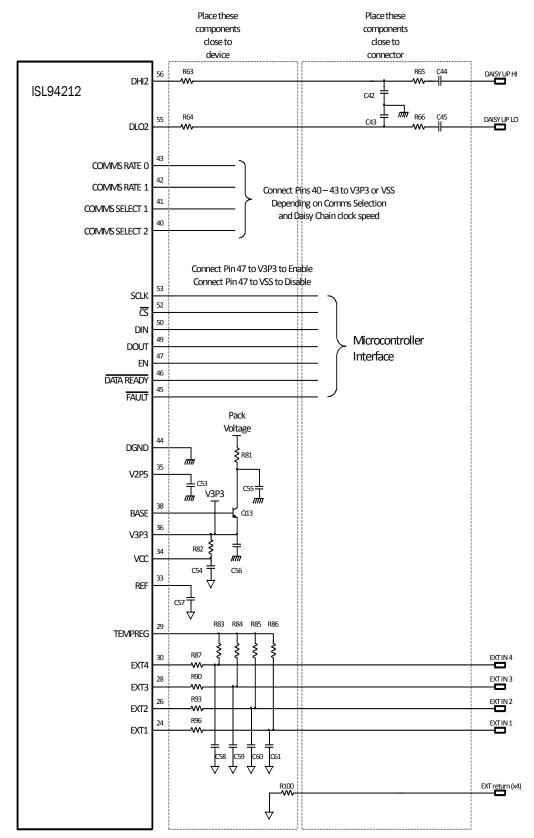

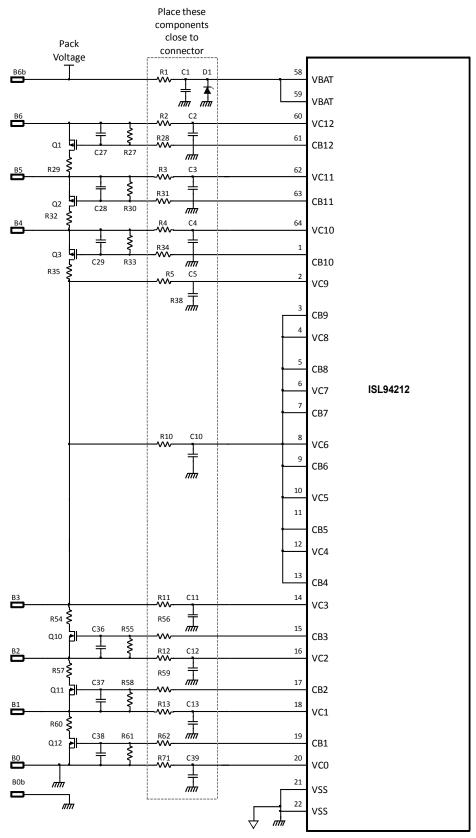

FIGURE 1. TYPICAL APPLICATION

| Table of Contents                                                                 | CRC Calculation                                                |      |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------|------|

| Ordering Information4                                                             | Daisy Chain Addressing                                         |      |

| Pin Configuration4                                                                | Daisy Chain Commands                                           | . 40 |

| Absolute Maximum Ratings7                                                         | Identify                                                       |      |

| Thermal Information                                                               | ACK (Acknowledge)                                              |      |

| Recommended Operating Conditions7                                                 | NAK (Not Acknowledge)                                          |      |

| Electrical Specifications                                                         | Reset                                                          |      |

| Timing Diagrams14                                                                 | Address All                                                    |      |

|                                                                                   | Alarm Signals                                                  |      |

| Typical Performance Curves15                                                      | Watchdog Function                                              |      |

| Device Description and Operation21                                                | Communications Faults                                          |      |

| Power Modes                                                                       | Communication Failure                                          | . 44 |

| Measurement Modes                                                                 | Scan Counter                                                   | . 45 |

| Measurement Mode Commands                                                         | Daisy Chain Communications Conflicts                           |      |

| Scan Once                                                                         | Memory Checksum                                                | . 45 |

| Scan Voltages22                                                                   | Settling Time Following Diagnostic Activity                    | . 45 |

| Scan Temperatures                                                                 | Open Wire Test                                                 | . 45 |

| Scan Mixed                                                                        | Cell Balancing                                                 | . 45 |

| Scan Wires                                                                        | Fault Signal Filtering                                         | . 46 |

| Scan All                                                                          | Fault Diagnostics                                              | . 46 |

| Scan Continuous23                                                                 | Sleep Mode                                                     | . 50 |

| Measure23                                                                         | Wakeup                                                         | . 50 |

| Cell Voltage Measurement Accuracy                                                 | Fault Response in Sleep Mode                                   | . 50 |

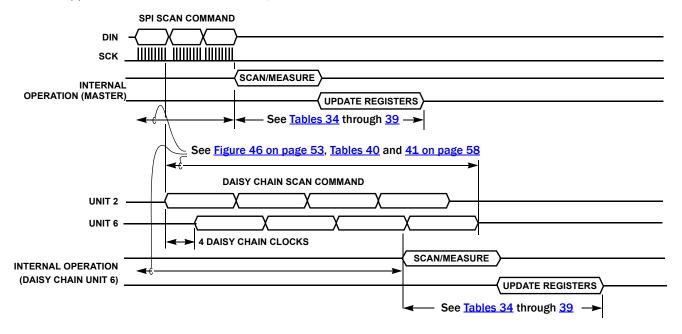

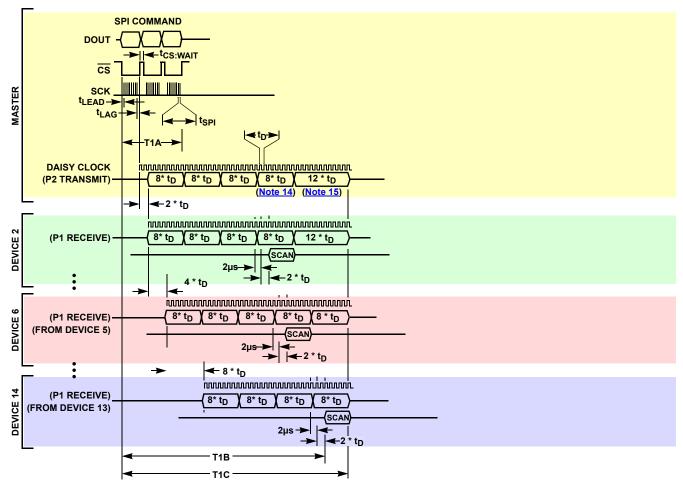

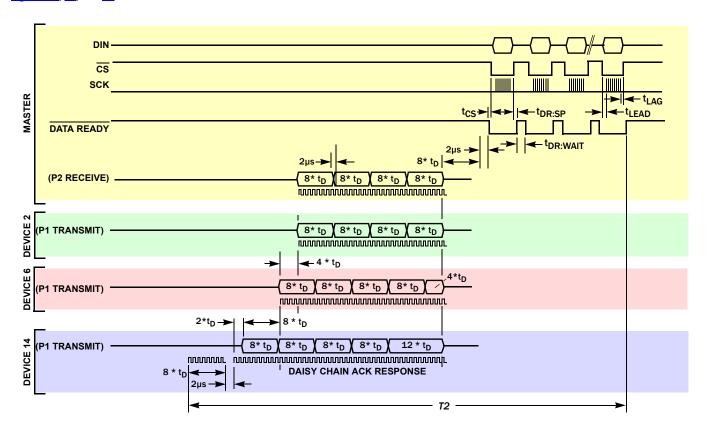

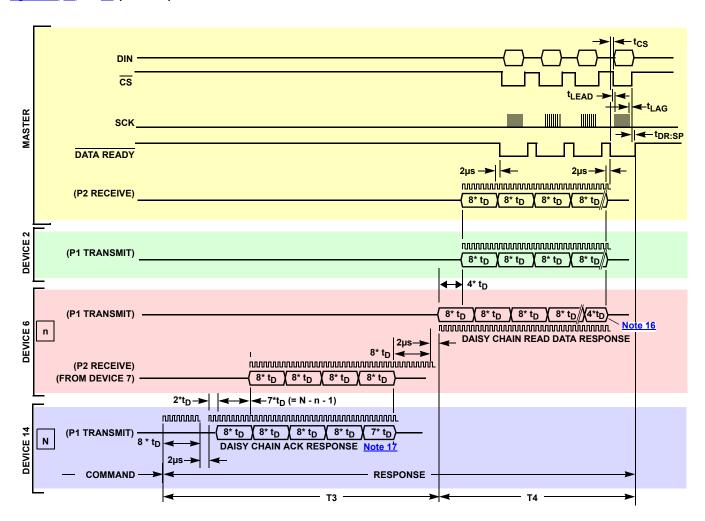

| Temperature Monitoring24                                                          | Communication and Measurement Diagrams                         | . 50 |

| Cell Balancing Functions25                                                        | Measurement Timing Diagrams                                    | . 51 |

| Balance Setup Register25                                                          | Command Timing Diagram                                         | . 52 |

| Balance Status Register                                                           | Response Timing Diagrams                                       | . 53 |

| Manual Balance Mode26                                                             | Communication and Measurement Timing Tables                    | . 56 |

| Timed Balance Mode27                                                              | Measurement Timing Tables                                      | . 56 |

| Auto Balance Mode                                                                 | Command Timing Tables                                          | . 57 |

| Balance FET Drivers29                                                             | Response Timing Tables                                         | . 58 |

| Device Setup Register30                                                           | System Registers                                               | . 62 |

| Cell Balance Enabled Register30                                                   | Register Descriptions                                          | . 62 |

| System Configuration                                                              | Cell Voltage Data                                              | . 62 |

| SPI Interface                                                                     | Temperature Data, Secondary Voltage Reference Data, Scan Count | . 62 |

| Full Duplex Operation                                                             | Fault Registers                                                |      |

| Half Duplex Operation         32           Non-daisy Chain Systems         33     | Setup Registers                                                |      |

|                                                                                   | Cell Balance Registers                                         |      |

| Normal Communications                                                             | Reference Coefficient Registers                                |      |

| Alarm Signals                                                                     | Cells In Balance Register                                      |      |

| Communication Faults         33           Fault Response in Sleep Mode         34 | Device Commands                                                |      |

| Example Communications                                                            | Nonvolatile Memory (EEPROM) Checksum                           |      |

| Daisy Chain Systems                                                               | Applications Circuits Information                              |      |

| Daisy Chain Ports                                                                 |                                                                |      |

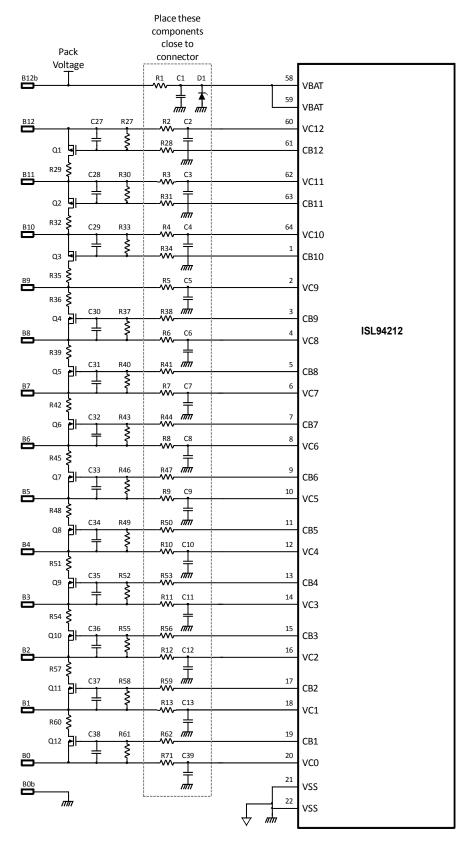

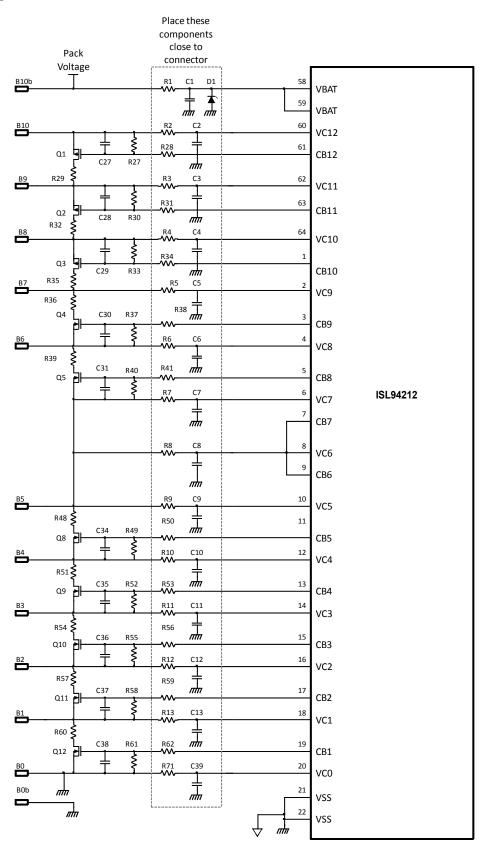

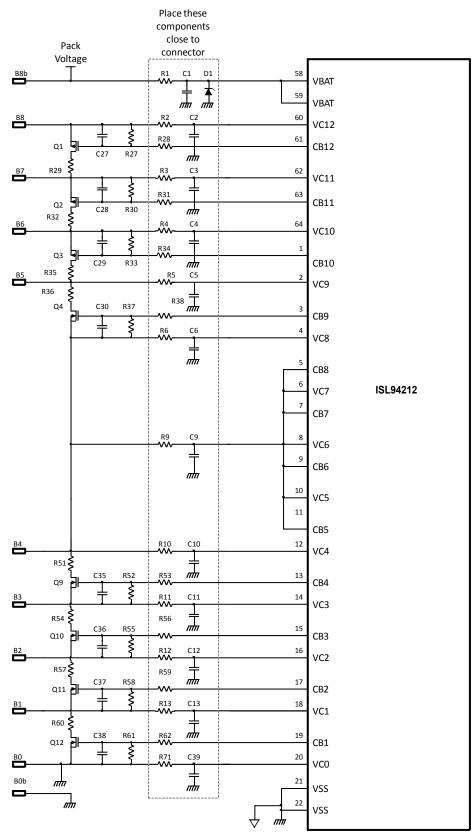

|                                                                                   | Typical Applications Circuits                                  | . 72 |

| Communications Protocol35                                                         | Typical Applications Circuits  Typical Application Circuits    |      |

#### ISL94212

|     | Component Selection                                | , |

|-----|----------------------------------------------------|---|

|     | Operating the ISL94212 with Reduced Cell Counts 78 | , |

| Гур | oical Application Circuits79                       | , |

|     | Power Supplies82                                   |   |

|     | Voltage Reference Bypass Capacitor82               |   |

|     | Cell Balancing Circuits82                          |   |

|     | Cell Voltage Measurements During Balancing83       | , |

|     | Balancing with Scan Continuous Mode Enabled 83     | , |

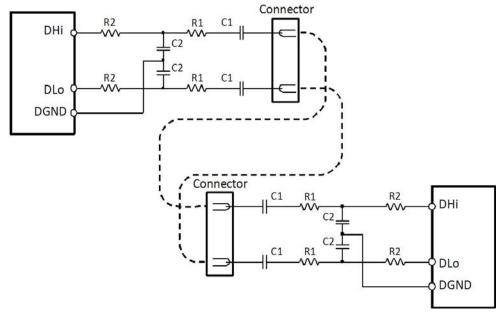

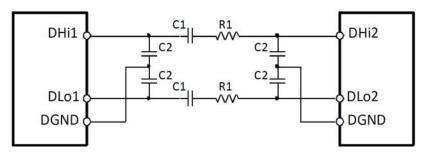

|     | Daisy Chain Communications System83                | , |

|     | External Inputs                                    | , |

|     | Board Level Calibration86                          | , |

| Wa  | orked Examples86                                   | , |

|     | Voltage Reference Check Calculation                | į |

|     | Cell Balancing – Manual Mode87                     | , |

|     | Cell Balancing – Timed Mode87                      | , |

|     | Cell Balancing – Auto Mode88                       | , |

| Re  | gister Map90                                       | ) |

| Re  | vision History95                                   | , |

| Pa  | ckage Outline Drawing                              |   |

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3, 4) | PART<br>MARKING | TRIM VOLTAGE, V <sub>NOM</sub> (V) | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|--------------------------------|-----------------|------------------------------------|---------------------|-----------------------------|----------------|

| ISL94212INZ (Note 1)           | ISL94212INZ     | 3.3                                | -40 to +85          | 64 Ld TQFP                  | Q64.10x10D     |

| ISL94212EVKIT1Z                | Evaluation Kit  |                                    |                     |                             |                |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level Rating (MSL) for the package, please see the Intersil ISL94212. For more information on handling and processing moisture sensitive devices, please see Techbrief TB363.

- 4. For other trim options, please contact Marketing.

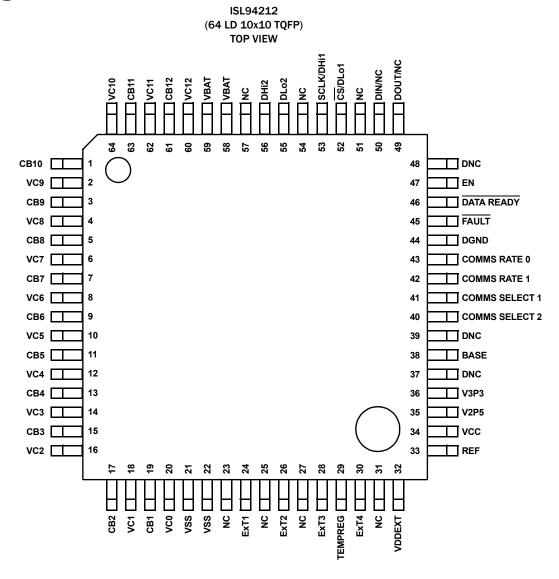

## **Pin Configuration**

# **Pin Descriptions**

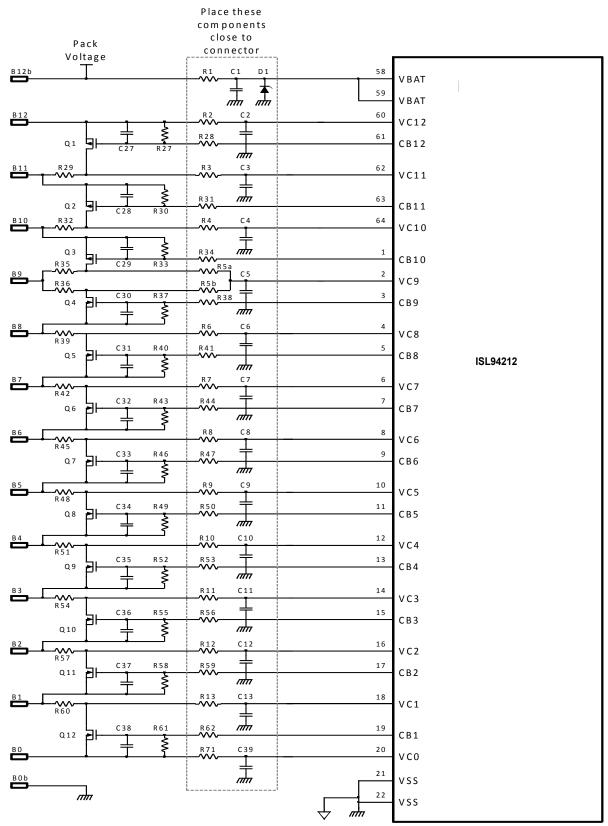

| SYMBOL                                                                   | PIN NUMBER                                              | DESCRIPTION                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VC0, VC1, VC2, VC3, VC4,<br>VC5, VC6, VC7, VC8, VC9,<br>VC10, VC11, VC12 | 20, 18, 16,<br>14, 12, 10, 8,<br>6, 4, 2, 64,<br>62, 60 | Battery cell voltage inputs. VCn connects to the positive terminal of CELLn and the negative terminal of CELLn+1. (VC12 connects only to the positive terminal of CELL12 and VCO only connects with the negative terminal of CELL1.)                                                 |

| CB1, CB2, CB3, CB4, CB5,<br>CB6, CB7, CB8, CB9, CB10,<br>CB11, CB12      | 19, 17, 15,<br>13, 11, 9, 7,<br>5, 3, 1, 63, 61         | Cell Balancing FET control outputs. Each output controls an external FET which provides a current path around the cell for balancing.                                                                                                                                                |

| VBAT                                                                     | 58, 59                                                  | Main IC Supply pins. Connect to the most positive terminal in the battery string.                                                                                                                                                                                                    |

| VSS                                                                      | 21, 22                                                  | Ground. These pins connect to the most negative terminal in the battery string.                                                                                                                                                                                                      |

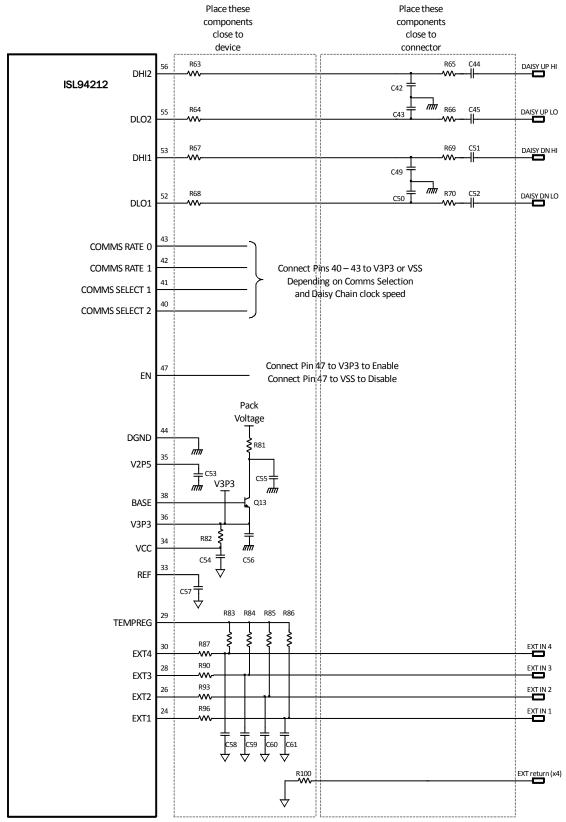

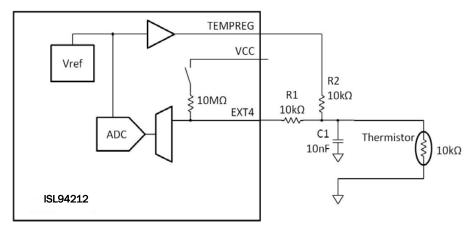

| ExT1, ExT2, ExT3, ExT4                                                   | 24, 26, 28,<br>30                                       | External temperature monitor or general purpose inputs. The temperature inputs are intended for use with external resistor networks using NTC type thermistor sense elements but may also be used as general purpose analog inputs at the user's discretion. OV to 2.5V input range. |

| TEMPREG                                                                  | 29                                                      | Temperature monitor voltage regulator output. This is a switched 2.5V output, which supplies a reference voltage to external NTC thermistor circuits to provide ratiometric ADC inputs for temperature measurement.                                                                  |

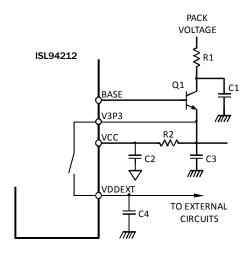

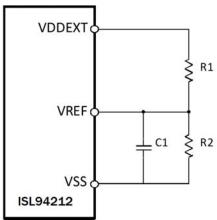

| VDDEXT                                                                   | 32                                                      | External V3P3 supply input/output. Connected to the V3P3 pin via a switch, this pin may be used to power external circuits from the V3P3 supply. The switch is open when the ISL94212 is placed in <b>Sleep mode</b> .                                                               |

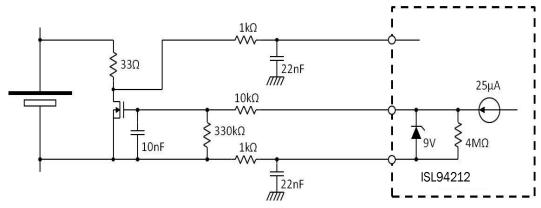

| REF                                                                      | 33                                                      | $2.5 V$ voltage reference decoupling pin. Connect a $2.0 \mu F$ to $2.5 \mu F$ X7R capacitor to VSS. Do not connect any additional external load to this pin.                                                                                                                        |

| vcc                                                                      | 34                                                      | Analog supply voltage input. Connect to V3P3 via a 33Ω resistor. Connect a 1μF capacitor to ground.                                                                                                                                                                                  |

| V2P5                                                                     | 35                                                      | Internal 2.5V digital supply decoupling pin. Connect a 1µF capacitor to DGND.                                                                                                                                                                                                        |

| V3P3                                                                     | 36                                                      | 3.3V digital supply voltage input. Connect the emitter of the external NPN regulator transistor to this pin. Connect a $1\mu F$ capacitor to DGND.                                                                                                                                   |

| Base                                                                     | 38                                                      | Regulator control pin. Connect the external NPN transistor's base. Do not let this pin float,                                                                                                                                                                                        |

| DNC                                                                      | 37, 39, 48                                              | Do not connect. Leave pins floating.                                                                                                                                                                                                                                                 |

| Comms Select 1                                                           | 41                                                      | Communications port 1 mode select pin. Connect via a $1k\Omega$ resistor to V3P3 for Daisy Chain communications on port 1 or to DGND for SPI operation on port 1.                                                                                                                    |

| Comms Select 2                                                           | 40                                                      | Communications port 2 mode select pin. Connect via a $1k\Omega$ resistor to V3P3 to enable port 2 or to DGND to disable this port.                                                                                                                                                   |

| Comms Rate 0,<br>Comms Rate 1                                            | 43, 42                                                  | Daisy Chain communications data rate setting. Connect via a $1 \text{k}\Omega$ resistor to DGND ('0') or to V3P3 ('1') to select between various communication data rates.                                                                                                           |

| DGND                                                                     | 44                                                      | Digital Ground.                                                                                                                                                                                                                                                                      |

| Fault                                                                    | 45                                                      | Logic fault output. Asserted low if a fault condition exists.                                                                                                                                                                                                                        |

| Data Ready                                                               | 46                                                      | SPI data ready. Asserted low when the device is ready to transmit data to the host microcontroller.                                                                                                                                                                                  |

| EN                                                                       | 47                                                      | Enable input. Tie to V3P3 to enable the part. Tie to DGND to disable (all IC functions are turned off).                                                                                                                                                                              |

| DOUT/NC                                                                  | 49                                                      | Serial Data Output (SPI) or NC (Daisy Chain). OV to 3.3V push-pull output.                                                                                                                                                                                                           |

| DIN/NC                                                                   | 50                                                      | Serial Data Input (SPI) or NC (Daisy Chain). OV to 3.3V input.                                                                                                                                                                                                                       |

| CS/DLo1                                                                  | 52                                                      | Chip-Select, active low 3.3V input (SPI) or Daisy Chain port 1 Lo connection.                                                                                                                                                                                                        |

| SCLK/DHi1                                                                | 53                                                      | Serial-Clock Input (SPI) or Daisy Chain port 1 Hi connection.                                                                                                                                                                                                                        |

| DHi2                                                                     | 56                                                      | Daisy Chain port 2 Hi connection.                                                                                                                                                                                                                                                    |

| DLo2                                                                     | 55                                                      | Daisy Chain port 2 Lo connection.                                                                                                                                                                                                                                                    |

| NC                                                                       | 23, 25, 27,<br>31, 51, 54,<br>57                        | No internal connection.                                                                                                                                                                                                                                                              |

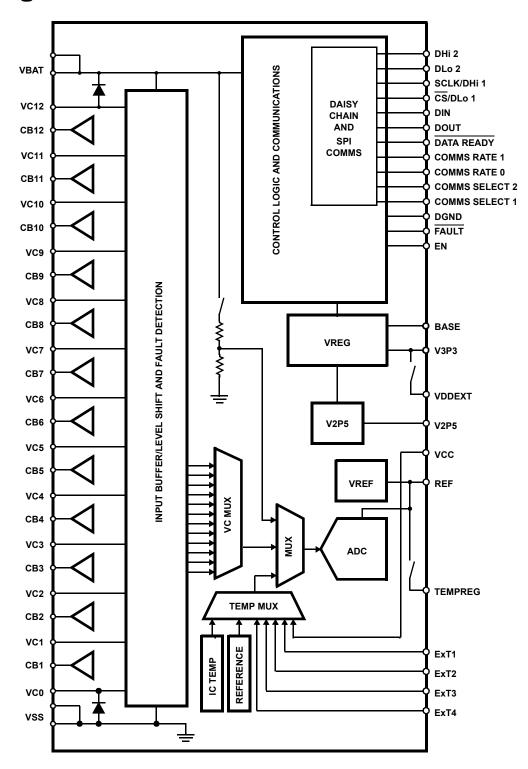

# **Block Diagram**

#### **Absolute Maximum Ratings**

Unless otherwise specified. With respect to VSS. DIN, SCLK, CS, DOUT, Data Ready, Comms Select n, ExTn, TEMPREG, REF, V3P3, VCC, Fault, Comms Rate n, Base, EN, VDDEXT.....-0.2V to 4.1V V2P5.....--0.2V to 2.9V VBAT.....-0.5V to 63V Dhi1, DLo1, DHi2, DLo2 .....-0.5V to (VBAT + 0.5V) VC0.....-0.5V to + 9.0V VC1.....-0.5V to + 18V VC2.....-0.5V to + 18V VC3.....-0.5V to + 27V VC5.....--0.5V to + 36V VC6.....--0.5V to + 36V VC7.....-0.5V to + 45V VC8.....-0.5V to + 45V VC9.....-0.5V to + 54V VC10.....-0.5V to + 63V VC11.....-0.5V to + 63V VC12.....-0.5V to + 63V VCn (for n = 0 to 12). . . . . . . . . . . . -0.5 to VBAT + 0.5V CBn (for n = 1 to 12) ......-0.5 to VBAT + 0.5V CBn (for n = 1 to 9) ...... V(VCn-1) - 0.5V to V(VCn-1) + 9VCurrent into VCn, VBAT, VSS (Latch up Test) . . . . . . . . . . . . ±100mA **ESD Rating** Human Body Model (Tested per JESD22-A114F)......2kV Machine Model (Tested per JESD22A115-A) . . . . . . . . . . . . 200V Charge Device Model (Tested per JESD22-C101D) . . . . . . . . . . . . . . . . . 750V Latch-up (Tested per JESD-78B; Class 2, Level A) ............ 100mA NOTE: DOUT, Data Ready, and Fault are digital outputs and should not be

**Thermal Information**

| Thermal Resistance (Typical)               | $\theta_{JA}\left(C/W\right)$ | $\theta_{JC}(C/W)$ |

|--------------------------------------------|-------------------------------|--------------------|

| 64 Ld TQFP Package (Notes 5, 6)            | 42                            | 9                  |

| Max Continuous Package Power Dissipation . |                               | 400mW              |

| Storage Temperature                        | 5!                            | 5°C to +125°C      |

| Max Operating Junction Temperature         |                               | +125°C             |

| Pb-Free Reflow Profile                     |                               | see <u>TB493</u>   |

#### **Recommended Operating Conditions**

| T <sub>A</sub> , Ambient Temperature Range  | 40°C to +85°C             |

|---------------------------------------------|---------------------------|

| V <sub>BAT</sub>                            | 6V to 60V                 |

| V <sub>BAT</sub> (Daisy Chain Operation)    | 10V to 60V                |

| VCn (for n = 1 to 12)                       | V(VCn-1) to V(VCn-1) + 5V |

| VCO                                         | 0.1V to 0.1V              |

| CBn (for n = 1 to 9)                        | V(VCn-1) to V(VCn-1) + 9V |

| CBn (for n = 10 to 12)                      | V(VCn) - 9V to V(VCn)     |

| DIN, SCLK, CS, DOUT, Data Ready, Comms Sele | ect 1,                    |

| Comms Select 2, TEMPREG,                    |                           |

| REF, V3P3, VCC, Fault, Comms Rate 0, Comi   | ms Rate 1,                |

| EN, VDDEXT                                  |                           |

| ExT1,ExT2,ExT3,Ext4                         | 0V to 2.5V                |

|                                             |                           |

driven from external sources. V2P5, REF, TEMPREG and BASE are analog outputs and should not be driven from external sources.

#### NOTES:

5. θ<sub>IA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product

6. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

reliability and result in failures not covered by warranty.

# **Electrical Specifications** $V_{BAT} = 6 \text{ to } 60V$ , $T_A = -40 \,^{\circ}\text{C}$ to $+85 \,^{\circ}\text{C}$ , unless otherwise specified. **Boldface limits apply across the operating temperature range, -40 \,^{\circ}\text{C} to +85 \,^{\circ}\text{C}.**

| PARAMETER                     | SYMBOL              | TEST CONDITIONS                                                                                                                         | MIN<br>( <u>Note 7</u> ) | TYP | MAX<br>(Note 7) | UNITS |

|-------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----------------|-------|

| Power-up Condition Threshold  | V <sub>POR</sub>    | V <sub>BAT</sub> voltage (rising)                                                                                                       | 4.8                      | 5.1 | 5.6             | V     |

| Power-up Condition Hysteresis | V <sub>PORhys</sub> |                                                                                                                                         |                          | 400 |                 | mV    |

| Initial Power-up Delay        | t <sub>POR</sub>    | Time after VPOR condition V <sub>REF</sub> from 0V to 0.95 x V <sub>REF</sub> (nom) (EN tied to V3P3) Device can now communicate        |                          |     | 27.125          | ms    |

| Enable Pin Power-up Delay     | t <sub>PUD</sub>    | Delay after EN = 1 to V <sub>REF</sub> from 0V to 0.95 x V <sub>REF</sub> (nom) (V <sub>BAT</sub> = 39.6V) - Device can now communicate |                          |     | 27.125          | ms    |

| PARAMETER                                                 | SYMBOL                  | TEST CONDITIONS                                                                                                                               |       | MIN<br>( <u>Note 7</u> ) | TYP  | MAX<br>( <u>Note 7</u> ) | UNITS |

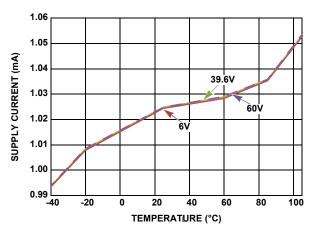

|-----------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------|------|--------------------------|-------|

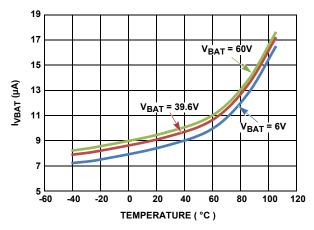

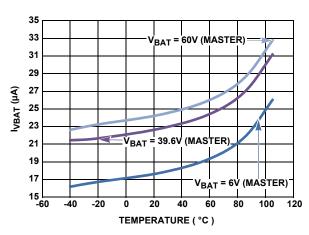

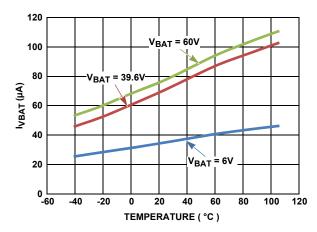

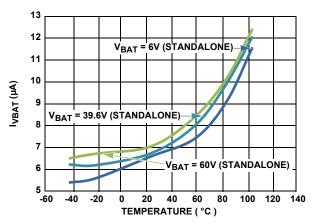

| V <sub>BAT</sub> Supply Current                           | I <sub>VBAT</sub>       | Non-daisy chain configuration. Device enabled. No communications, ADC, measurement, balancing or open wire detection activity.                | 6V    | 10                       | 35   | 75                       | μА    |

|                                                           |                         |                                                                                                                                               | 39.6V | 10                       | 64   | 220                      | μΑ    |

|                                                           |                         |                                                                                                                                               | 60V   | 10                       | 90   | 230                      | μΑ    |

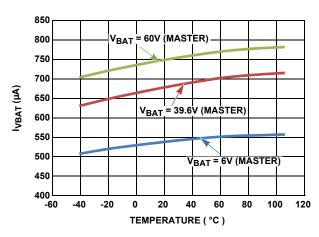

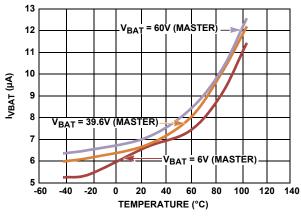

|                                                           | IVBATMASTER             | Daisy chain configuration – master device.<br>Enabled. No communications, ADC,<br>measurement, balancing or open wire<br>detection activity.  | 6V    | 400                      | 530  | 660                      | μА    |

|                                                           |                         |                                                                                                                                               | 39.6V | 500                      | 680  | 900                      | μΑ    |

|                                                           |                         |                                                                                                                                               | 60V   | 550                      | 750  | 1000                     | μΑ    |

|                                                           |                         | Peak current when daisy chain transmitting                                                                                                    |       |                          | 18   |                          | mA    |

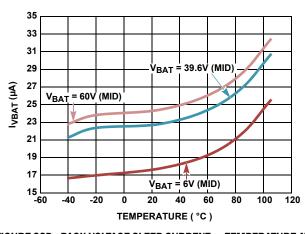

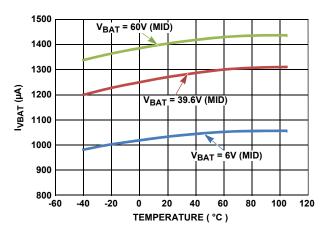

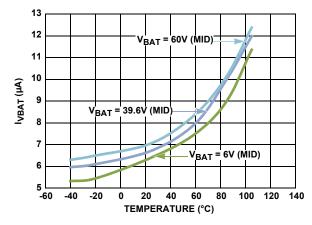

|                                                           | I <sub>VBATMID</sub>    | Daisy chain configuration – mid stack device.<br>Enabled. No communications, ADC,<br>measurement, balancing or open wire                      | 6V    | 700                      | 1020 | 1300                     | μА    |

|                                                           |                         | detection activity.                                                                                                                           | 39.6V | 900                      | 1250 | 1600                     | μΑ    |

|                                                           |                         |                                                                                                                                               | 60V   | 1000                     | 1400 | 1700                     | μΑ    |

|                                                           |                         | Peak current when daisy chain transmitting                                                                                                    |       |                          | 18   |                          | mA    |

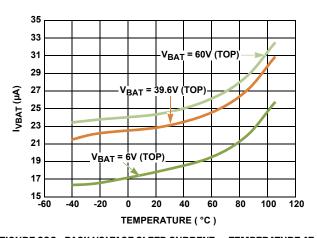

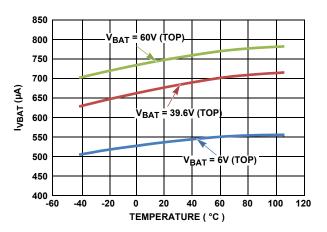

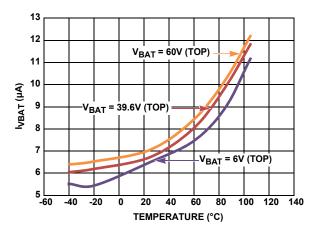

|                                                           | IVBATTOP                | Daisy chain configuration – top device.<br>Enabled. No communications, ADC,<br>measurement, balancing or open wire                            | 6V    | 400                      | 530  | 660                      | μΑ    |

|                                                           |                         | detection activity.                                                                                                                           | 39.6V | 500                      | 680  | 900                      | μΑ    |

|                                                           |                         |                                                                                                                                               | 60V   | 550                      | 750  | 1000                     | μΑ    |

|                                                           |                         | Peak current when daisy chain transmitting                                                                                                    |       |                          | 18   |                          | mA    |

|                                                           | I <sub>VBATSLEEP1</sub> | Sleep mode<br>(EN = 1, daisy chain configuration).                                                                                            |       | 10                       | 19   | 36                       | μА    |

|                                                           | IVBATSLEEP2             | Sleep mode<br>(EN = 1, standalone, non-daisy chain)                                                                                           |       | 5                        | 9    | 18                       | μА    |

|                                                           | IVBATSHDN               | Shutdown. device "off" (EN = 0)<br>(daisy chain and non-daisy chain configuration                                                             | s)    | 5                        | 7    | 18                       | μА    |

| V <sub>BAT</sub> Supply Current Tracking.<br>Sleep Mode.  | I <sub>VBATΔSLEEP</sub> | $EN=1$ , daisy chain sleep mode configuration. $V_{BAT}$ current difference between any two devicoperating at the same temperature and supply |       | 0                        |      | 10.5                     | μΑ    |

| V <sub>BAT</sub> Incremental Supply Current,<br>Balancing | IVBATBAL                | All balancing circuits on. Incremental current:<br>Add to non-balancing V <sub>BAT</sub> current.<br>V <sub>BAT</sub> = 39.6V                 |       | 200                      | 300  | 400                      | μΑ    |

| V3P3 Regulator Voltage (Normal)                           | V <sub>3P3N</sub>       | EN = 1, load current range 0 to 5 mA.<br>V <sub>BAT</sub> = 39.6V                                                                             |       | 3.2                      | 3.35 | 3.5                      | V     |

| V3P3 Regulator Voltage (Sleep)                            | V <sub>3P3S</sub>       | EN = 1, load current range. No load. (SLEEP).<br>V <sub>BAT</sub> = 39.6V                                                                     |       | 2.4                      | 2.7  | 3.05                     | V     |

| V3P3 Regulator Control Current                            | I <sub>Base</sub>       | Current sourced from base output.<br>V <sub>BAT</sub> = 6V                                                                                    |       | 1                        | 1.5  |                          | mA    |

| V3P3 Supply Current                                       | I <sub>V3P3</sub>       | Device enabled<br>No measurement activity, normal mode                                                                                        |       | 0.8                      | 1    | 1.3                      | mA    |

| V <sub>REF</sub> Reference Voltage                        | V <sub>REF</sub>        | EN = 1, no load, normal mode                                                                                                                  |       |                          | 2.5  |                          | ٧     |

| PARAMETER                                                                   | SYMBOL                  | TEST CONDITIONS                                                                                                                                                              | MIN<br>( <u>Note 7</u> ) | TYP   | MAX<br>( <u>Note 7</u> ) | UNITS |

|-----------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------|

| VDDEXT Switch Resistance                                                    | R <sub>VDDEXT</sub>     | Switch ON-resistance, V <sub>BAT</sub> = 39.6V                                                                                                                               | 5                        | 12    | 22                       | Ω     |

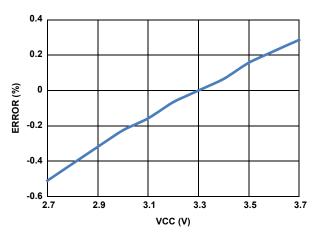

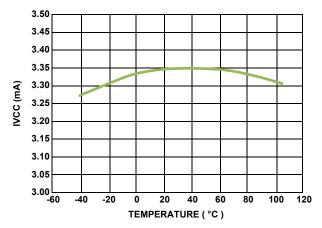

| VCC Supply Current                                                          | lvcc                    | Device enabled (EN = 1). Standalone or daisy configuration. No ADC or daisy chain communications active.                                                                     | 2.0                      | 3.25  | 5.0                      | mA    |

|                                                                             | I <sub>VCCACTIVE1</sub> | Device enabled (EN = 1). Standalone or daisy configuration. Average current during 16ms scan continuous operation. V <sub>BAT</sub> = 39.6V                                  |                          | 6.0   |                          | mA    |

|                                                                             | I <sub>VCCSLEEP</sub>   | Device enabled (EN = 1). Sleep mode. V <sub>BAT</sub> = 39.6V                                                                                                                |                          | 2.4   |                          | μΑ    |

|                                                                             | Ivccshdn                | Device disabled (EN = 0). Shutdown mode.                                                                                                                                     | 0                        | 1.2   | 9.0                      | μΑ    |

| MEASUREMENT SPECIFICATIONS                                                  | 1                       |                                                                                                                                                                              |                          | 1     | 11                       | •     |

| Cell Voltage Input Measurement<br>Range                                     | V <sub>CELL</sub>       | VC(N) - VC(N-1). For design reference.                                                                                                                                       | 0                        |       | 5                        | V     |

| Cell Monitor Voltage Resolution                                             | V <sub>CELLRES</sub>    | [VC(N)-VC(N-1)] LSB step size (13-bit signed number), 5V full scale value                                                                                                    |                          | 0.61  |                          | mV    |

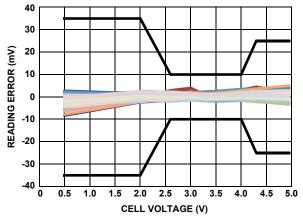

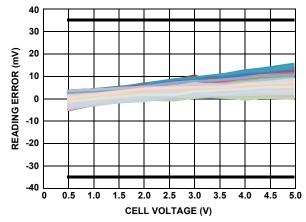

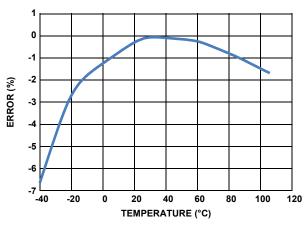

| ISL94212 Cell Monitor Voltage<br>Error (Absolute)                           | ∆V <sub>CELLA</sub>     | Absolute cell measurement error (Cell measurement error compared with applied voltage with 1k series resistor.) Temperature = 0°C to +50°C, V <sub>CELL</sub> = 2.6V to 4.0V | -10                      |       | 10                       | mV    |

|                                                                             |                         | Temperature = +50 °C to +85 °C, V <sub>CELL</sub> = 2.0V to 4.3V                                                                                                             | -25                      |       | 25                       | mV    |

|                                                                             |                         | Temperature = -40 °C to 0 °C, V <sub>CELL</sub> = 2.0V to 4.3V                                                                                                               | -35                      |       | 35                       | m۷    |

| ISL94212 Cell Monitor Voltage<br>Error (Relative)                           | ΔV <sub>CELLB</sub>     | Relative cell measurement error (Max absolute cell measurement error Min absolute cell measurement error) Temperature = 0°C to +50°C                                         | 0                        |       | 7.5                      | mV    |

|                                                                             |                         | •                                                                                                                                                                            | 0                        |       | 7.5                      | mV    |

|                                                                             |                         | Temperature = -40°C to 0°C  Temperature = +50°C to +85°C                                                                                                                     | 0                        |       | 20                       | mV    |

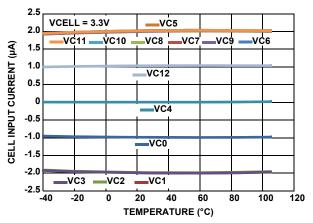

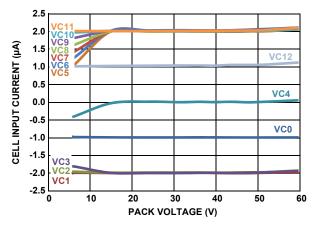

| Cell Input Current.                                                         | L                       | VCO input                                                                                                                                                                    | -2.0                     | -1    | -0.5                     | μΑ    |

| •                                                                           | IVCELL                  | VC1, VC2, VC3 inputs                                                                                                                                                         | -3.0                     | -2    | -0.9                     | μΑ    |

| Note: Cell accuracy figures assume a fixed $1k\Omega$ resistor is placed in |                         | VC4 input                                                                                                                                                                    | -0.8                     | 0     | 0.9                      | μА    |

| series with each VCn pin (n = 0                                             |                         | VC5, VC6, VC7, VC8, VC9, VC10, VC11 inputs                                                                                                                                   | 0.5                      | 2     | 3.2                      |       |

| to 12)                                                                      |                         | VC12 input                                                                                                                                                                   |                          | 1     | 2.0                      | μΑ    |

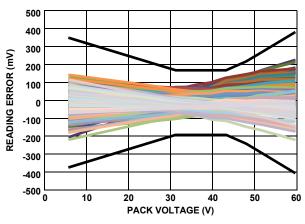

| V <sub>BAT</sub> Monitor Voltage Resolution                                 | VBAT <sub>RES</sub>     | ADC resolution referred to input (V <sub>BAT</sub> ) level. 14b unsigned number. Full scale value = 79.67V.                                                                  | 0.4                      | 4.863 | 2.0                      | mV    |

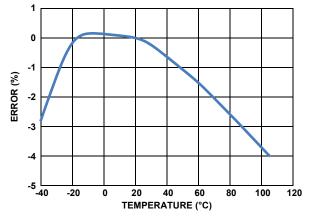

| V <sub>BAT</sub> Monitor Voltage Error                                      | ΔV <sub>BAT</sub>       | Temperature = 0°C to +50°C,<br>Measured at V <sub>BAT</sub> = 31.2V to 43.2V                                                                                                 | -180                     |       | 180                      | mV    |

|                                                                             |                         | Temperature = 0 °C to +50 °C,<br>Measured at V <sub>BAT</sub> = 24V to 48V                                                                                                   | -230                     |       | 230                      | mV    |

|                                                                             |                         | Temperature = 0 °C to +50 °C,<br>Measured at V <sub>BAT</sub> = 6V to 59.4V                                                                                                  | -390                     |       | 390                      | mV    |

|                                                                             |                         | Temperature = -40 °C to +85 °C,<br>Measured at V <sub>BAT</sub> = 31.2V to 39.6V                                                                                             | -320                     |       | 320                      | mV    |

|                                                                             |                         | Temperature = -40 °C to +85 °C,<br>Measured at V <sub>BAT</sub> = 6V to 48V                                                                                                  | -440                     |       | 440                      | mV    |

|                                                                             |                         | Temperature = -40 °C to +85 °C,<br>Measured at V <sub>BAT</sub> = 6V to 59.4V                                                                                                | -650                     |       | 650                      | mV    |

| PARAMETER                                    | SYMBOL               | TEST CONDITIONS                                                                                                                                                          | MIN<br>( <u>Note 7</u> ) | TYP  | MAX<br>(Note 7) | UNITS   |

|----------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----------------|---------|

| External Temperature Monitoring<br>Regulator | V <sub>TEMP</sub>    | Voltage on TEMPREG output. (0 to 2mA load)                                                                                                                               | 2.475                    | 2.5  | 2.525           | V       |

| External Temperature Output Impedance        | R <sub>TEMP</sub>    | Output impedance at TEMPREG pin.                                                                                                                                         | 0                        | 0.1  | 0.2             | Ω       |

| External Temperature Input Range             | V <sub>EXT</sub>     | ExTn input voltage range. For design reference.                                                                                                                          | 0                        |      | 2344            | mV      |

| External Temperature Input Pull-up           | R <sub>EXTTEMP</sub> | Pull-up resistor to V <sub>TEMPREG</sub> applied to each input during measurement                                                                                        |                          | 10   |                 | МΩ      |

| External Temperature Input Offset            | V <sub>EXTOFF</sub>  | V <sub>BAT</sub> = 39.6V                                                                                                                                                 | -12                      |      | 12              | mV      |

| External Temperature Input INL               | V <sub>EXTINL</sub>  |                                                                                                                                                                          | -0.65                    |      | 0.65            | mV      |

| External Temperature Input Gain<br>Error     | V <sub>EXTG</sub>    |                                                                                                                                                                          | -8                       |      | 18.5            | mV      |

| Internal Temperature Monitor Error           | V <sub>INTMON</sub>  |                                                                                                                                                                          |                          | ±10  |                 | °C      |

| Internal Temperature Monitor Resolution      | T <sub>INTRES</sub>  | Output resolution (LSB/ °C). 14b number.                                                                                                                                 |                          | 31.9 |                 | LSB/°C  |

| Internal Temperature Monitor<br>Output       | T <sub>INT25</sub>   | Output count at +25°C                                                                                                                                                    |                          | 9180 |                 | Decimal |

| OVER-TEMPERATURE PROTECTION                  | SPECIFICATION        | DNS                                                                                                                                                                      |                          |      |                 |         |

| Internal Temperature Limit<br>Threshold      | T <sub>INTSD</sub>   | Balance stops and auto scan stops. Temperature rising or falling.                                                                                                        |                          | 150  |                 | °C      |

| External Temperature Limit<br>Threshold      | т <sub>хт</sub>      | Corresponding to OV (min) and V <sub>TEMPREG</sub> (max) External temperature input voltages higher than 15/16 V <sub>TEMPREG</sub> are registered as open input faults. | 0                        |      | 16383           | Decimal |

| FAULT DETECTION SYSTEM SPECIFI               | CATIONS              |                                                                                                                                                                          |                          |      |                 |         |

| Undervoltage Threshold                       | $v_{UV}$             | Programmable. Corresponding to OV (min) and 5V (max)                                                                                                                     | 0                        |      | 8191            | Decimal |

| Overvoltage Threshold                        | v <sub>ov</sub>      | Programmable. Corresponding to OV (min) and 5V (max)                                                                                                                     | 0                        |      | 8191            | Decimal |

| V3P3 Power-good Window                       | V <sub>3PH</sub>     | 3.3V Power-good window high threshold.<br>V <sub>BAT</sub> = 39.6V                                                                                                       | 3.7                      | 3.90 | 4.05            | V       |

|                                              | V <sub>3PL</sub>     | 3.3V Power-good window low threshold.<br>V <sub>BAT</sub> = 39.6V                                                                                                        | 2.5                      | 2.65 | 2.8             | V       |

| V2P5 Power-good Window                       | V <sub>2PH</sub>     | 2.5V Power-good window high threshold.<br>V <sub>BAT</sub> = 39.6V                                                                                                       | 2.55                     | 2.7  | 2.9             | V       |

|                                              | V <sub>2PL</sub>     | 2.5V Power-good window low threshold.<br>V <sub>BAT</sub> = 39.6V                                                                                                        | 1.90                     | 2.0  | 2.15            | V       |

| VCC Power-good Window                        | V <sub>VCCH</sub>    | VCC Power-good window high threshold.  V <sub>BAT</sub> = 39.6V                                                                                                          | 3.6                      | 3.75 | 4.0             | V       |

|                                              | V <sub>VCCL</sub>    | VCC Power-good window low threshold. VBAT = 39.6V                                                                                                                        | 2.55                     | 2.7  | 2.85            | V       |

| V <sub>REF</sub> Power-good Window           | V <sub>RPH</sub>     | V <sub>REF</sub> Power-good window high threshold.<br>V <sub>BAT</sub> = 39.6V                                                                                           | 2.525                    | 2.7  | 2.9             | V       |

|                                              | V <sub>RPL</sub>     | V <sub>REF</sub> Power-good window low threshold.<br>V <sub>BAT</sub> = 39.6V                                                                                            | 2.0                      | 2.30 | 2.50            | V       |

| PARAMETER                                          | SYMBOL               | TEST CONDITIONS                                                                                                                                                                                             | MIN<br>( <u>Note 7</u> ) | TYP  | MAX<br>( <u>Note 7</u> ) | UNITS |

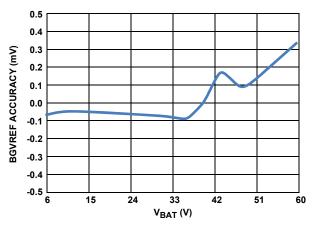

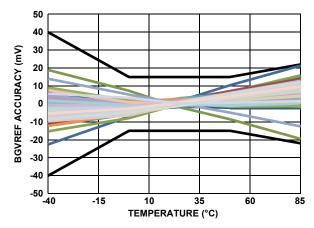

|----------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| V <sub>REF</sub> Reference Accuracy Error          | V <sub>RACC</sub>    | V <sub>REF</sub> value calculated using stored coefficients.  V <sub>BAT</sub> = 39.6V, V <sub>REF</sub> typical = 2.5V (See "Voltage Reference Check Calculation" on page 86.)  Temperature = 0°C to +50°C | -15                      |      | 15                       | mV    |

|                                                    |                      | Temperature = -40°C to 0°C                                                                                                                                                                                  | -40                      |      | 40                       | mV    |

|                                                    |                      | Temperature = +50°C to +85°C                                                                                                                                                                                | -22                      |      | 22                       | mV    |

| Voltage Reference Check Timeout                    | t <sub>VREF</sub>    | Time to check voltage reference value from power-on, enable or wake up                                                                                                                                      |                          | 20   |                          | ms    |

| Oscillator Check Timeout                           | tosc                 | Time to check main oscillator frequency from power-on, enable or wake up                                                                                                                                    |                          | 20   |                          | ms    |

| Oscillator Check Filter Time                       | toscf                | Minimum duration of fault required for detection                                                                                                                                                            |                          | 100  |                          | ms    |

| CELL OPEN WIRE DETECTION                           |                      |                                                                                                                                                                                                             |                          |      |                          |       |

| (See sections <u>"Scan Wires" on page</u>          | ge 22, <u>"ISCN</u>  | PIN37, PIN39" on page 30, and "Open Wire Test" on page                                                                                                                                                      | age 45.)                 |      |                          |       |

| Open Wire Current                                  | low                  | ISCN bit = 0; V <sub>BAT</sub> = 39.6V                                                                                                                                                                      | 0.125                    | 0.15 | 0.175                    | mA    |

|                                                    |                      | ISCN bit = 1; V <sub>BAT</sub> = 39.6V                                                                                                                                                                      | 0.85                     | 1.0  | 1.15                     | mA    |

| Open Wire Detection Time                           | tow                  | Open wire current source "on" time                                                                                                                                                                          |                          | 4.6  |                          | ms    |

| Open VCO Detection Threshold                       | V <sub>VCO</sub>     | CELL1 negative terminal (with respect to VSS) V <sub>BAT</sub> = 39.6V                                                                                                                                      | 1.2                      | 1.5  | 1.8                      | V     |

| Open VC1 Detection Threshold                       | V <sub>VC1</sub>     | CELL1 positive terminal (with respect to VSS) V <sub>BAT</sub> = 39.6V                                                                                                                                      | 0.6                      | 0.7  | 0.8                      | V     |

| Primary Detection Threshold, VC2 to VC12           | V <sub>VC2_12P</sub> | V(VC(n - 1)) - V(VCn), n = 2 to 12<br>V <sub>BAT</sub> = 39.6V                                                                                                                                              | -2                       | -1.5 | 0                        | V     |

| Secondary Detection Threshold,<br>VC2 to VC12      | V <sub>VC2_12S</sub> | Via ADC. VC2 to VC12 only<br>V <sub>BAT</sub> = 39.6V                                                                                                                                                       | -100                     | -30  | 50                       | mV    |

| Open V <sub>BAT</sub> Fault Detection<br>Threshold | V <sub>VBO</sub>     | VC12 - V <sub>BAT</sub>                                                                                                                                                                                     |                          | 200  |                          | m۷    |

| Open VSS Fault Detection<br>Threshold              | V <sub>VSSO</sub>    | VSS - VCO                                                                                                                                                                                                   |                          | 250  |                          | mV    |

| MEASUREMENT FUNCTION TIMING                        | (Note 8)             |                                                                                                                                                                                                             |                          |      |                          |       |

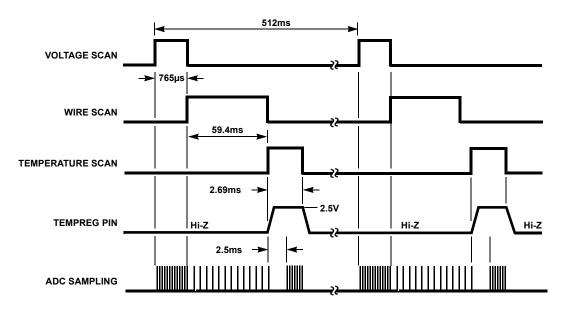

| Cell Sample Time Start                             |                      | Time to sample the first cell (CELL12) following $\overline{\text{CS}}$ going High. Scan voltages command                                                                                                   |                          | 65   | 71.5                     | μs    |

| Cell Sample Time Duration                          |                      | Time to scan all 12 cells (sample of CELL12 to sample of CELL1) scan voltages command.                                                                                                                      |                          | 233  | 257                      | μs    |

| Scan Voltages Processing Time                      |                      | Time from start of scan to registers loaded to DATA READY going low                                                                                                                                         |                          | 770  | 847                      | μs    |

| Scan Temperatures Processing<br>Time               |                      | Time from start of scan to registers loaded to DATA READY going low                                                                                                                                         |                          | 2690 | 2959                     | μs    |

| Scan Mixed Processing Time                         |                      | Time from start of scan to registers loaded to DATA READY going low                                                                                                                                         |                          | 830  | 913                      | μs    |

| Scan Wires Processing Time                         |                      | Time from start of scan to registers loaded to DATA READY going low                                                                                                                                         |                          | 59.4 | 65.3                     | ms    |

| Scan All Processing Time                           |                      | Time from start of scan to registers loaded to DATA READY going low                                                                                                                                         |                          | 63.2 | 69.5                     | ms    |

| PARAMETER                                           | SYMBOL            | TEST CONDITIONS                                                                                                   | MIN<br>( <u>Note 7</u> ) | TYP  | MAX<br>(Note 7) | UNITS |

|-----------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----------------|-------|

| Measure Cell Voltage Processing<br>Time             |                   | Time from start of measurement to register(s) loaded to DATA READY going low                                      |                          | 180  | 198             | μs    |

| Measure V <sub>BAT</sub> Voltage Processing<br>Time |                   | Time from start of measurement to register(s) loaded to DATA READY going low                                      |                          | 130  | 143             | μs    |

| Measure Internal Temperature<br>Processing Time     |                   | Time from start of measurement to register(s) loaded to DATA READY going low                                      |                          | 110  | 121             | μs    |

| Measure External Temperature Input Processing Time  |                   | Time from start of measurement to register(s) loaded to DATA READY going low                                      |                          | 2520 | 2772            | μs    |

| Measure Secondary Voltage<br>Reference Time         |                   | Time from start of measurement to register(s) loaded to DATA READY going low                                      |                          | 2520 | 2772            | μs    |

| CELL BALANCE OUTPUT SPECIFICA                       | TIONS             |                                                                                                                   |                          |      |                 |       |

| Cell Balance Pin Output<br>Impedance                | R <sub>CBL</sub>  | CBn output off impedance<br>between CB(n) to VC(n-1): cells 1 to 9 and<br>between CB(n) to VC(n): cells 10 to 12. | 3                        | 4    | 5               | ΜΩ    |

| Cell Balance Output Current                         | I <sub>CBH1</sub> | CBn output on. (CB1-CB9); V <sub>BAT</sub> = 39.6V; device sinking current.                                       | -28                      | -25  | -21             | μΑ    |

|                                                     | I <sub>CBH2</sub> | CBn output on. (CB10-CB12); V <sub>BAT</sub> = 39.6V; device sourcing current.                                    | 21                       | 25   | 28              | μΑ    |

| Cell Balance Output Leakage in<br>Shutdown          | I <sub>CBSD</sub> | EN = GND. V <sub>BAT</sub> = 39.6V.                                                                               | -500                     | 10   | 700             | nA    |

| External Cell Balance FET Gate<br>Voltage           | VGS               | CBn Output on; External 320k $\Omega$ between VCn and CBn (n = 10 to 12) and between CBn and VCn-1 (n = 1 to 9)   | 7.05                     | 8.0  | 8.95            | V     |

| Internal Cell Balance Output<br>Clamp               | VCBCL             | $I_{CB} = 100  \mu A.$                                                                                            | 8.9                      |      |                 | V     |

| LOGIC INPUTS: SCLK, CS, DIN                         |                   |                                                                                                                   |                          |      | -               |       |

| Low Level Input Voltage                             | VIL               |                                                                                                                   |                          |      | 0.8             | V     |

| High Level Input Voltage                            | VIH               |                                                                                                                   | 1.75                     |      |                 | V     |

| Input Hysteresis                                    | VHYS              |                                                                                                                   | 100                      |      |                 | mV    |

| Input Current                                       | IIN               | 0V < V <sub>IN</sub> < V3P3                                                                                       | -1                       |      | +1              | μΑ    |

| Input Capacitance                                   | CIN               |                                                                                                                   |                          |      | 10              | pF    |

| LOGIC INPUTS: EN, COMMS SELECT                      | T1, COMMS S       | ELECT2, COMMS RATE 0, COMMS RATE 1                                                                                |                          |      |                 |       |

| Low Level Input Voltage                             | VIL               |                                                                                                                   |                          |      | 0.3*V3P3        | V     |

| High Level Input Voltage                            | VIH               |                                                                                                                   | 0.7*V3P3                 |      |                 | V     |

| Input Hysteresis                                    | VHYS              |                                                                                                                   | 0.05*V3P3                |      |                 | V     |

| Input Current                                       | IIN               | 0V < V <sub>IN</sub> < V3P3                                                                                       | -1                       |      | +1              | μA    |

| Input Capacitance                                   | CIN               |                                                                                                                   |                          |      | 10              | pF    |

| LOGIC OUTPUTS: DOUT, FAULT, DAT                     | A READY           | 1                                                                                                                 |                          |      | 1               |       |

| Low Level Output Voltage                            | VOL1              | At 3mA sink current                                                                                               | 0                        |      | 0.4             | V     |

|                                                     | VOL2              | At 6mA sink current                                                                                               | 0                        |      | 0.6             | V     |

| High Level Output Voltage                           | VOH1              | At 3mA source current                                                                                             | V3P3 - 0.4V              |      | V3P3            | V     |

|                                                     | VOH2              | At 6mA source current                                                                                             | V3P3 - 0.6V              |      | V3P3            | V     |

# **Electrical Specifications** $V_{BAT} = 6 \text{ to } 60V$ , $T_A = -40 \,^{\circ}\text{C}$ to $+85 \,^{\circ}\text{C}$ , unless otherwise specified. **Boldface limits apply across the operating** temperature range, $-40 \,^{\circ}\text{C}$ to $+85 \,^{\circ}\text{C}$ . (Continued)

| PARAMETER                                 | SYMBOL               | TEST CONDITIONS                                                                                                         | MIN<br>(Note 7) | TYP                 | MAX<br>(Note 7) | UNITS |

|-------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|-----------------|-------|

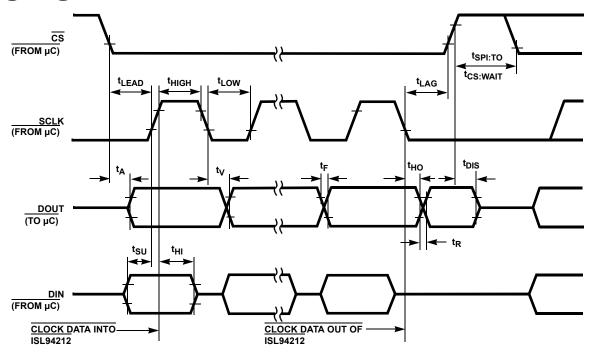

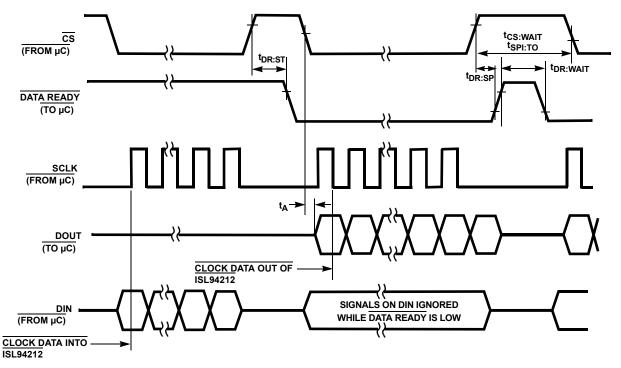

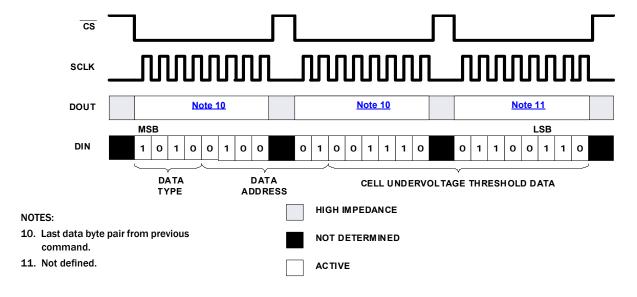

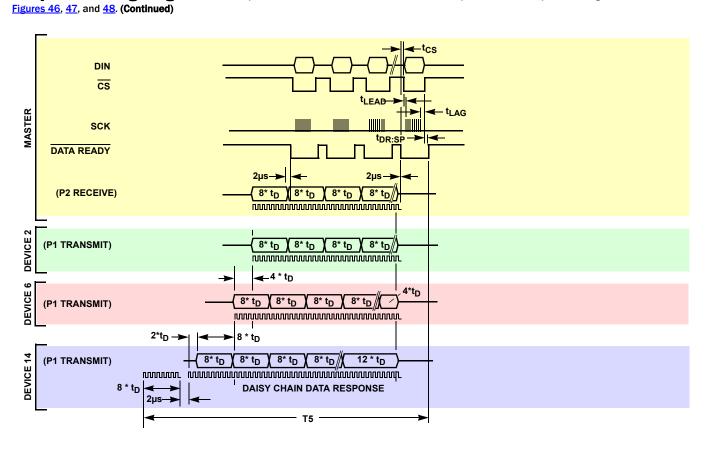

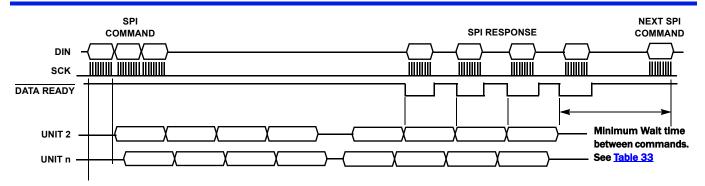

| SPI INTERFACE TIMING (See Figures 2       | 2 and 3)             |                                                                                                                         |                 |                     |                 |       |

| SCLK Clock Frequency                      | f <sub>SCLK</sub>    |                                                                                                                         |                 |                     | 2               | MHz   |

| Pulse Width of Input Spikes<br>Suppressed | t <sub>IN1</sub>     |                                                                                                                         | 50              |                     | 200             | ns    |

| Enable Lead Time                          | t <sub>LEAD</sub>    | Chip select low to ready to receive clock data                                                                          | 200             |                     |                 | ns    |

| Clock High Time                           | t <sub>HIGH</sub>    |                                                                                                                         | 200             |                     |                 | ns    |

| Clock Low Time                            | t <sub>LOW</sub>     |                                                                                                                         | 200             |                     |                 | ns    |

| Enable Lag Time                           | t <sub>LAG</sub>     | Last data read clock edge to chip select high.                                                                          | 250             |                     |                 | ns    |

| CHIP SELECT High Time                     | t <sub>CS:WAIT</sub> | Minimum high time for $\overline{\text{CS}}$ between bytes.                                                             | 200             |                     |                 | ns    |

| Slave Access Time                         | t <sub>A</sub>       | Chip select low to DOUT active.                                                                                         |                 |                     | 200             | ns    |

| Data Valid Time                           | t <sub>V</sub>       | Clock low to DOUT valid.                                                                                                |                 |                     | 350             | ns    |

| Data Output Hold Time                     | t <sub>HO</sub>      | Data hold time after falling edge of SCLK.                                                                              | 0               |                     |                 | ns    |

| DOUT Disable Time                         | t <sub>DIS</sub>     | DOUT disabled following rising edge of $\overline{\text{CS}}$ .                                                         |                 |                     | 240             | ns    |

| Data Setup Time                           | t <sub>SU</sub>      | Data input valid prior to rising edge of SCLK.                                                                          | 100             |                     |                 | ns    |

| Data Input Hold Time                      | t <sub>HI</sub>      | Data input to remain valid following rising edge of SCLK.                                                               | 80              |                     |                 | ns    |

| Data Ready Start Delay Time               | t <sub>DR:ST</sub>   | Chip select high to Data Ready low.                                                                                     | 100             |                     |                 | ns    |

| Data Ready Stop Delay Time                | t <sub>DR:SP</sub>   | Chip select high to Data Ready high.                                                                                    |                 |                     | 750             | ns    |

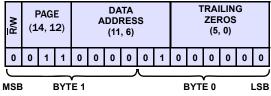

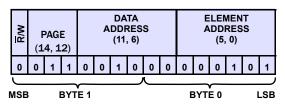

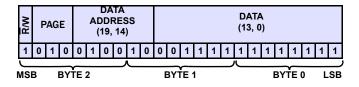

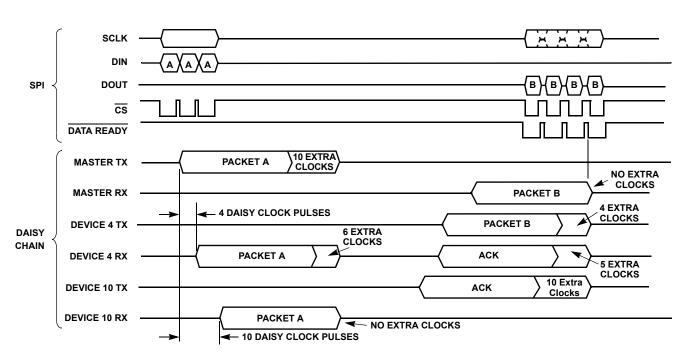

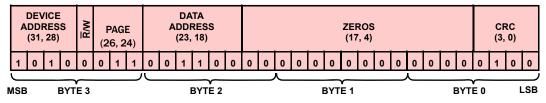

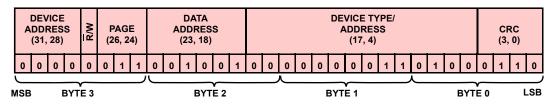

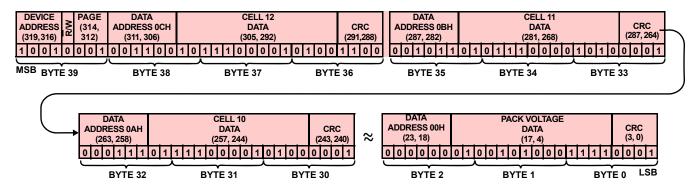

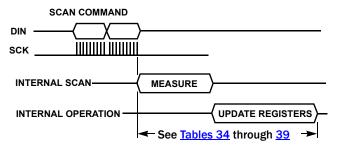

| Data Ready High Time                      | t <sub>DR:WAIT</sub> | Time between bytes.                                                                                                     | 0.6             |                     |                 | μs    |