# 1.5 A, 260 kHz and 520 kHz, Low Voltage Buck Regulators with External Bias or Synchronization Capability

The CS5141X products are 1.5 A buck regulator ICs. These devices are fixed-frequency operating at 260 kHz and 520 kHz. The regulators use the  $V^{2\text{TM}}$  control architecture to provide unmatched transient response, the best overall regulation and the simplest loop compensation for today's high-speed logic. These products accommodate input voltages from 4.5 V to 40 V.

The CS51411 and CS51413 contain synchronization circuitry. The CS51412 and CS51414 have the option of powering the controller from an external 3.3 V to 6.0 V supply in order to improve efficiency, especially in high input voltage, light load conditions.

The on-chip NPN transistor is capable of providing a minimum of 1.5 A of output current, and is biased by an external "boost" capacitor to ensure saturation, thus minimizing on-chip power dissipation. Protection circuitry includes thermal shutdown, cycle-by-cycle current limiting and frequency foldback. The CS51411 and CS51413 are functionally pin-compatible with the LT1375. The CS51412 and CS51414 are functionally pin-compatible with the LT1376.

#### **Features**

- V<sup>2</sup> Architecture Provides Ultrafast Transient Response, Improved Regulation and Simplified Design

- 2.0% Error Amp Reference Voltage Tolerance

- Switch Frequency Decrease of 4:1 in Short Circuit Conditions Reduces Short Circuit Power Dissipation

- BOOST Lead Allows "Bootstrapped" Operation to Maximize Efficiency

- Sync Function for Parallel Supply Operation or Noise Minimization

1

- Shutdown Lead Provides Power-Down Option

- 85 µA Quiescent Current During Power-Down

- Thermal Shutdown

- Soft-Start

- Pin-Compatible with LT1375 and LT1376

- Pb-Free Packages are Available

## ON Semiconductor®

http://onsemi.com

### MARKING DIAGRAMS

5141x = Device Codex = 1, 2, 3 or 4

A = Assembly Location

L, WL = Wafer Lot Y, YY = Year W, WW = Work Week

> y = E or G = Pb-Free Package

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 18 of this data sheet.

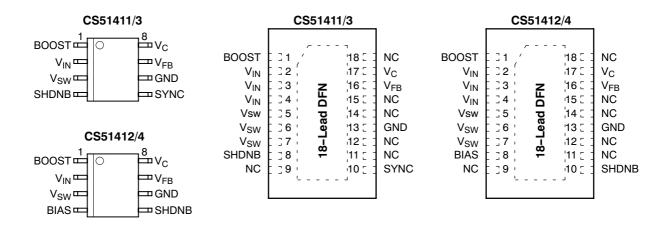

## **PIN CONNECTIONS**

## PACKAGE PIN DESCRIPTION

| SOIC-8<br>Package Pin #                          | DFN18<br>Package Pin #                            | Pin Symbol      | Function                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------|---------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                | 1                                                 | BOOST           | The BOOST pin provides additional drive voltage to the on-chip NPN power transistor. The resulting decrease in switch on voltage increases efficiency.                                                                                                                                                                                               |

| 2                                                | 2, 3, 4                                           | V <sub>IN</sub> | This pin is the main power input to the IC.                                                                                                                                                                                                                                                                                                          |

| 3                                                | 5, 6, 7                                           | V <sub>SW</sub> | This is the connection to the emitter of the on-chip NPN power transistor and serves as the switch output to the inductor. This pin may be subjected to negative voltages during switch off-time. A catch diode is required to clamp the pin voltage in normal operation. This node can stand –1.0 V for less than 50 ns during switch node flyback. |

| 4<br>(CS51412/CS51414)                           | 8                                                 | BIAS            | The BIAS pin connects to the on-chip power rail and allows the IC to run most of its internal circuitry from the regulated output or another low voltage supply to improve efficiency. The BIAS pin is left floating if this feature is not used.                                                                                                    |

| 5<br>(CS51411/CS51413)                           | 10                                                | SYNC            | This pin provides the synchronization input.                                                                                                                                                                                                                                                                                                         |

| 5<br>(CS51412/CS51414)<br>4<br>(CS51411/CS51413) | 10<br>(CS51412/CS51414)<br>8<br>(CS51411/CS51413) | SHDNB           | The shutdown pin is active low and TTL compatible. The IC goes into sleep mode, drawing less than 85 $\mu\text{A}$ when the pin voltage is pulled below 1.0 V. This pin should be left floating in normal position.                                                                                                                                  |

| 6                                                | 13                                                | GND             | Power return connection for the IC.                                                                                                                                                                                                                                                                                                                  |

| 7                                                | 16                                                | V <sub>FB</sub> | The FB pin provides input to the inverting input of the error amplifier. If $V_{FB}$ is lower than 0.29 V, the oscillator frequency is divided by four, and current limit folds back to about 1 A. These features protect the IC under severe overcurrent or short circuit conditions.                                                               |

| 8                                                | 17                                                | V <sub>C</sub>  | The V <sub>C</sub> pin provides a connection point to the output of the error amplifier and input to the PWM comparator. Driving of this pin should be avoided because on-chip test circuitry becomes active whenever current exceeding 0.5 mA is forced into the IC.                                                                                |

| -                                                | 9, 11, 12, 14, 15, 18                             | NC              | No Connection                                                                                                                                                                                                                                                                                                                                        |

## **PRODUCT SELECTION GUIDE**

| Part Number | Frequency | Temperature Range | Bias/Sync |

|-------------|-----------|-------------------|-----------|

| CS51411E    | 260 kHz   | -40°C to 85°C     | Sync      |

| CS51411G    | 260 kHz   | 0°C to 70°C       | Sync      |

| CS51412E    | 260 kHz   | -40°C to 85°C     | Bias      |

| CS51412G    | 260 kHz   | 0°C to 70°C       | Bias      |

| CS51413E    | 520 kHz   | -40°C to 85°C     | Sync      |

| CS51413G    | 520 kHz   | 0°C to 70°C       | Sync      |

| CS51414E    | 520 kHz   | -40°C to 85°C     | Bias      |

| CS51414G    | 520 kHz   | 0°C to 70°C       | Bias      |

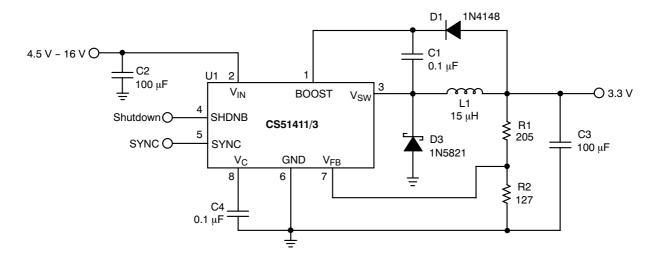

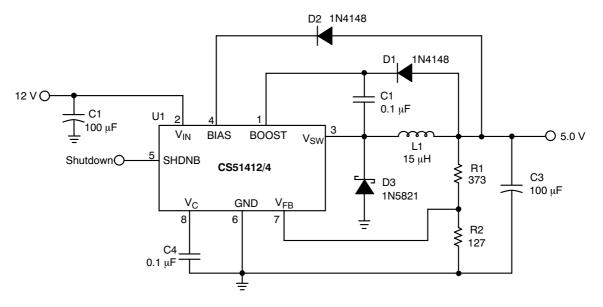

Figure 1. Application Diagram, 4.5 V - 16 V to 3.3 V @ 1.0 A Converter

#### **MAXIMUM RATINGS**

| Rating                                               |                                                                                                 | Value                            | Unit |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------|------|

| Operating Junction Temperature Range, T <sub>J</sub> |                                                                                                 | -40 to 150                       | °C   |

| Lead Temperature Soldering:                          | Reflow for Leaded: (SMD styles only) (Note 1)<br>Reflow for Pb-Free: (SMD styles only) (Note 2) | 230 peak<br>260 peak<br>(Note 3) | °C   |

| Storage Temperature Range, T <sub>S</sub>            |                                                                                                 | -65 to +150                      | °C   |

| ESD Damage Threshold (Human Body Model)              |                                                                                                 | 2.0                              | kV   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. 60-150 second above 183°C, 30 second maximum at peak.

- 2. 60-150 second above 217°C, 40 second maximum at peak.

- 3. +5°C/0°C allowable conditions, applies to both Pb and Pb-Free Devices.

## **MAXIMUM RATINGS**

| Pin Name        | V <sub>Max</sub> | V <sub>MIN</sub>         | I <sub>SOURCE</sub> | I <sub>SINK</sub> |

|-----------------|------------------|--------------------------|---------------------|-------------------|

| V <sub>IN</sub> | 40 V             | -0.3 V                   | N/A                 | 4.0 A             |

| BOOST           | 40 V             | -0.3 V                   | N/A                 | 100 mA            |

| V <sub>SW</sub> | 40 V             | -0.6 V/-1.0 V, t < 50 ns | 4.0 A               | 10 mA             |

| V <sub>C</sub>  | 7.0 V            | -0.3 V                   | 1.0 mA              | 1.0 mA            |

| SHDNB           | 7.0 V            | -0.3 V                   | 1.0 mA              | 1.0 mA            |

| SYNC            | 7.0 V            | -0.3 V                   | 1.0 mA              | 1.0 mA            |

| BIAS            | 7.0 V            | -0.3 V                   | 1.0 mA              | 50 mA             |

| V <sub>FB</sub> | 7.0 V            | -0.3 V                   | 1.0 mA              | 1.0 mA            |

| GND             | 7.0 V            | -0.3 V                   | 50 mA               | 1.0 mA            |

$\begin{tabular}{ll} \textbf{ELECTRICAL CHARACTERISTICS} & (-40^{\circ}C < T_{J} < 125^{\circ}C \ (CS51411E/2E/3E/4E); \ -40^{\circ}C < T_{A} < 85^{\circ}C \ (CS51411E/2E/3E/4E); \\ 0^{\circ}C < T_{A} < 70^{\circ}C \ (CS51411G/2G/3G/4G), \ 4.5 \ V < V_{IN} < 40 \ V; \ unless otherwise specified.) \\ \end{tabular}$

| Characteristic                               | Test Conditions                                                                                            | Min       | Тур      | Max        | Unit           |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------|----------|------------|----------------|

| Oscillator                                   |                                                                                                            |           |          |            |                |

| Operating Frequency                          | CS51411/CS51412                                                                                            | 224       | 260      | 296        | kHz            |

| Operating Frequency                          | CS51413/CS51414                                                                                            | 446       | 520      | 594        | kHz            |

| Frequency Line Regulation                    | -                                                                                                          | -         | 0.05     | 0.15       | %/V            |

| Maximum Duty Cycle                           | -                                                                                                          | 85        | 90       | 95         | %              |

| V <sub>FB</sub> Frequency Foldback Threshold | -                                                                                                          | 0.29      | 0.32     | 0.36       | V              |

| PWM Comparator                               |                                                                                                            |           |          |            |                |

| Slope Compensation Voltage                   | CS51411/CS51412, Fix V <sub>FB,</sub> ΔV <sub>C</sub> /ΔT <sub>ON</sub><br>CS51413/CS51414                 | 8.0<br>25 | 17<br>50 | 26<br>75   | mV/μs<br>mV/μs |

| Minimum Output Pulse Width                   | CS51411/CS51412, V <sub>FB</sub> to V <sub>SW</sub><br>CS51413/CS51414, V <sub>FB</sub> to V <sub>SW</sub> |           | 150<br>- | 300<br>230 | ns<br>ns       |

| Power Switch                                 |                                                                                                            |           |          |            |                |

| Current Limit                                | V <sub>FB</sub> > 0.36 V                                                                                   | 1.6       | 2.3      | 3.0        | Α              |

| Foldback Current                             | V <sub>FB</sub> < 0.29 V                                                                                   | 0.9       | 1.5      | 2.1        | Α              |

| Saturation Voltage                           | I <sub>OUT</sub> = 1.5 A, V <sub>BOOST</sub> = V <sub>IN</sub> + 2.5 V                                     | 0.4       | 0.7      | 1.0        | V              |

| Current Limit Delay                          | (Note 4)                                                                                                   | -         | 120      | 160        | ns             |

| Error Amplifier                              |                                                                                                            |           |          |            |                |

| Internal Reference Voltage                   | -                                                                                                          | 1.244     | 1.270    | 1.296      | V              |

| Reference PSRR                               | (Note 4)                                                                                                   | -         | 40       | _          | dB             |

| FB Input Bias Current                        | -                                                                                                          | -         | 0.02     | 0.1        | μΑ             |

| Output Source Current                        | V <sub>C</sub> = 1.270 V, V <sub>FB</sub> = 1.0 V                                                          | 15        | 25       | 35         | μΑ             |

| Output Sink Current                          | V <sub>C</sub> = 1.270 V, V <sub>FB</sub> = 2.0 V                                                          | 15        | 25       | 35         | μΑ             |

| Output High Voltage                          | V <sub>FB</sub> = 1.0 V                                                                                    | 1.39      | 1.46     | 1.53       | V              |

| Output Low Voltage                           | V <sub>FB</sub> = 2.0 V                                                                                    | 5.0       | 20       | 60         | mV             |

| Unity Gain Bandwidth                         | (Note 4)                                                                                                   | -         | 500      | -          | kHz            |

| Open Loop Amplifier Gain                     | (Note 4)                                                                                                   | -         | 70       | -          | dB             |

| Amplifier Transconductance                   | (Note 4)                                                                                                   | -         | 6.4      | -          | mA/V           |

<sup>4.</sup> Guaranteed by design, not 100% tested in production.

$\begin{tabular}{ll} \textbf{ELECTRICAL CHARACTERISTICS} & (-40^{\circ}C < T_{J} < 125^{\circ}C \ (CS51411E/2E/3E/4E); \ -40^{\circ}C < T_{A} < 85^{\circ}C \ (CS51411E/2E/3E/4E); \ 0^{\circ}C < T_{A} < 70^{\circ}C \ (CS51411G/2G/3G/4G), \ 4.5 \ V < V_{IN} < 40 \ V; \ unless otherwise specified.) \end{tabular}$

| Characteristic              | Test Conditions                                      | Min      | Тур        | Max        | Unit                     |

|-----------------------------|------------------------------------------------------|----------|------------|------------|--------------------------|

| Sync                        | •                                                    |          |            |            | -                        |

| Sync Frequency Range        | CS51411/CS51412                                      | 305      | _          | 470        | kHz                      |

| Sync Frequency Range        | CS51413/CS51414                                      | 575      | -          | 880        | kHz                      |

| Sync Pin Bias Current       | V <sub>SYNC</sub> = 0 V<br>V <sub>SYNC</sub> = 5.0 V | -<br>250 | 0.1<br>360 | 0.2<br>460 | μ <b>Α</b><br>μ <b>Α</b> |

| Sync Threshold Voltage      | -                                                    | 1.0      | 1.5        | 1.9        | V                        |

| Shutdown                    |                                                      |          |            |            |                          |

| Shutdown Threshold Voltage  | -                                                    | 1.0      | 1.3        | 1.6        | V                        |

| Shutdown Pin Bias Current   | V <sub>SHDNB</sub> = 0 V                             | 0.14     | 5.00       | 35         | μА                       |

| Thermal Shutdown            |                                                      |          |            |            |                          |

| Overtemperature Trip Point  | (Note 5)                                             | 175      | 185        | 195        | °C                       |

| Thermal Shutdown Hysteresis | (Note 5)                                             | -        | 42         | -          | °C                       |

| General                     |                                                      |          |            |            |                          |

| Quiescent Current           | I <sub>SW</sub> = 0 A                                | 3.0      | 4.0        | 6.25       | mA                       |

| Shutdown Quiescent Current  | V <sub>SHDNB</sub> = 0 V                             | 8.0      | 20         | 85         | μΑ                       |

| Boost Operating Current     | V <sub>BOOST</sub> - V <sub>SW</sub> = 2.5 V         | 6.0      | 15         | 40         | mA/A                     |

| Minimum Boost Voltage       | (Note 5)                                             | -        | -          | 2.5        | V                        |

| Startup Voltage             | -                                                    | 2.2      | 3.3        | 4.4        | V                        |

| Minimum Output Current      | -                                                    | -        | 7.0        | 12         | mA                       |

<sup>5.</sup> Guaranteed by design, not 100% tested in production.

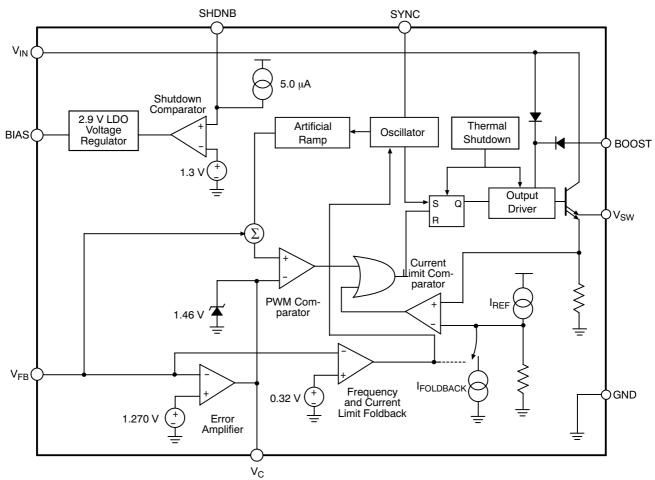

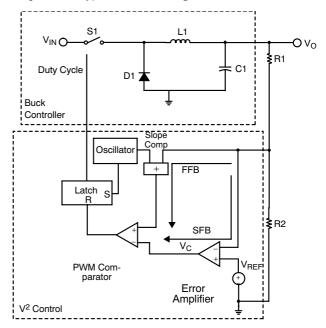

Figure 2. Block Diagram

#### **APPLICATIONS INFORMATION**

#### THEORY OF OPERATION

#### V<sup>2</sup> Control

The CS5141X family of buck regulators utilizes a V2 control technique and provides a high level of integration to enable high power density design optimization.

Every pulse width modulated controller configures basic control elements such that when connected to the feedback signal of a power converter, sufficient loop gain and bandwidth is available to regulate the voltage set point against line and load variations. The arrangement of these elements differentiates a voltage mode, or a current mode controller from a V2 device.

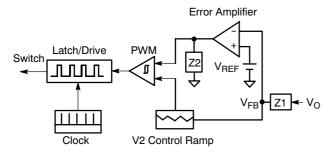

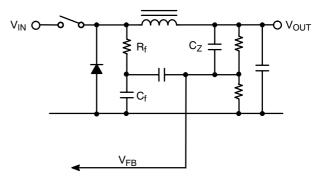

Figure 3 illustrates the basic architecture of a V2 controller.

Figure 3. V2 Control

In common with V mode or I mode, the feedback signal is compared with a reference voltage to develop an error signal which is fed to one input of the PWM. The second input to the PWM, however, is neither a fixed voltage ramp nor the switch current, but rather the feedback signal from the output of the converter. This feedback signal provides both DC information as well as AC information (the control ramp) for the converter to regulate its set point. The control architecture is known as V2 since both PWM inputs are derived from the converter's output voltage. This is a little misleading because the control ramp is typically generated from current information present in the converter.

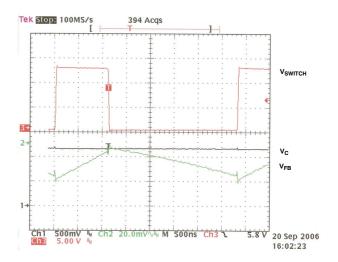

The feedback signal from the buck converter shown in Figure 4 is processed in one of two ways before being routed to the inputs of the PWM comparator. The Fast Feedback path (FFB) adds slope compensation to the feedback signal before passing it to one input of the PWM. The Slow Feedback path (SFB) compares the original feedback signal against a DC reference. The error signal generated at the output of the error amplifier VC is filtered by a low frequency pole before being routed to the second input of the PWM. Each switch cycle is initiated (S1 on), when the output latch is set by the oscillator. Each switch cycle terminates (S1 off), when the FFB signal (AC plus output DC) exceeds SFB (error DC), and the output latch is reset. In the event of a load transient, the FFB signal changes faster, in relation to the filtered SFB signal, causing duty

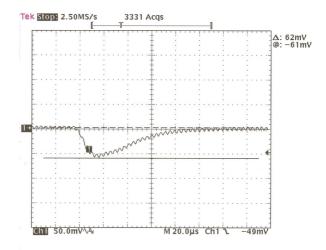

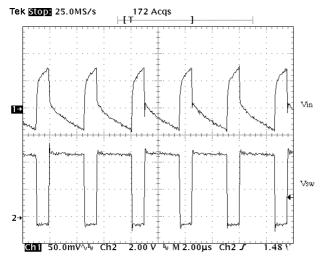

cycle modulation to occur. Actual oscilloscope waveforms taken from the converter show the switch node  $V_{SWITCH}$ , the error signal  $V_{C}$  and the feedback signal  $V_{FB}$  (AC component only) are shown in Figure 5.

Figure 4. Buck Converter with V2 Control

Figure 5.

In the event of a load transient, the FFB signal changes faster, in relation to the filtered SFB signal, causing duty cycle modulation to occur. By this means the converter's transient response time is independent of the error amplifier bandwidth. The error amplifier is used here to ensure excellent DC accuracy.

In order for the controller to operate optimally, a stable ramp is required at the feedback pin.

## **Control Ramp Generation**

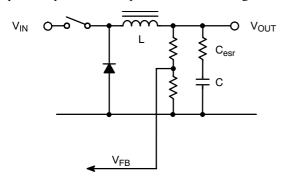

In original V2 designs, the control ramp VCR was generated from the converter's output ripple. Using a current derived ramp provides the same benefits as current mode, namely input feed forward, single pole output filter compensation and fast feedback following output load transients. Typically a tantalum or organic polymer capacitor is selected having a sufficiently large ESR component, relative to its capacitive and ESL ripple contributions, to ensure the control ramp was sensing inductor current and its amplitude was sufficient to maintain loop stability. This technique is illustrated in Figure 6.

Figure 6. Control Ramp Generated from Output

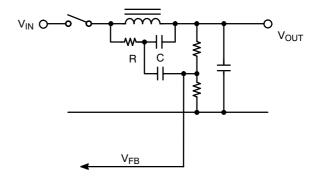

Advances in multilayer ceramic capacitor technology are such that MLCC's can provide a cost effective filter solution for low voltage (< 12 V), high frequency converters (>200 kHz). For example, a 10  $\mu F$  MLCC 16 V in a 805 SMT package has an ESR of 2 m $\Omega$  and an ESL of 100 nH. Using several MLCC's in parallel, connected to power and ground planes on a PCB with multiple vias, can provide a "near perfect" capacitor. Using this technique, output switching ripple below 10 mV can be readily obtained since parasitic ESR and ESL ripple contributions are nil. In this case, the control ramp is generated elsewhere in the circuit.

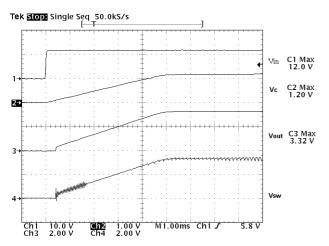

Ramp generation using dcr inductor current sensing, where the L/DCR time constant of the output inductor is matched with the CR time constant of the integrating network, is shown in Figure 7. The converter's transient response following a 1 A step load is shown in Figure 8. This transient response is indicative of a closed loop in excess of 10 kHz having good gain and phase margin in the frequency domain. Also note the amplitude of output switching ripple provided by just two  $10 \text{ }\mu\text{F}$  MLCC's.

Figure 7. Control Ramp Generated from DCR Inductor Sensing

Figure 8.

Ramp generation using a voltage feed forward technique is illustrated in Figure 9.

Figure 9. Control Ramp from Voltage Feed Forward

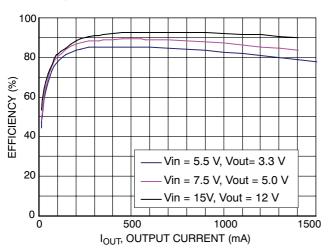

Some representative efficiency data is shown in Figure 10.

Figure 10. Efficiency versus Output Current

More detailed information is available in the ON Semiconductor application note AND8276/D on V2 and the CS5141x demonstration board number.

## **Error Amplifier**

The CS5141X has a transconductance error amplifier, whose noninverting input is connected to an Internal Reference Voltage generated from the on-chip regulator. The inverting input connects to the  $V_{FB}$  pin. The output of the error amplifier is made available at the  $V_{C}$  pin. A typical frequency compensation requires only a 0.1  $\mu F$  capacitor connected between the  $V_{C}$  pin and ground, as shown in Figure 1. This capacitor and error amplifier's output resistance (approximately 8.0  $M\Omega$ ) create a low frequency pole to limit the bandwidth. Since V2 control does not require a high bandwidth error amplifier, the frequency compensation is greatly simplified.

The  $V_{\rm C}$  pin is clamped below Output High Voltage. This allows the regulator to recover quickly from overcurrent or short circuit conditions.

## Oscillator and Sync Feature (CS51411 and CS51413 only)

The on-chip oscillator is trimmed at the factory and requires no external components for frequency control. The high switching frequency allows smaller external components to be used, resulting in a board area and cost savings. The tight frequency tolerance simplifies magnetic components election. The switching frequency is reduced to 25% of the nominal value when the  $V_{FB}$  pin voltage is below Frequency Foldback Threshold. In short circuit or overload conditions, this reduces the power dissipation of the IC and external components.

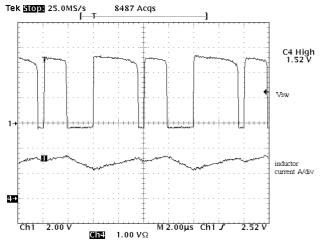

An external clock signal can sync CS51411/CS51414 to a higher frequency. The rising edge of the sync pulse turns on the power switch to start a new switching cycle, as shown in Figure 11. There is approximately 0.5  $\mu$ s delay between the rising edge of the sync pulse and rising edge of the V<sub>SW</sub> pin voltage. The sync threshold is TTL logic compatible, and duty cycle of the sync pulses can vary from 10% to 90%. The frequency foldback feature is disabled during the sync mode.

Figure 11. A CS51411 Buck Regulator is Synced by an External 350 kHz Pulse Signal

#### **Power Switch and Current Limit**

The collector of the built-in NPN power switch is connected to the  $V_{IN}$  pin, and the emitter to the  $V_{SW}$  pin. When the switch turns on, the  $V_{SW}$  voltage is equal to the  $V_{IN}$  minus switch Saturation Voltage. In the buck regulator, the  $V_{SW}$  voltage swings to one diode drop below ground when the power switch turns off, and the inductor current is commutated to the catch diode. Due to the presence of high pulsed current, the traces connecting the  $V_{SW}$  pin, inductor and diode should be kept as short as possible to minimize the noise and radiation. For the same reason, the input capacitor should be placed close to the  $V_{IN}$  pin and the anode of the diode.

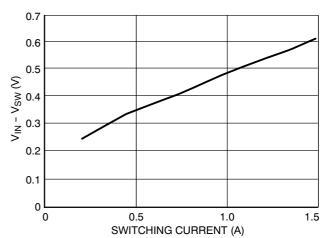

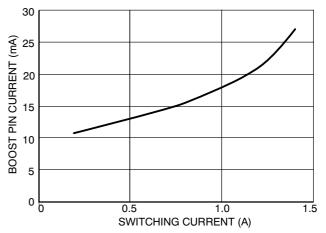

The saturation voltage of the power switch is dependent on the switching current, as shown in Figure 12.

Figure 12. The Saturation Voltage of the Power Switch Increases with the Conducting Current

Members of the CS5141X family contain pulse-by-pulse current limiting to protect the power switch and external components. When the peak of the switching current reaches the Current Limit, the power switch turns off after the Current Limit Delay. The switch will not turn on until the next switching cycle. The current limit threshold is

independent of switching duty cycle. The maximum load current, given by the following formula under continuous conduction mode, is less than the Current Limit due to the ripple current.

$$I_{O(MAX)} = I_{LIM} - \frac{V_{O}(V_{IN} - V_{O})}{2(L)(V_{IN})(f_S)}$$

where:

$f_S$  = switching frequency,

I<sub>LIM</sub> = current limit threshold,

$V_O$  = output voltage,

$V_{IN}$  = input voltage,

L = inductor value.

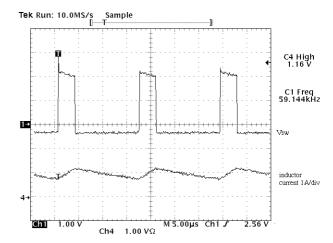

When the regulator runs undercurrent limit, the subharmonic oscillation may cause low frequency oscillation, as shown in Figure 13. Similar to current mode control, this oscillation occurs at the duty cycle greater than 50% and can be alleviated by using a larger inductor value. The current limit threshold is reduced to Foldback Current when the FB pin falls below Foldback Threshold. This feature protects the IC and external components under the power up or overload conditions.

Figure 13. The Regulator in Current Limit

## **BOOST Pin**

The BOOST pin provides base driving current for the power switch. A voltage higher than  $V_{IN}$  provides required headroom to turn on the power switch. This in turn reduces IC power dissipation and improves overall system efficiency. The BOOST pin can be connected to an external boost–strapping circuit which typically uses a  $0.1~\mu F$  capacitor and a 1N914 or 1N4148 diode, as shown in Figure 1. When the power switch is turned on, the voltage on the BOOST pin is equal to

$$V_{BOOST} = V_{IN} + V_{O} - V_{F}$$

where:

$V_F$  = diode forward voltage.

The anode of the diode can be connected to any DC voltage other than the regulated output voltage. However, the maximum voltage on the BOOST pin shall not exceed 40 V.

As shown in Figure 14, the BOOST pin current includes a constant 7.0 mA predriver current and base current proportional to switch conducting current. A detailed discussion of this current is conducted in Thermal Consideration section. A  $0.1 \, \mu F$  capacitor is usually adequate for maintaining the Boost pin voltage during the on time.

## BIAS Pin (CS51412 and CS51414 Only)

The BIAS pin allows a secondary power supply to bias the control circuitry of the IC. The BIAS pin voltage should be between 3.3 V and 6.0 V. If the BIAS pin voltage falls below that range, use a diode to prevent current drain from the BIAS pin. Powering the IC with a voltage lower than the regulator's input voltage reduces the IC power dissipation and improves energy transfer efficiency.

Figure 14. The Boost Pin Current Includes 7.0 mA

Predriver Current and Base Current when the Switch

is Turned On. The Beta Decline of the Power Switch

Further Increases the Base Current at High

Switching Current

#### Shutdown

The internal power switch will not turn on until the  $V_{\rm IN}$  pin rises above the Startup Voltage. This ensures no switching until adequate supply voltage is provided to the IC.

The IC enters a sleep mode when the SHDNB pin is pulled below Shutdown Threshold Voltage. In the sleep mode, the power switch keeps open and the supply current reduces to Shutdown Quiescent Current. This pin has internal pull-up current. So when this pin is not used, leave the SHDNB pin open.

#### Startup

During power up, the regulator tends to quickly charge up the output capacitors to reach voltage regulation. This gives rise to an excessive in-rush current which can be detrimental to the inductor, IC and catch diode. In  $V^2$  control, the compensation capacitor provides Soft–Start with no need for extra pin or circuitry. During the power up, the Output Source Current of the error amplifier charges the compensation capacitor which forces  $V_C$  pin and thus output voltage ramp up gradually.

The Soft-Start duration can be calculated by

$$T_{SS} = \frac{V_C \times C_{COMP}}{I_{SOURCE}}$$

where:

$V_C = V_C$  pin steady-state voltage, which is approximately equal to error amplifier's reference voltage.

$C_{COMP}$  = Compensation capacitor connected to the  $V_{C}$  pin  $I_{SOURCE}$  = Output Source Current of the error amplifier.

Using a 0.1  $\mu F$  C<sub>COMP</sub>, the calculation shows a T<sub>SS</sub> over 5.0 ms which is adequate to avoid any current stresses. Figure 15 shows the gradual rise of the V<sub>C</sub>, V<sub>O</sub> and envelope of the V<sub>SW</sub> during power up. There is no voltage overshoot after the output voltage reaches the regulation. If the supply voltage rises slower than the V<sub>C</sub> pin, output voltage may overshoot.

Figure 15. The Power Up Transition of CS5141X Regulator

#### **Short Circuit**

When the V<sub>FB</sub> pin voltage drops below Foldback Threshold, the regulator reduces the peak current limit by 40% and switching frequency to 1/4 of the nominal frequency. These features are designed to protect the IC and external components during overload or short circuit conditions. In those conditions, peak switching current is clamped to the current limit threshold. The reduced switching frequency significantly increases the ripple current, and thus lowers the DC current. The short circuit can cause the minimum duty cycle to be limited by Minimum Output Pulse Width. The foldback frequency reduces the minimum duty cycle by extending the switching cycle. This protects the IC from overheating, and also limits the power that can be transferred to the output. The current limit foldback effectively reduces the current stress on the inductor and diode. When the output is shorted, the DC current of the inductor and diode can approach the current limit threshold. Therefore, reducing the current limit by 40% can result in an equal percentage drop of the inductor and

diode current. The short circuit waveforms are captured in Figure 16, and the benefit of the foldback frequency and current limit is self-evident.

Figure 16. In Short Circuit, the Foldback Current and Foldback Frequency Limit the Switching Current to Protect the IC, Inductor and Catch Diode

#### **Thermal Considerations**

A calculation of the power dissipation of the IC is always necessary prior to the adoption of the regulator. The current drawn by the IC includes quiescent current, predriver current, and power switch base current. The quiescent current drives the low power circuits in the IC, which include comparators, error amplifier and other logic blocks. Therefore, this current is independent of the switching current and generates power equal to

$$W_Q = V_{IN} \times I_Q$$

where:

$I_{O}$  = quiescent current.

The predriver current is used to turn on/off the power switch and is approximately equal to 12 mA in worst case. During steady state operation, the IC draws this current from the Boost pin when the power switch is on and then receives it from the  $V_{IN}$  pin when the switch is off. The predriver current always returns to the  $V_{SW}$  pin. Since the predriver current goes out to the regulator's output even when the power switch is turned off, a minimum load is required to prevent overvoltage in light load conditions. If the Boost pin voltage is equal to  $V_{IN} + V_O$  when the switch is on, the power dissipation due to predriver current can be calculated by

$$W_{DRV} = 12 \text{ mA} \times (V_{IN} - V_O + \frac{V_O^2}{V_{IN}})$$

The base current of a bipolar transistor is equal to collector current divided by beta of the device. Beta of 60 is used here to estimate the base current. The Boost pin provides the base current when the transistor needs to be on.

The power dissipated by the IC due to this current is

$$W_{BASE} = \frac{V_0^2}{V_{IN}} \times \frac{I_S}{60}$$

where:

$I_S = DC$  switching current.

When the power switch turns on, the saturation voltage and conduction current contribute to the power loss of a non-ideal switch. The power loss can be quantified as

$$W_{SAT} = \frac{V_{O}}{V_{IN}} \times I_{S} \times V_{SAT}$$

where:

V<sub>SAT</sub> = saturation voltage of the power switch which is shown in Figure 12.

The switching loss occurs when the switch experiences both high current and voltage during each switch transition. This regulator has a 30 ns turn-off time and associated power loss is equal to

$$W_S = \frac{I_S \times V_{IN}}{2} \times 30 \text{ ns} \times f_S$$

The turn-on time is much shorter and thus turn-on loss is not considered here.

The total power dissipated by the IC is sum of all the above

The IC junction temperature can be calculated from the ambient temperature, IC power dissipation and thermal resistance of the package. The equation is shown as follows,

$$T_J = W_{IC} \times R_{\theta JA} + T_A$$

The maximum IC junction temperature shall not exceed 125°C to guarantee proper operation and avoid any damages to the IC.

## Using the BIAS Pin

The efficiency savings in using the BIAS pin is most notable at low load and high input voltage as will be explained below.

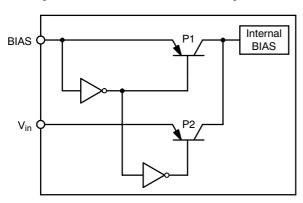

Figure 17 will help to understand the increase in efficiency when the BIAS pin is used. The circuitry shown is not the actual implementation, but is useful in the explanation.

Figure 17.

Internal bias to the IC can be supplied via the  $V_{in}$  pin or the BIAS pin. When the BIAS pin is low, the logic turns P2 on and current is routed to the internal bias circuitry from the  $V_{in}$  pin. Conversely, when the BIAS pin is high, the logic turns P1 on and current is routed to the internal bias circuitry from the BIAS pin.

Here is an example of the power savings:

The input voltage range for V<sub>in</sub> is 4.5 V to 40 V. The input voltage range for BIAS is 3.3 V to 6 V. The quiescent current specification is 3 mA (min), 4 mA (typ), and 6.25 mA (max).

Using a typical battery voltage of 14 V and the typical quiescent current number of 4 mA, the power would be:

$$P = V \times I = 14 \times 4e-3 = 56 \text{ mW}$$

We'll assume the BIAS pin is connected to an external regulator at 5 V instead of the output voltage. The BIAS pin would normally be connected to the output voltage, but adding an added switching regulator efficiency number here would cloud this example. Now the internal BIAS circuitry is being powered via 5 V. The resulting on chip power being dissipated is:

$$P = V \times I = 5 \times 4e-3 = 21 \text{ mW}$$

The power savings is 35 mW.

Now, to demonstrate more notable savings using the maximum battery input voltage of 40 V, the maximum quiescent current of 6.25 mA, and the lowest allowed BIAS voltage for proper operation of 3.3 V;

Powered from Vin:

$$P = 40 \times 6.25e-3 = 250 \text{ mW}$$

Powered from the BIAS pin:

$$P = 3.3 \times 6.25e-3 = 21 \text{ mW}$$

The power savings is 229 mW.

## **Minimum Load Requirement**

As pointed out in the previous section, a minimum load is required for this regulator due to the predriver current feeding the output. Placing a resistor equal to  $V_O$  divided by 12 mA should prevent any voltage overshoot at light load conditions. Alternatively, the feedback resistors can be valued properly to consume 12 mA current.

#### **COMPONENT SELECTION**

#### **Input Capacitor**

In a buck converter, the input capacitor witnesses pulsed current with an amplitude equal to the load current. This pulsed current and the ESR of the input capacitors determine the  $V_{IN}$  ripple voltage, which is shown in Figure 18. For  $V_{IN}$  ripple, low ESR is a critical requirement for the input capacitor selection. The pulsed input current possesses a significant AC component, which is absorbed by the input capacitors.

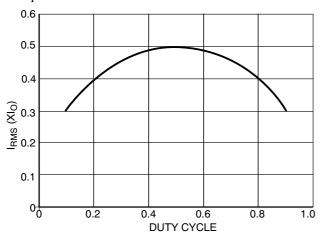

The RMS current of the input capacitor can be calculated using:

$$I_{BMS} = I_{O} \sqrt{D(1-D)}$$

where:

D = switching duty cycle which is equal to  $V_O/V_{IN}$ .  $I_O$  = load current.

Figure 18. Input Voltage Ripple in a Buck Converter

To calculate the RMS current, multiply the load current with the constant given by Figure 19 at each duty cycle. It is a common practice to select the input capacitor with an RMS current rating more than half the maximum load current. If multiple capacitors are paralleled, the RMS current for each capacitor should be the total current divided by the number of capacitors.

Figure 19. Input Capacitor RMS Current can be Calculated by Multiplying Y Value with Maximum Load Current at any Duty Cycle

Selecting the capacitor type is determined by each design's constraint and emphasis. The aluminum electrolytic capacitors are widely available at lowest cost. Their ESR and Equivalent Series Inductor (ESL) are relatively high. Multiple capacitors are usually paralleled to achieve lower ESR. In addition, electrolytic capacitors usually need to be paralleled with a ceramic capacitor for filtering high frequency noises. The OS-CON are solid aluminum electrolytic capacitors, and therefore has a much lower ESR. Recently, the price of the OS-CON capacitors has dropped significantly so that it is now feasible to use them for some low cost designs. Electrolytic capacitors are physically large, and not used in applications where the size, and especially height is the major concern.

Ceramic capacitors are now available in values over  $10\,\mu\text{F}$ . Since the ceramic capacitor has low ESR and ESL, a single ceramic capacitor can be adequate for both low frequency and high frequency noises. The disadvantage of ceramic capacitors are their high cost. Solid tantalum capacitors can have low ESR and small size. However, the reliability of the tantalum capacitor is always a concern in the application where the capacitor may experience surge current.

## **Output Capacitor**

In a buck converter, the requirements on the output capacitor are not as critical as those on the input capacitor. The current to the output capacitor comes from the inductor and thus is triangular. In most applications, this makes the RMS ripple current not an issue in selecting output capacitors.

The output ripple voltage is the sum of a triangular wave caused by ripple current flowing through ESR, and a square wave due to ESL. Capacitive reactance is assumed to be small compared to ESR and ESL. The peak-to-peak ripple current of the inductor is:

$$IP - P = \frac{VO(VIN - VO)}{(VIN)(L)(fS)}$$

$V_{RIPPLE(ESR)}$ , the output ripple due to the ESR, is equal to the product of  $I_{P-P}$  and ESR. The voltage developed across the ESL is proportional to the di/dt of the output capacitor. It is realized that the di/dt of the output capacitor is the same as the di/dt of the inductor current. Therefore, when the switch turns on, the di/dt is equal to  $(V_{IN} - V_O)/L$ , and it becomes  $V_O/L$  when the switch turns off. The total ripple voltage induced by ESL can then be derived from

$$V_{RIPPLE(ESL)} = ESL(\frac{VIN}{L}) + ESL(\frac{VIN - VO}{L}) = ESL(\frac{VIN}{L})$$

The total output ripple is the sum of the  $V_{RIPPLE(ESR)}$  and  $V_{RIPPLE(ESR)}. \label{eq:vripple}$

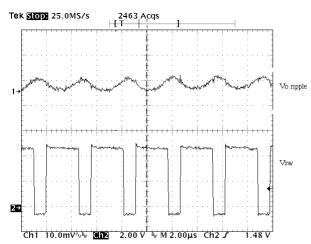

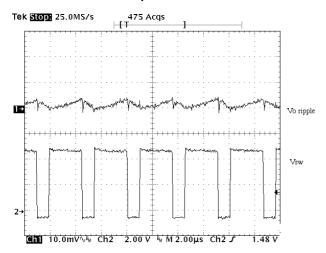

Figure 20. The Output Voltage Ripple Using Two 10  $\mu$ F Ceramic Capacitors in Parallel

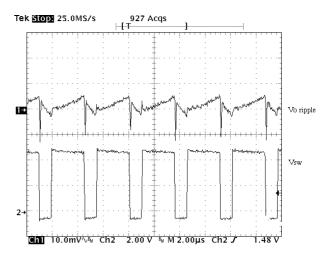

Figure 21. The Output Voltage Ripple Using One 100  $\mu F$  POSCAP Capacitor

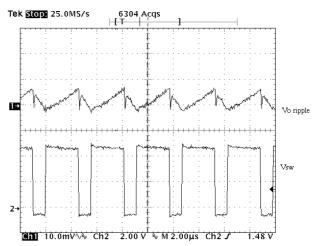

Figure 22. The Output Voltage Ripple Using One 100  $\mu F$  OS-CON

Figure 23. The Output Voltage Ripple Using One 100  $\mu F$  Tantalum Capacitor

Figure 20 to Figure 23 show the output ripple of a 5.0 V to 3.3 V/500 mA regulator using 22 µH inductor and various capacitor types. At the switching frequency, the low ESR and ESL make the ceramic capacitors behave capacitively as shown in Figure 20. Additional paralleled ceramic capacitors will further reduce the ripple voltage, but inevitably increase the cost. "POSCAP", manufactured by SANYO, is a solid electrolytic capacitor. The anode is sintered tantalum and the cathode is a highly conductive polymerized organic semiconductor. TPC series, featuring low ESR and low profile, is used in the measurement of Figure 21. It is shown that POSCAP presents a good balance of capacitance and ESR, compared with a ceramic capacitor. In this application, the low ESR generates less than 5.0 mV of ripple and the ESL is almost unnoticeable. The ESL of the through-hole OS-CON capacitor give rise to the inductive impedance. It is evident from Figure 22 which shows the step rise of the output ripple on the switch turn-on and large spike on the switch turn-off. The ESL prevents the output capacitor from quickly charging up the parasitic capacitor of the inductor when the switch node is pulled below ground through the catch diode conduction. This results in the spike associated with the falling edge of the switch node. The D package tantalum capacitor used in Figure 23 has the same footprint as the POSCAP, but doubles the height. The ESR of the tantalum capacitor is apparently higher than the POSCAP. The electrolytic and tantalum capacitors provide a low-cost solution with compromised performance. The reliability of the tantalum capacitor is not a serious concern for output filtering because the output capacitor is usually free of surge current and voltage.

## **Diode Selection**

The diode in the buck converter provides the inductor current path when the power switch turns off. The peak reverse voltage is equal to the maximum input voltage. The peak conducting current is clamped by the current limit of the IC. The average current can be calculated from:

$$I_{D(AVG)} = \frac{I_{O}(V_{IN} - V_{O})}{V_{IN}}$$

The worse case of the diode average current occurs during maximum load current and maximum input voltage. For the diode to survive the short circuit condition, the current rating of the diode should be equal to the Foldback Current Limit. See Table 1 for Schottky diodes from ON Semiconductor which are suggested for CS5141X regulator.

#### **Inductor Selection**

When choosing inductors, one might have to consider maximum load current, core and copper losses, component height, output ripple, EMI, saturation and cost. Lower inductor values are chosen to reduce the physical size of the inductor. Higher value cuts down the ripple current, core losses and allows more output current. For most applications, the inductor value falls in the range between  $2.2~\mu H$  and  $22~\mu H$ . The saturation current ratings of the inductor shall not exceed the  $I_{L(PK)}$ , calculated according to

$$I_{L(PK)} = I_{O} + \frac{V_{O}(V_{IN} - V_{O})}{2(f_{S})(L)(V_{IN})}$$

The DC current through the inductor is equal to the load current. The worse case occurs during maximum load current. Check the vendor's spec to adjust the inductor value undercurrent loading. Inductors can lose over 50% of inductance when it nears saturation.

The core materials have a significant effect on inductor performance. The ferrite core has benefits of small physical size, and very low power dissipation. But be careful not to operate these inductors too far beyond their maximum ratings for peak current, as this will saturate the core. Powered Iron cores are low cost and have a more gradual saturation curve. The cores with an open magnetic path, such as rod or barrel, tend to generate high magnetic field radiation. However, they are usually cheap and small. The cores providing a close magnetic loop, such as pot-core and toroid, generate low electro-magnetic interference (EMI).

There are many magnetic component vendors providing standard product lines suitable for CS5141X. Table 2 lists three vendors, their products and contact information.

Table 1.

| Part Number | V <sub>BREAKDOWN</sub> (V) | I <sub>AVERAGE</sub> (A) | V <sub>(F)</sub> (V) @ I <sub>AVERAGE</sub> | Package    |

|-------------|----------------------------|--------------------------|---------------------------------------------|------------|

| 1N5817      | 20                         | 1.0                      | 0.45                                        | Axial Lead |

| 1N5818      | 30                         | 1.0                      | 0.55                                        | Axial Lead |

| 1N5819      | 40                         | 1.0                      | 0.6                                         | Axial Lead |

| MBR0520     | 20                         | 0.5                      | 0.385                                       | SOD-123    |

| MBR0530     | 30                         | 0.5                      | 0.43                                        | SOD-123    |

| MBR0540     | 40                         | 0.5                      | 0.53                                        | SOD-123    |

| MBRS120     | 20                         | 1.0                      | 0.55                                        | SMB        |

| MBRS130     | 30                         | 1.0                      | 0.395                                       | SMB        |

| MBRS140     | 40                         | 1.0                      | 0.6                                         | SMB        |

## Table 2.

| Vendor      | Product Family                                                                                                                                                         | Web Site            | Telephone      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|

| Coiltronics | UNI-Pac1/2: SMT, barrel THIN-PAC: SMT, toroid, low profile CTX: Leaded, toroid                                                                                         | www.coiltronics.com | (516) 241-7876 |

| Coilcraft   | DO1608: SMT, barrel DS/DT 1608: SMT, barrel, magnetically shielded DO3316: SMT, barrel DS/DT 3316: SMT, barrel, magnetically shielded DO3308: SMT, barrel, low profile | www.coilcraft.com   | (800) 322-2645 |

| Pulse       | -                                                                                                                                                                      | www.pulseeng.com    | (619) 674-8100 |

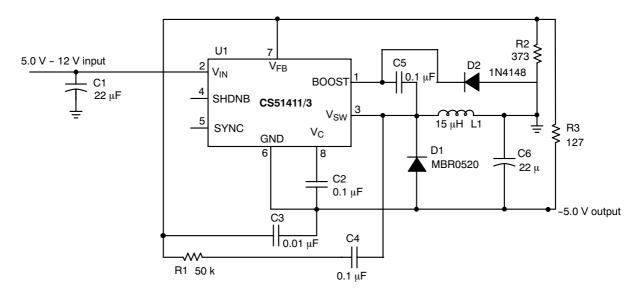

Figure 24. Additional Application Diagram, 5.0 V - 12 V to -5.0 V/400 mA Inverting Converter

Figure 25. Additional Application Diagram, 12 V to 5.0 V/1.0 A Buck Converter using the BIAS Pin

## **ORDERING INFORMATION**

| Device        | Operating Temperature Range   | Package          | Shipping <sup>†</sup> |

|---------------|-------------------------------|------------------|-----------------------|

| CS51411ED8    |                               | SOIC-8           | 98 Units/Rail         |

| CS51411ED8G   |                               | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51411EDR8   |                               | SOIC-8           | 2500 Tape & Reel      |

| CS51411EDR8G  |                               | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51411EMNR2G |                               | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51412ED8    |                               | SOIC-8           | 98 Units/Rail         |

| CS51412ED8G   |                               | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51412EDR8   |                               | SOIC-8           | 2500 Tape & Reel      |

| CS51412EDR8G  |                               | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51412EMNR2G | 1                             | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51413ED8    | -40°C < T <sub>A</sub> < 85°C | SOIC-8           | 98 Units/Rail         |

| CS51413ED8G   | 7                             | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51413EDR8   | 1                             | SOIC-8           | 2500 Tape & Reel      |

| CS51413EDR8G  |                               | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51413EMNR2G |                               | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51414ED8    |                               | SOIC-8           | 98 Units/Rail         |

| CS51414ED8G   |                               | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51414EDR8   |                               | SOIC-8           | 2500 Tape & Reel      |

| CS51414EDR8G  |                               | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51414EMNR2G | 7                             | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51411GD8    |                               | SOIC-8           | 98 Units/Rail         |

| CS51411GD8G   | 7                             | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51411GDR8   | 7                             | SOIC-8           | 2500 Tape & Reel      |

| CS51411GDR8G  | 1                             | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51411GMNR2G | 7                             | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51412GD8    | 1                             | SOIC-8           | 98 Units/Rail         |

| CS51412GD8G   | 1                             | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51412GDR8   | 1                             | SOIC-8           | 2500 Tape & Reel      |

| CS51412GDR8G  | 7                             | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51412GMNR2G | ]                             | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51413GD8    | - 0°C < T <sub>A</sub> < 70°C | SOIC-8           | 98 Units/Rail         |

| CS51413GD8G   |                               | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51413GDR8   |                               | SOIC-8           | 2500 Tape & Reel      |

| CS51413GDR8G  |                               | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

| CS51413GMNR2G | -                             | DFN18 (Pb-Free)  | 2500 Tape & Reel      |

| CS51414GD8    |                               | SOIC-8           | 98 Units/Rail         |

| CS51414GD8G   | 1                             | SOIC-8 (Pb-Free) | 98 Units/Rail         |

| CS51414GDR8   |                               | SOIC-8           | 2500 Tape & Reel      |

| CS51414GDR8G  |                               | SOIC-8 (Pb-Free) | 2500 Tape & Reel      |

|               |                               |                  |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

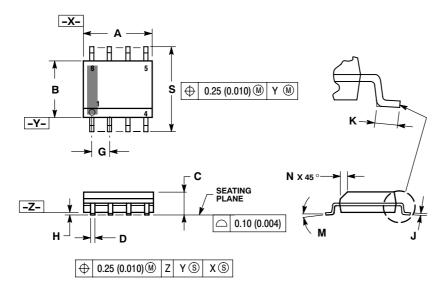

## PACKAGE DIMENSIONS

## SOIC-8 NB CASE 751-07 **ISSUE AH**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |       | INC   | HES   |

|-----|-------------|-------|-------|-------|

| DIM | MIN         | MAX   | MIN   | MAX   |

| Α   | 4.80        | 5.00  | 0.189 | 0.197 |

| В   | 3.80        | 4.00  | 0.150 | 0.157 |

| С   | 1.35        | 1.75  | 0.053 | 0.069 |

| D   | 0.33        | 0.51  | 0.013 | 0.020 |

| G   | 1.27        | 7 BSC | 0.05  | 0 BSC |

| Н   | 0.10        | 0.25  | 0.004 | 0.010 |

| J   | 0.19        | 0.25  | 0.007 | 0.010 |

| K   | 0.40        | 1.27  | 0.016 | 0.050 |

| M   | 0 °         | 8 °   | 0 °   | 8 °   |

| N   | 0.25        | 0.50  | 0.010 | 0.020 |

| S   | 5.80        | 6.20  | 0.228 | 0 244 |

## **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **PACKAGE THERMAL DATA**

| Parameter       |         | SOIC-8 | Unit |

|-----------------|---------|--------|------|

| $R_{\theta JC}$ | Typical | 45     | °C/W |

| $R_{\theta JA}$ | Typical | 165    | °C/W |

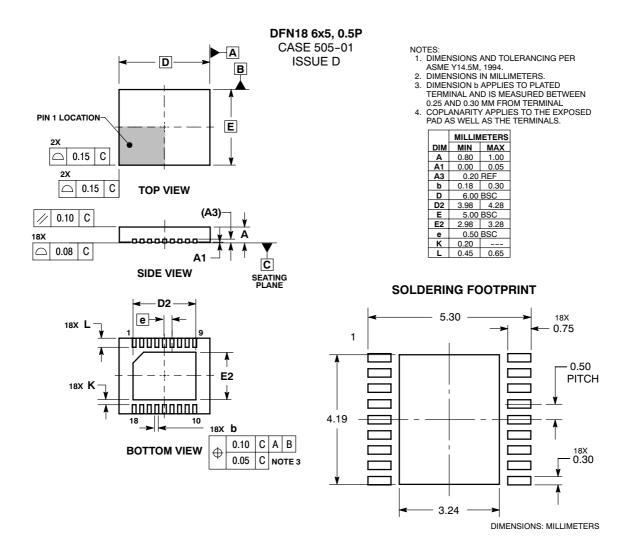

#### PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **PACKAGE THERMAL DATA**

| Parameter       |         | DFN18 | Unit |

|-----------------|---------|-------|------|

| $R_{\theta JA}$ | Typical | 35    | °C/W |

V<sup>2</sup> is a trademark of Switch Power, Inc.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative