# **Integrated Driver and MOSFET**

The NCP5360R integrates a MOSFET driver, high-side MOSFET and low-side MOSFET into a 8mm x 8mm 56-pin QFN package. The driver and MOSFETs have been optimized for high-current DC-DC buck power conversion applications. The NCP5360R integrated solution greatly reduces package parasitics and board space compared to a discrete component solution.

#### **Features**

- Capable of Switching Frequencies up to 1 MHz

- Capable of Output Currents up to 40 A

- Integrated Bootstrap Diode

- Output Disable Control turns off both MOSFETs

- Anti Cross-Conduction Protection Circuitry

- Undervoltage Lockout

- Internal Thermal Shutdown for System Protection

- These are Pb-free Devices

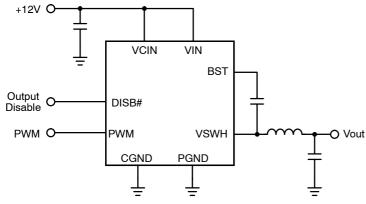

Figure 1. Application Schematic

# ON Semiconductor®

http://onsemi.com

# MARKING DIAGRAM

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP5360RMNR2G | QFN56<br>(Pb-Free) | 2500/Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

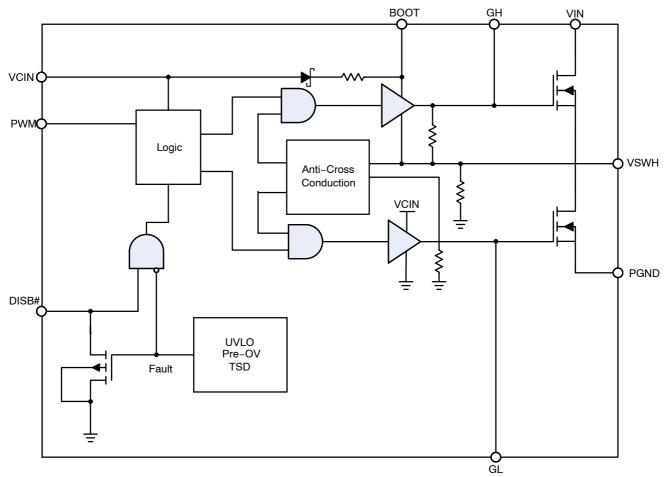

Figure 2. Simplified Block Diagram

# **PIN CONNECTIONS**

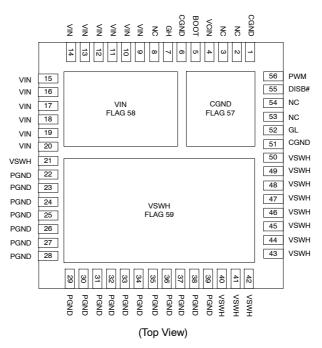

Figure 3. Pin Connections

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin No.            | Pin Name | Description                   |

|--------------------|----------|-------------------------------|

| 2, 3, 8, 53, 54    | NC       | No Connect                    |

| 4                  | VCIN     | Control Input Voltage         |

| 1, 6, 51, Flag 57  | CGND     | Control Signal Ground         |

| 21, 40-50, Flag 59 | VSWH     | Switch Node Output            |

| 52                 | GL       | Low Side FET Gate Access Pin  |

| 22-39              | PGND     | Power Ground                  |

| 9-20, Flag 58      | VIN      | Input Voltage                 |

| 7                  | GH       | High Side FET Gate Access Pin |

| 5                  | воот     | Bootstrap Voltage Pin         |

| 55                 | DISB#    | Output Disable Pin            |

| 56                 | PWM      | PWM Drive Logic               |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Pin Symbol | Pin Name              | Min                    | Max                                                     |

|------------|-----------------------|------------------------|---------------------------------------------------------|

| VCIN       | Control Input Voltage | -0.3 V                 | 15 V                                                    |

| VIN        | Power Input Voltage   | -0.3 V                 | 30 V                                                    |

| BOOT       | Bootstrap Voltage     | -0.3 V wrt/VSWH        | 35 V wrt/PGND<br>40 V < 50 ns wrt/PGND<br>15 V wrt/VSWH |

| VSWH       | Switch Node Output    | −5 V<br>−10 V < 200 ns | 30 V                                                    |

| PWM        | PWM Drive Logic       | -0.3 V                 | 6.5 V                                                   |

| DISB#      | Output Disable        | -0.3 V                 | 6.5 V                                                   |

| PGND       | Ground                | 0 V                    | 0 V                                                     |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **Table 3. THERMAL CHARACTERISTICS**

| Rating                            | Symbol            | Value      | Unit |

|-----------------------------------|-------------------|------------|------|

| Thermal Resistance, High-Side FET | $R_{\theta JPCB}$ | 13         | °C/W |

| Thermal Resistance, Low-Side FET  | $R_{\theta JPCB}$ | 5.0        | °C/W |

| Operating Junction Temperature    | TJ                | 0 to 150   | °C   |

| Storage Temperature               | T <sub>S</sub>    | -55 to 150 | °C   |

<sup>1.</sup> Refer to ELECTRICAL CHARACTERISTIS and APPLICATION INFORMATION for Safe Operating Area.

# Table 4. OPERATING RANGES (Note 2)

| Rating                | Symbol           | Min | Тур | Max  | Unit |

|-----------------------|------------------|-----|-----|------|------|

| Control Input Voltage | V <sub>CIN</sub> | 4.5 | 12  | 13.2 | V    |

| Input Voltage         | V <sub>IN</sub>  | 4.5 | 12  | 25   | V    |

<sup>2.</sup> Refer to ELECTRICAL CHARACTERISTIS and APPLICATION INFORMATION for Safe Operating Area.

**ELECTRICAL CHARACTERISTICS** (Notes 3, 4) (VCIN = 12 V, VIN = 12 V,  $T_A = -10^{\circ}C$  to  $+100^{\circ}C$ , unless otherwise noted)

| Parameter                         | Symbol               | Condition                                | Min | Тур  | Max | Unit |

|-----------------------------------|----------------------|------------------------------------------|-----|------|-----|------|

| SUPPLY CURRENT                    | •                    |                                          | •   | •    | •   | •    |

| VCIN Current (Normal Mode)        | _                    | DISB# = 5 V, PWM = OSC, Fsw = 400 kHz    |     |      | 75  | mA   |

| VCIN Current (Shutdown Mode)      | -                    | DISB# = GND                              |     | 0.5  | 1.7 | mA   |

| UNDERVOLTAGE LOCKOUT              | •                    |                                          | •   | •    |     |      |

| UVLO Startup                      | -                    |                                          | 3.8 | 4.35 | 4.5 | V    |

| UVLO Hysteresis                   | -                    |                                          | 150 | 200  | 250 | mV   |

| BOOTSTRAP DIODE                   | •                    |                                          |     |      |     |      |

| Bootstrap Diode Forward Voltage   | _                    | VCIN = 12 V, Forward Bias Current = 2 mA | 0.1 | 0.4  | 0.6 | V    |

| PWM INPUT                         |                      |                                          |     |      |     | •    |

| PWM Input Voltage High            | V <sub>PWM_HI</sub>  |                                          | 3.3 |      |     | V    |

| PWM Input Voltage Mid-State       | V <sub>PWM_MID</sub> |                                          | 1.3 |      | 2.7 | V    |

| PWM Input Voltage Low             | V <sub>PWM_LO</sub>  |                                          |     |      | 0.7 | V    |

| Tri-State Shutdown Holdoff Time   | -                    |                                          |     | 200  |     | ns   |

| OUTPUT DISABLE                    |                      |                                          |     |      |     | •    |

| Output Disable Input Voltage High | V <sub>DISB_HI</sub> |                                          | 2.0 |      |     | V    |

| Output Disable Input Voltage Low  | V <sub>DISB_LO</sub> |                                          |     |      | 1.0 | V    |

| Output Disable Hysteresis         | _                    |                                          |     | 500  |     | mV   |

| Output Disable Propagation Delay  |                      |                                          |     | 20   | 40  | ns   |

Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T<sub>J</sub> = T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

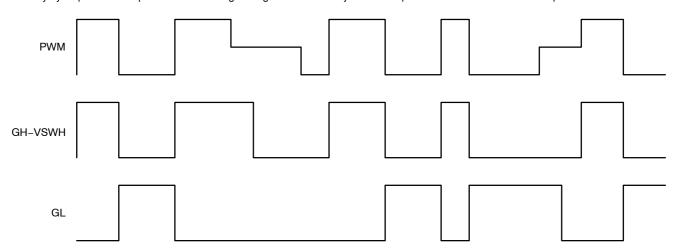

Figure 4. Timing Diagram

#### APPLICATION INFORMATION

## **Theory of Operation**

The NCP5360R is an integrated driver and MOSFET module designed for use in a synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and low-side MOSFETs.

# **Undervoltage Lockout**

GH and GL are held low until VCIN reaches 4.5 V during startup. The PWM signals will control the gate status when the VCIN threshold is exceeded.

#### **Power-On Reset**

Power-On Reset feature is used to protect against an abnormal status during startup. When the initial soft-start voltage is greater than 2.75 V, the switch node pin is monitored. If VSWH is higher than 2.25 V, the low-side FET is turned on to discharge the output capacitors. The fault mode will latch and DISB# will be forced low until the part is recycled. When the input voltage is higher than 4.5 V and DISB# is high, the part will enter normal operation.

#### **Bi-Directional DISB# Signal**

Fault modes such as Power-On Reset, Overtemperature and Undervoltage Lockout will assert the DISB# pin. This will pull down the DRON of the controller as well, thus shutting the controller down.

#### Low-Side Driver

The low-side driver is designed to drive a ground referenced low RDS(on) N-Channel MOSFET. The voltage rail for the low-side driver is internally connected to VCIN and CGND.

## **High-Side Driver**

The high-side driver is designed to drive a floating low RDS(on) N-channel MOSFET. The gate voltage for the high-side driver is developed by a bootstrap circuit referenced to Switch Node (VSWH) pin.

The bootstrap circuit is comprised of the internal bootstrap diode, and an external bootstrap capacitor. When the NCP5360R is starting up, the VSWH pin is at ground, so the bootstrap capacitor will charge up to VCIN through the bootstrap diode. When the PWM input goes high, the high–side driver will begin to turn on the high–side MOSFET using the stored charge of the bootstrap capacitor. As the high–side MOSFET turns on, the VSWH pin will rise. When the high–side MOSFET is fully on, the switch node will be at 12 V, and the BST pin will be at 12 V plus the charge of the bootstrap capacitor (approaching 24 V).

The bootstrap capacitor is recharged when the switch node goes low during the next cycle.

# **Safety Timer and Overlap Protection Circuit**

It is very important that MOSFETs in a synchronous buck regulator do not both conduct at the same time. Excessive shoot-through or cross-conduction can damage the MOSFETs, and even a small amount of cross-conduction will cause a decrease in the power conversion efficiency.

The NCP5360R prevents cross conduction by monitoring the status of the MOSFETs and applying the appropriate amount of "dead–time" or the time between the turn off of one MOSFET and the turn on of the other MOSFET.

When the PWM input pin goes high, the gate of the low-side MOSFET (GL pin) will go low after a propagation delay (tpdlDRVL). The time it takes for the low-side MOSFET to turn off (tfDRVL) is dependent on the total charge on the low-side MOSFET gate. The NCP5360R monitors the gate voltage of both MOSFETs and the switchnode voltage to determine the conduction status of the MOSFETs. Once the low-side MOSFET is turned off an internal timer will delay (tpdhDRVH) the turn on of the high-side MOSFET.

Likewise, when the PWM input pin goes low, the gate of the high-side MOSFET (GH pin) will go low after the propagation delay (tpdlDRVH). The time to turn off the high-side MOSFET (tfDRVH) is dependent on the total gate charge of the high-side MOSFET. A timer will be triggered once the high-side MOSFET has stopped conducting, to delay (tpdhDRVL) the turn on of the low-side MOSFET.

When the PWM input is between  $V_{PWM\_LO}$  and  $V_{PWM\_HI}$  for longer than 200 ns, both the high-side and low-side MOSFETs will be turned off. The PWM input will need to exceed  $V_{PWM\_HI}$  to resume normal switching of the MOSFETs.

## **Power Supply Decoupling**

The NCP5360R can source and sink relatively large currents to the gate pins of the MOSFETs. In order to maintain a constant and stable supply voltage (VCIN) a low ESR capacitor should be placed near the power and ground pins. A 1  $\mu$ F to 4.7  $\mu$ F multi layer ceramic capacitor (MLCC) is usually sufficient.

#### **Input Pins**

The PWM input and the Output Disable pins of the NCP5360R have internal protection for Electro Static Discharge (ESD), but in normal operation they present a relatively high input impedance. If the PWM controller does not have internal pull-down resistors, they should be added externally to ensure that the driver outputs do not go high before the controller has reached its undervoltage lockout threshold.

#### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor (CBST) and the internal diode. The bootstrap capacitor must have a voltage rating that is able to withstand twice the maximum supply voltage. A minimum 50 V rating is recommended. A bootstrap capacitance greater than 100 nF is recommended. A good quality ceramic capacitor should be used.

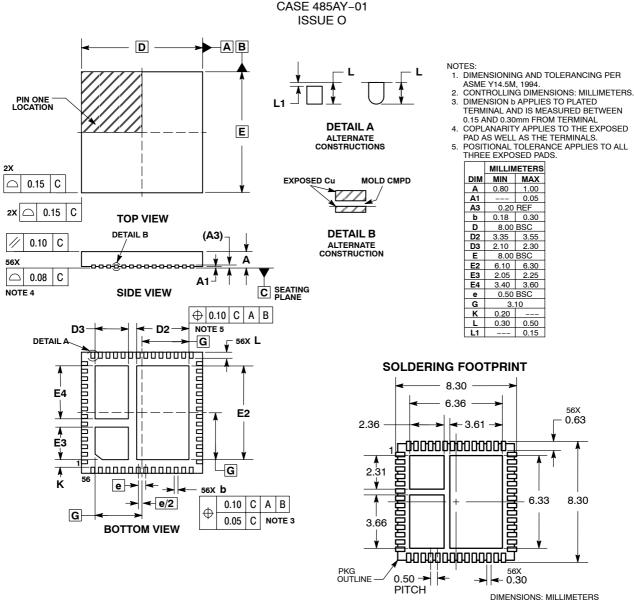

#### PACKAGE DIMENSIONS

## QFN56 8x8, 0.5P MN SUFFIX CASE 485AY-01 ISSUF O

ON Semiconductor and a registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.