# PFC and Half-Bridge Resonant Combo Controller for LED Lighting

The NCL30051 is a combination of PFC and half-bridge resonant controllers optimized for off-line LED lighting solutions. This device integrates all the features needed to implement a highly efficient and small form factor LED Driver/Power Supply. It contains a critical conduction mode (CrM) power factor correction (PFC) boost controller and a half-bridge resonant controller with a built-in 600 V driver. The half-bridge stage operates at a fixed frequency, greatly simplifying the control implementations. The output (current or voltage) regulation is achieved by adjusting the PFC stage output voltage – based on a control signal generated external to the NCL30051.

This device includes an enable input on the PFC feedback pin, open feedback loop protection and PFC overvoltage and undervoltage detectors. Other features included in the NCL30051 are a 600 V startup circuit and an adjustable frequency oscillator with a divide by 2 circuit to assure true symmetric duty ratio. The controllers are properly sequenced, simplifying system design.

## Features

- Voltage Mode CrM Power Factor Correction Controller

- PFC Open Feedback Loop Protection

- PFC Undervoltage Detector

- PFC Overvoltage Detector

- Half-Bridge Stage with 600 V High Side Gate Drive

- State Machine Ensures Proper Turn-on and Turn-off of Half-Bridge Stage

- Controllers are Properly Sequenced for Fault Free Operation

- Non–Latching Fault Management

- Internal 600 V Startup Circuit

- Wide Temperature Range of -40°C to +125°C

- This is a Pb–Free Device

# **Typical Applications**

- High Efficiency LED Drivers and Power Supplies

- Electronic Control Gear

- Lighting Ballasts

ORDERING INFORMATION

SOIC-16

PGND

🞞 РСТ

PCS 🚥

PZCD 🚥

PControl

| Device       | Package              | Shipping <sup>†</sup> |

|--------------|----------------------|-----------------------|

| NCL30051DR2G | SOIC-16<br>(Pb-Free) | 2500/Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

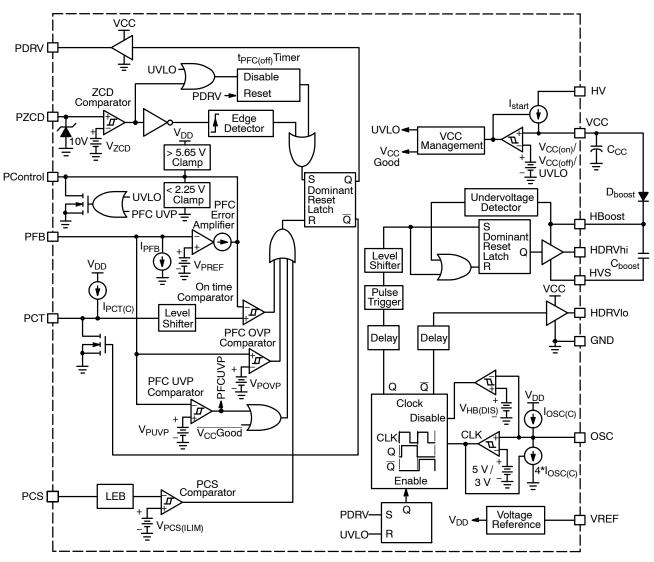

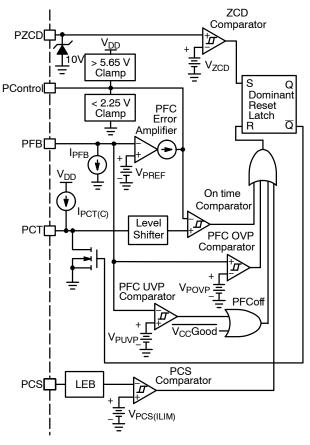

Figure 1. Functional Block Diagram

# Table 1. PIN FUNCTION DESCRIPTION

| Pin | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | HV       | This is the input of the high voltage startup regulator and connects directly to the bulk voltage. A constant current source supplies current from this pin to the $V_{CC}$ capacitor, eliminating the need for an external startup resistor. The charge current is 7.5 mA (typical).                                                                                                                                                                                                                                                                                                                                                           |

| 2   | OSC      | A capacitor on this pin adjusts the frequency of the internal oscillator. The oscillator sets the frequency of the half-bridge controller. Each half-bridge switch operates at half the oscillator frequency. The OSC pin also serves as a disable input for the half-bridge stage. The half-bridge stage is disabled by pulling down this pin below its disable threshold, V <sub>HB(DIS)</sub> , typically 1.955 V.                                                                                                                                                                                                                           |

| 3   | GND      | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | VREF     | Reference voltage. The capacitor on this pin decouples the internal reference. A 0.1 $\mu$ F capacitor needs to be connected between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5   | PFB      | PFC voltage feedback input. Connect to PFC output using a resistive divider network. The voltage on this pin is compared to a 2.5 V reference (typical) to regulate the PFC output voltage. The voltage on this pin is also used to detect PFC undervoltage and overvoltage conditions. In the typical intended application, the PFB pin voltage will set an upper bound on the PFC output voltage, while the actual PFC voltage control will be exercised by a control signal generated on the secondary side to provide accurate LED current/voltage control.                                                                                 |

| 6   | PCS      | PFC regulator current sense input. A voltage ramp proportional to the PFC switch current is applied to this pin. The current sense threshold, V <sub>PCS((LIM)</sub> , is typically 0.84 V. A 110 ns (typical) leading edge blanking circuit filters the current sense signal at the start of each cycle.                                                                                                                                                                                                                                                                                                                                       |

| 7   | PZCD     | PFC inductor zero current detector. The inductor current is monitored using an auxiliary winding on the PFC inductor. The PFC drive signal is enabled during a high to low transition on the PZCD pin. A series resistor limits the current into the PZCD pin. The watchdog timer is disabled while the PZCD voltage is above the ZCD arming threshold, V <sub>ZCD(high)</sub> . It is re–enabled once the voltage drops below the ZCD trigger threshold, V <sub>ZCD(low)</sub> . This feature can be used to disable PFC drive pulses.                                                                                                         |

| 8   | PControl | PFC control voltage. This pin connects to the output of the PFC error amplifier. The error amplifier is a transcon-<br>ductance amplifier. A compensation network between this pin and grounds sets the PFC loop bandwidth. The<br>PFC control voltage is compared to a level shifted version of V <sub>PCT</sub> to control the PFC duty ratio. In the typical<br>intended application, the PControl voltage will be controlled by a secondary side control signal through an opto-<br>coupler. The optocoupler signal is diode ORed to the internally generated PControl signal and the lower of the<br>two signals dictates the PFC on-time. |

| 9   | PCT      | PFC on time control capacitor. A 270 $\mu$ A (typical) current source charges a capacitor connected between this pin and ground. Once the level shifted PCT voltage reaches V <sub>PControl</sub> , the PFC drive signal is disabled and the PCT capacitor is discharged.                                                                                                                                                                                                                                                                                                                                                                       |

| 10  | VCC      | Positive input supply. This pin connects to an external capacitor for energy storage. An internal current source supplies current from HV to this pin. Once the $V_{CC}$ voltage reaches $V_{CC(on)}$ (15.3 V typical), the current source turns off and the controller is enabled. The current source turns on once $V_{CC}$ falls to $V_{CC(off)}$ (9.3 V typical). During normal operation, power is supplied to the IC via this pin by means of an auxiliary winding.                                                                                                                                                                       |

| 11  | PGND     | Ground connection for PDRV and HDRVIo. Tie to the power stage return with a short trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12  | PDRV     | PFC switch gate drive control signal. The source and sink drive capability is limited to 60 $\Omega$ and 15 $\Omega$ (typical), respectively. A discrete driver may be needed to drive the external MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13  | HDRVIo   | Half-bridge low side switch gate drive control signal. The source and sink drive capability is limited to 75 $\Omega$ and 15 $\Omega$ (typical), respectively. A discrete driver may be needed to drive the half bridge switch.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14  | HVS      | Half-bridge high side driver source connection. This pin connects directly to the bridge terminal and can float up to 600 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15  | HDRVhi   | Half-bridge high side switch gate drive control signal. The source and sink drive capability is limited to 75 $\Omega$ and 15 $\Omega$ (typical), respectively. The supply terminals of the high side driver connect to the HBoost and HVS pins. A discrete driver may be needed to drive the half bridge switch.                                                                                                                                                                                                                                                                                                                               |

| 16  | HBoost   | Supply voltage of the high side gate driver. A charge pump generates a bootstrap voltage floating on top of the HVS voltage. A diode between the VCC and HBoost pins provides a charge path. The bootstrap voltage is V <sub>CC</sub> minus a diode drop.                                                                                                                                                                                                                                                                                                                                                                                       |

# Table 2. MAXIMUM RATINGS (Notes 1 and 2)

| Rating                                                                                                                                               | Symbol                      | Value                                     | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|------|

| High Voltage Input Voltage                                                                                                                           | V <sub>HV</sub>             | -0.3 to 600                               | V    |

| High Voltage Input Current                                                                                                                           | I <sub>HV</sub>             | 10                                        | mA   |

| Supply Input Voltage                                                                                                                                 | V <sub>CC</sub>             | -0.3 to 20                                | V    |

| Supply Input Current                                                                                                                                 | I <sub>CC</sub>             | 10                                        | mA   |

| Oscillator Input Voltage                                                                                                                             | Vosc                        | –0.3 to V <sub>REF</sub>                  | V    |

| Oscillator Input Current                                                                                                                             | losc                        | 10                                        | mA   |

| Bandgap Reference Decoupling Output Voltage                                                                                                          | V <sub>REF</sub>            | –0.3 to 9                                 | V    |

| Bandgap Reference Decoupling Output Current                                                                                                          | I <sub>REF</sub>            | 10                                        | mA   |

| PFC Feedback Voltage Input Voltage                                                                                                                   | V <sub>PFB</sub>            | –0.3 to 10                                | V    |

| PFC Feedback Voltage Input Current                                                                                                                   | I <sub>PFB</sub>            | 10                                        | mA   |

| PFC Current Sense Input Voltage                                                                                                                      | V <sub>PCS</sub>            | -0.3 to 10                                | V    |

| PFC Current Sense Input Current                                                                                                                      | I <sub>PCS</sub>            | 10                                        | mA   |

| PFC Zero Current Detection Input Voltage                                                                                                             | V <sub>PZCD</sub>           | –0.3 to 10                                | V    |

| PFC Zero Current Detection Input Current                                                                                                             | I <sub>PZCD</sub>           | 10                                        | mA   |

| PFC Control Input Voltage                                                                                                                            | V <sub>PControl</sub>       | –0.3 to V <sub>REF</sub>                  | V    |

| PFC Control Input Current                                                                                                                            | I <sub>PControl</sub>       | 1.2                                       | mA   |

| PFC On Time Control Input Voltage                                                                                                                    | V <sub>PCT</sub>            | –0.3 to V <sub>REF</sub>                  | V    |

| PFC On Time Control Input Current                                                                                                                    | I <sub>PCT</sub>            | 9                                         | mA   |

| PFC Drive Signal Voltage                                                                                                                             | V <sub>PDRV</sub>           | –0.3 to $V_{CC}$                          | V    |

| PFC Drive Signal Current                                                                                                                             | I <sub>PDRV</sub>           | 100                                       | mA   |

| Half-Bridge Low Side Driver Input Voltage                                                                                                            | V <sub>HDRVIo</sub>         | –0.3 to $V_{CC}$                          | V    |

| Half-Bridge Low Side Driver Input Current                                                                                                            | I <sub>HDRVI0</sub>         | 100                                       | mA   |

| Half-Bridge High Side Driver Source Connection Input Voltage                                                                                         | V <sub>HVS</sub>            | -1.0 to 600                               | V    |

| Half-Bridge High Side Driver Source Connection Input Current                                                                                         | I <sub>HVS</sub>            | 100                                       | mA   |

| Half-Bridge High Side Driver Input Voltage                                                                                                           | V <sub>HDRVhi</sub>         | -1.3 to V <sub>HVS</sub> +V <sub>CC</sub> | V    |

| Half-Bridge High Side Driver Input Current                                                                                                           | I <sub>HDRVhi</sub>         | 100                                       | mA   |

| Half-Bridge High Side Driver Charge Pump Input Voltage                                                                                               | V <sub>HBoost</sub>         | –0.3 to V <sub>HVS</sub> +V <sub>CC</sub> | V    |

| Half-Bridge High Side Driver Charge Pump Input Current                                                                                               | I <sub>HBoost</sub>         | 100                                       | mA   |

| High Side Boost Circuit Supply Voltage (between HBoost and HVS pins)                                                                                 | V <sub>HBoost(supply)</sub> | –0.3 to $V_{CC}$                          | V    |

| High Side Boost Circuit Supply Voltage (between HBoost and HVS pins)                                                                                 | I <sub>HBoost(supply)</sub> | 100                                       | mA   |

| Half-Bridge High Side Driver Source Connection Slew Rate                                                                                             | dV <sub>HVS</sub> /dt       | 50                                        | V/ns |

| Junction Temperature (Biased)                                                                                                                        | TJ                          | 150                                       | °C   |

| Storage Temperature Range                                                                                                                            | T <sub>stg</sub>            | -60 to 150                                | °C   |

| Power Dissipation ( $T_A = 25^{\circ}C$ , 1 Oz Cu, 0.155 Sq Inch, Printed Circuit Copper Clad)<br>D Suffix, Plastic Package Case 751B–05 (SOIC–16)   | PD                          | 0.95                                      | W    |

| Thermal Resistance, Junction to Ambient<br>(1 Oz Cu, 0.155 Sq Inch, Printed Circuit Copper Clad)<br>D Suffix, Plastic Package Case 751B-05 (SOIC-16) | R <sub>θJA</sub>            | 130                                       | °C/M |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device(s) contains ESD protection and exceeds the following tests:

Pins 1, 14, 15 and 16 rated to the maximum voltage of the respective pins based on the maximum ratings table. All Other Pins: Human Body Model 1500 V per JEDEC Standard JESD22–A114E.

Machine Model 150 V per JEDEC Standard JESD22-A115-A. 2. This device contains Latch-Up protection and exceeds ± 100 mA per JEDEC Standard JESD78.

| Table 3. ELECTRICAL CHARACTERISTICS (V <sub>HV</sub> = open, V <sub>PFB</sub> = 2.4 V, V <sub>PCS</sub> = 0 V, V <sub>PZCD</sub> = 5 V, V <sub>PControl</sub> = open, V <sub>CC</sub> = 15 V,                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PDRV</sub> = open, V <sub>HDRVI0</sub> = open, V <sub>HVS</sub> = 0 V, V <sub>HDRVhi</sub> = open, V <sub>HBoost</sub> = 15 V, C <sub>OSC</sub> = 2200 pF, C <sub>VREF</sub> = 0.1 μF, C <sub>PCT</sub> = 1000 pF, for typical |

| values $T_J = 25^{\circ}C$ , for min/max values, $T_J$ is $-40^{\circ}C$ to $125^{\circ}C$ , unless otherwise noted)                                                                                                                  |

| Characteristics                                                                              | Conditions                                                                                                       | Symbol                                                                 | Min                 | Тур                 | Max                  | Unit |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|---------------------|----------------------|------|

| STARTUP AND SUPPLY CIRCUITS                                                                  |                                                                                                                  | •                                                                      |                     |                     | •                    |      |

| Supply Voltage<br>Startup Threshold<br>Minimum Enable Threshold<br>Minimum Operating Voltage | $V_{CC}$ Increasing $V_{CC}$ Decreasing $V_{CC}$ Decreasing $V_{CC}$ Decreasing                                  | V <sub>CC(on)</sub><br>V <sub>CC(enable)</sub><br>V <sub>CC(off)</sub> | 14.3<br>13.6<br>8.5 | 15.3<br>14.6<br>9.3 | 16.3<br>15.6<br>10.0 | V    |

| Supply Current<br>Device Disabled/Fault<br>Device Switching                                  | V <sub>PFB</sub> = V <sub>PUVP(low)</sub><br>(Note 3)                                                            | I <sub>CC1</sub><br>I <sub>CC2</sub>                                   | 1.0<br>1.8          | 1.4<br>2.4          | 1.8<br>3.0           | mA   |

| Startup Current                                                                              | $\label{eq:VCC} \begin{array}{l} V_{CC} = V_{CC \ (on)} - 0.2 \ \text{V}, \\ V_{HV} = 50 \ \text{V} \end{array}$ | I <sub>start</sub>                                                     | 3.0                 | 7.5                 | 10.5                 | mA   |

| Startup Circuit Off-State Leakage Current                                                    | $\begin{array}{l} V_{HV}=600 \text{ V},\\ V_{CC}=V_{CC \text{ (on)}}+0.2 \text{ V} \end{array}$                  | I <sub>HV(off)</sub>                                                   | -                   | 15                  | 50                   | μA   |

| BANDGAP REFERENCE                                                                            |                                                                                                                  |                                                                        |                     |                     |                      |      |

| Reference Voltage                                                                            | C <sub>REF</sub> = 0.1 μF                                                                                        | V <sub>REF</sub>                                                       | 6.605               | 7.000               | 7.295                | V    |

| OSCILLATOR                                                                                   |                                                                                                                  |                                                                        |                     |                     |                      |      |

| Half-Bridge Clock Frequency                                                                  | V <sub>HVS</sub> = 50 V                                                                                          | f <sub>clock</sub>                                                     | 13.5                | 15.5                | 16.5                 | kHz  |

| Maximum Half-Bridge Clock Frequency                                                          | C <sub>OSC</sub> = open                                                                                          | f <sub>clock(MAX)</sub>                                                | 75                  | _                   | -                    | kHz  |

| PFC ERROR AMPLIFIER                                                                          |                                                                                                                  |                                                                        |                     |                     |                      |      |

| PFC Feedback Voltage Reference                                                               | 0°C < T <sub>J</sub> < 125°C<br>−40°C < T <sub>J</sub> < 125°C                                                   | V <sub>PREF</sub>                                                      | 2.42<br>2.40        | 2.50<br>-           | 2.58<br>2.60         | V    |

| PFC Feedback Voltage Reference<br>Regulation with Line                                       | $V_{CC(on)}$ + 0.2 V < $V_{CC}$ < 20 V                                                                           | V <sub>PREF(line)</sub>                                                | -15                 | -                   | 15                   | mV   |

| Error Amplifier Drive Capability<br>Sink<br>Source                                           | V <sub>PControl</sub> = 4 V, V <sub>PFB</sub> = 5 V<br>V <sub>PControl</sub> = 4 V, V <sub>PFB</sub> = 0.5 V     | I <sub>EA(SNK)</sub><br>I <sub>EA(SRC)</sub>                           | 60<br>-60           | 80<br>80            |                      | μA   |

| Open Loop Error Amplifier<br>Transconductance                                                | $V_{PControl} = 4 V,$<br>$V_{PFB} = 2.4 V and 2.6 V$                                                             | Gm                                                                     | 60                  | 95                  | -                    | μS   |

| Feedback Input Pulldown Current Source                                                       | V <sub>PFB</sub> = 3 V                                                                                           | I <sub>PFB</sub>                                                       | 0.5                 | 1.2                 | 1.5                  | μΑ   |

| Error Amplifier Maximum Output Voltage                                                       | I <sub>PControl</sub> = 10 μA                                                                                    | V <sub>EA(OH)</sub>                                                    | 5.30                | 5.65                | 6.00                 | V    |

| Error Amplifier Minimum Output Voltage                                                       | I <sub>PControl</sub> = −10 μA                                                                                   | V <sub>EA(OL)</sub>                                                    | 2.10                | 2.25                | 2.40                 | V    |

| Error Amplifier Output Voltage Range                                                         | V <sub>EA(OH)</sub> – V <sub>EA(OL)</sub>                                                                        | $\Delta V_{EA}$                                                        | 3.1                 | 3.4                 | 3.7                  | V    |

3. Resistor/capacitor parallel combination (39 pF || 20 kΩ) between drive pin and driver supply and between xDRVxx and GND pins.

**Table 4. ELECTRICAL CHARACTERISTICS** ( $V_{HV}$  = open,  $V_{PEB}$  = 2.4 V,  $V_{PCS}$  = 0 V,  $V_{PZCD}$  = 5 V,  $V_{PControl}$  = open,  $V_{CC}$  = 15 V,  $V_{PDRV}$  = open,  $V_{HDRVlo}$  = open,  $V_{HVS}$  = 0 V,  $V_{HDRVhi}$  = open,  $V_{HBoost}$  = 15 V,  $C_{OSC}$  = 2200 pF,  $C_{VREF}$  = 0.1  $\mu$ F,  $C_{PCT}$  = 1000 pF, for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                                                                      | Conditions                                                              | Symbol                                               | Min                        | Тур                        | Max                        | Unit |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|------|

| PFC CURRENT SENSE                                                                                    |                                                                         |                                                      | •                          |                            | •                          |      |

| Current Sense Threshold Voltage                                                                      |                                                                         | V <sub>PCS(ILIM)</sub>                               | 0.78                       | 0.84                       | 0.92                       | V    |

| Current Sense Input Bias Current                                                                     | V <sub>PCS</sub> = 2 V                                                  | I <sub>PCS</sub>                                     | -1                         | 0                          | 1                          | μA   |

| Leading Edge Blanking Duration                                                                       |                                                                         | t <sub>PCS(LEB)</sub>                                | 40                         | 110                        | 200                        | ns   |

| Propagation Delay                                                                                    | V <sub>PCS</sub> = V <sub>PCS(ILIM)</sub> + 1 V                         | t <sub>PCS(delay)</sub>                              | -                          | 90                         | 250                        | ns   |

| PFC ZERO CURRENT DETECTION                                                                           |                                                                         |                                                      |                            |                            | •                          | •    |

| ZCD Threshold Voltage<br>Arming Threshold<br>Trigger Threshold                                       | $V_{PZCD}$ increasing $V_{PZCD}$ decreasing                             | V <sub>ZCD</sub> (high)<br>V <sub>ZCD</sub> (low)    | 1.9<br>1.3                 | 2.1<br>1.5                 | 2.3<br>1.7                 | V    |

| ZCD Voltage Hysteresis                                                                               |                                                                         | V <sub>ZCD(HYS)</sub>                                | 400                        | 600                        | 800                        | mV   |

| ZCD Input Bias Current                                                                               | V <sub>PZCD</sub> = 1 V<br>V <sub>PZCD</sub> = 5 V                      | I <sub>PZCD(bias1)</sub><br>I <sub>PZCD(bias2)</sub> | -1<br>-1                   | _                          | 1<br>1                     | μΑ   |

| PFC MAXIMUM OFF TIME                                                                                 |                                                                         |                                                      |                            |                            |                            |      |

| Maximum Off Time                                                                                     |                                                                         | t <sub>PFC(off)</sub>                                | 50                         | 180                        | 350                        | μs   |

| PFC ON TIME RAMP GENERATOR                                                                           |                                                                         |                                                      |                            |                            |                            |      |

| ON time Capacitor Charge Current                                                                     | V <sub>PCT</sub> = 0 V                                                  | I <sub>PCT(C)</sub>                                  | 220                        | 270                        | 300                        | μA   |

| On Time Capacitor Discharge Time                                                                     | V <sub>PCT</sub> = 2.4 V to 0.6 V                                       | t <sub>PCT(D)</sub>                                  | -                          | 70                         | 300                        | ns   |

| ON Time Capacitor Peak Voltage                                                                       |                                                                         | V <sub>PCT(peak)</sub>                               | 2.6                        | 3.0                        | 3.4                        | V    |

| Minimum Duty Ratio                                                                                   | V <sub>PFB</sub> = 3.0 V, V <sub>PZCD</sub> = 0 V                       | D <sub>PMIN</sub>                                    | 0                          | -                          | -                          | %    |

| Maximum On Time Detect Delay                                                                         | V <sub>PCT</sub> = V <sub>PCT(peak)</sub> + 1 V                         | t <sub>PCT(delay)</sub>                              | -                          | 250                        | 375                        | ns   |

| Voltage Delta between PControl Voltage Needed to Generate PDRV Pulses and $V_{\text{EA}(\text{OL})}$ | $\Delta V_{EA} - V_{PCT(peak)}$                                         | V <sub>PCT(offset)</sub>                             | 250                        | 400                        | 550                        | mV   |

| PFC OVERVOLTAGE and UNDERVOLTAGE                                                                     | E                                                                       |                                                      | 1                          |                            |                            |      |

| Overvoltage Detector Threshold Voltage                                                               | Midpoint between high and low<br>threshold, V <sub>PControl</sub> = 4 V | V <sub>POVP</sub>                                    | 1.03*<br>V <sub>PREF</sub> | 1.05*<br>V <sub>PREF</sub> | 1.07*<br>V <sub>PREF</sub> | V    |

| Overvoltage Comparator Hysteresis Win-<br>dow                                                        | V <sub>PControl</sub> = 4V                                              | V <sub>POVP(HYS)</sub>                               | 5                          | 30                         | 60                         | mV   |

| Propagation Delay                                                                                    | V <sub>PFB</sub> = V <sub>PREF</sub> + 1 V                              | t <sub>POVP(delay)</sub>                             | -                          | 400                        | 800                        | ns   |

| Undervoltage Detector Threshold Voltage                                                              | V <sub>PFB</sub> increasing<br>V <sub>PFB</sub> decreasing              | V <sub>PUVP(high)</sub><br>V <sub>PUVP(low)</sub>    | -<br>175                   | 290<br>230                 | 350<br>-                   | mV   |

| Undervoltage Comparator Hysteresis                                                                   | V <sub>PFB</sub> increasing                                             | V <sub>PUVP(HYS)</sub>                               | 20                         | 60                         | 100                        | mV   |

| PFC DRIVER                                                                                           | •                                                                       | •                                                    | •                          |                            | •                          |      |

| PFC Driver Rise Time                                                                                 | 10% to 90% (Note 4)                                                     | t <sub>PDRV(rise)</sub>                              | -                          | 18                         | -                          | ns   |

| PFC Driver Fall Time                                                                                 | 90% to 10% (Note 4)                                                     | t <sub>PDRV(fall)</sub>                              | -                          | 9                          | -                          | ns   |

| PFC Driver High State Voltage                                                                        | I <sub>PDRV</sub> = -8 mA                                               | V <sub>PDRV(OH)</sub>                                | 14.00                      | 14.55                      | -                          | V    |

| PFC Driver Low State Voltage                                                                         | I <sub>PDRV</sub> = 8 mA                                                | V <sub>PDRV(OL)</sub>                                | -                          | 0.12                       | 0.50                       | V    |

4. Resistor/capacitor parallel combination (39 pF || 20 kΩ) between PDRV and driver supply and between PDRV and GND pins.

**Table 5. ELECTRICAL CHARACTERISTICS** ( $V_{HV}$  = open,  $V_{PEB}$  = 2.4 V,  $V_{PCS}$  = 0 V,  $V_{PZCD}$  = 5 V,  $V_{PControl}$  = open,  $V_{CC}$  = 15 V,  $V_{PDRV}$  = open,  $V_{HDRVlo}$  = open,  $V_{HVS}$  = 0 V,  $V_{HDRVhi}$  = open,  $V_{HBoost}$  = 15 V,  $C_{OSC}$  = 2200 pF,  $C_{VREF}$  = 0.1  $\mu$ F,  $C_{PCT}$  = 1000 pF, for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                        | Conditions                                                         | Symbol                    | Min  | Тур  | Max | Unit |

|----------------------------------------|--------------------------------------------------------------------|---------------------------|------|------|-----|------|

| HALF BRIDGE HIGH SIDE DRIVER           |                                                                    | ·                         |      |      |     |      |

| Half-Bridge High Side Driver Rise Time | 10% to 90% (Note 5)                                                | t <sub>HDRVhi(rise)</sub> | -    | 18   | —   | ns   |

| Half-Bridge High Side Driver Fall Time | 90% to 10% (Note 5)                                                | t <sub>HDRVhi(fall)</sub> | -    | 9    | -   | ns   |

| High State Voltage                     | I <sub>HDRVhi</sub> = -4 mA                                        | V <sub>HDRVhi(OH)</sub>   | 14.0 | 14.7 | -   | V    |

| Low State Voltage                      | I <sub>HDRVhi</sub> = 4 mA                                         | V <sub>HDRVhi(OL)</sub>   | -    | 0.06 | 0.5 | V    |

| High Side Driver Duty Ratio            | 10 to 90% to 10% transitions,<br>V <sub>HSVS</sub> = 50 V (Note 5) | D <sub>HDRVhiMAX</sub>    | 44   | 48   | 50  | %    |

| Boost Supply Undervoltage Threshold    |                                                                    | V <sub>HBoost(UVLO)</sub> | 4    | 6.1  | 8.0 | V    |

| Boost Current Consumption              | HDRVhi switching,<br>between HDRVhi and HVS (Note 5)               | I <sub>CC(Boost)</sub>    | -    | 0.1  | 0.5 | mA   |

| HVS Leakage Current                    | $T_J = 25^{\circ}C, V_{HVS} = 600 V, V_{HBoost} = 600 V$           | I <sub>HVS(off)</sub>     | -    | 0.1  | 1   | μΑ   |

# HALF BRIDGE LOW SIDE DRIVER

| Half-Bridge Low Side Driver Rise Time             | 10% to 90% (Note 5)                      | t <sub>HDRVIo(rise)</sub> | -  | 18   | -   | ns |

|---------------------------------------------------|------------------------------------------|---------------------------|----|------|-----|----|

| Half-Bridge Low Side Driver Fall Time             | 90% to 10% (Note 5)                      | t <sub>HDRVhi(fall)</sub> | -  | 9    | -   | ns |

| Half-Bridge Low Side Driver High State<br>Voltage | I <sub>HDRVI0</sub> = -4 mA              | V <sub>HDRVI0(OH)</sub>   | 14 | 14.7 | -   | V  |

| Half-Bridge Low Side Driver Low State<br>Voltage  | I <sub>HDRVIo</sub> = 4 mA               | V <sub>HDRVIo(OL)</sub>   | -  | 0.06 | 0.5 | V  |

| Half-Bridge Low Side Driver Duty Ratio            | 10 to 90% to 10% transitions<br>(Note 5) | D <sub>HDRVI0MAX</sub>    | 44 | 48   | 50  | %  |

| CROSSOVER DEAD TIME                               |                                          |                           | •  | •    |     |    |

| Delay from HDRVIo high to low to<br>HDRVhi low to high transition | V <sub>HVS</sub> = 50 V | t <sub>HDRVhi(h−l)</sub> | 500 | 785 | 950 | ns |

|-------------------------------------------------------------------|-------------------------|--------------------------|-----|-----|-----|----|

| Delay from HDRVhi high to low to<br>HDRVlo low to high transition | V <sub>HVS</sub> = 50 V | t <sub>HDRVhi(h−l)</sub> | 500 | 785 | 950 | ns |

#### HALF-BRIDGE DISABLE

| Half-Bridge Disable            | V <sub>OSC</sub> Decreasing | V <sub>HB(DIS)</sub>     | 1.550 | 1.955 | 2.300 | V  |

|--------------------------------|-----------------------------|--------------------------|-------|-------|-------|----|

| Half-Bridge Disable Hysteresis | V <sub>OSC</sub> Increasing | V <sub>HB(DIS-HYS)</sub> | -     | 130   | -     | mV |

5. Resistor/capacitor parallel combination (39 pF || 20 kΩ) between drive pin and driver supply and between HDRVxx and GND pins.

# **DETAILED OPERATING DESCRIPTION**

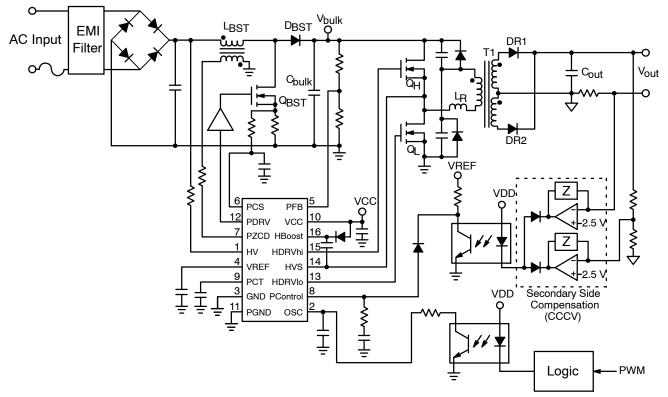

Figure 2. Simplified Application Block Diagram

### **OVERVIEW**

The NCL30051 is a combination of a PFC boost controller and a half-bridge resonant controller optimized for off-line LED lighting solutions. This device integrates all the features needed to implement a highly efficient and small form factor LED driver. It contains a critical conduction mode (CrM) power factor correction (PFC) controller and a half-bridge resonant (HBR) controller with a built-in 600 V driver. The half-bridge stage operates at a fixed frequency – greatly simplifying the control implementation. Output (current or voltage) regulation can be achieved by adjusting the PFC stage output voltage based on a control signal generated external to the NCL30051.

This device includes an enable input on the PFC feedback pin, open feedback loop protection and PFC overvoltage and undervoltage detectors. Other features included in the NCL30051 are a 600 V startup circuit and an adjustable frequency oscillator. The controllers are properly sequenced, simplifying the system design.

# THEORY OF OPERATION

The NCL30051 provides an innovative control mechanism compared to traditional two stage power conversion architectures. This unique regulation scheme offers extreme simplicity for certain applications, but at the

same time places constraints that have to be taken into account during the converter design.

Traditional 2-stage converters have independent control loops for the PFC stage and the step-down stage, allowing each converter output to be regulated on its own. The PFC stage is often designed for critical conduction (CrM) or continuous conduction mode (CCM) operation and the step-down stage is typically a current-mode/voltage-mode PWM controller geared for forward or flyback applications. More recently, some solutions such as the NCP1910 CCM PFC two stage combo from ON Semiconductor have become available which incorporates the half-bridge resonant converter topology which offers significant efficiency and EMI advantages. However, this HBR topology involves varying the switching frequency to regulate the output and hence adds further complexity to such combination controllers.

In contrast, the NCL30051 simplifies the overall approach significantly by implementing the HBR approach for the second stage converter at a fixed frequency. This simply means that the second-stage converter now operates in a non-regulating fixed-ratio voltage conversion mode. The implication of this approach is that output regulation control has to be provided by adjusting the output of the PFC front-end converter. The benefits of this approach can be summarized as follows:

- Low pin-count of controller combines strong feature set

- Low external component count

- ZVS of the second stage FETs without any tuning requirements

- High efficiency facilitates improved thermal performance

- Low EMI and easy filtering due to fixed frequency

- Facilitation of synchronous rectification control design

- Easier design of magnetic components (esp. Resonant transformer and inductor)

While the above listed benefits make this approach a very interesting proposition for many isolated applications with PFC front-end, it has to be implemented with some additional considerations.

The fact that the output regulation is achieved by adjusting the PFC output voltage, places additional limits on the PFC stage that is not needed in the traditional approach. Depending on the application and output requirements, this may not be much of a constraint. However, if the output variation requirements are significant, the PFC stage may not have enough dynamic range to provide sufficient output power control.

The other consideration is related to the response time to any output variations. In a true 2-stage conversion, the decoupling of the two stages allows a better transient response. In that case the PFC converter is constrained to a bandwidth much below the line frequency (typically < 20 Hz), whereas the second stage can be optimized to have a very fast dynamic response. In the NCL30051 application, the second stage has no independent output regulation ability, so the dynamic response is constrained by the PFC stage bandwidth. This limitation means that the approach is not suited for very fast-transient loads. However, a large number of applications (such as LED drivers and battery chargers) can easily accept the response times offered by the NCL30051 approach.

Output voltage ripple is another consideration when designing with the NCL30051. The low frequency ripple on the PFC output stage is determined by the size of the PFC capacitor. With no compensation in the second stage, the final output voltage ripple is simply a scaled version of the PFC output ripple determined by the fixed ratio of the second stage. Normally this type of ripple is not a concern for lighting applications as the ripple frequency (100/120 Hz) is above the eye response frequency or in the case of fixed output LED power supplies, there are secondary side constant current regulators that further reduces the ripple.

Finally, hold-up time is another matter to be considered when using this fixed-ratio converter approach. When the input voltage droops, the output of the PFC starts dropping at a rate determined by the bulk capacitance value and the load current. The output voltage follows this discharge rate with a fixed ratio. By increasing the bulk capacitance value, this discharge rate can be slowed down increasing hold-up time. However, this approach has practical limits and is not recommended for applications requiring a long hold-up time with no output voltage variation.

Figure 2 illustrates a typical NCL30051 2-stage converter implementation. As seen in the figure, the isolated second stage converter output value is processed by a compensation circuit in the secondary and an error signal is generated and coupled to the primary using an opto-coupler. On the primary side, this signal is fed to the PControl pin of NCL30051 through a reverse ORing diode. The PControl pin also has a default error signal generated by the PFC error amplifier. The lower of these two signals dominates and helps set the fixed ON time for the PFC block as described in earlier sections. In the intended implementation, the NCL30051's PFC error amplifier should be configured to set the maximum value of the output voltage and the secondary side feedback should be allowed to control it lower based on the output conditions.

# **DESIGN CONSIDERATIONS – POWER STAGE**

Given the unique nature of the NCL30051, certain power stage design considerations are applicable (for PFC and second-stage) as below. These design considerations are described for a constant current LED lighting application, but can also apply to constant voltage applications with minor variations.

# PFC Output (Vbulk) Voltage Range

The minimum bulk voltage setting is dictated by the requirement that the PFC output voltage be higher than the peak of the input line voltage at all times. Even though many lighting applications operate from a single voltage range which simplifies the analysis, we will consider an input range of 85-265 Vac which covers most regional requirements, this means the minimum bulk voltage is set in the range of 385-400 Vdc. However, if the circuit has to handle 277 Vac  $\pm 10\%$  input also (as in the case of US commercial lighting applications), the minimum bulk setting goes up to 435 Vdc. The maximum bulk setting is limited by component stress factors and other considerations. The major constraints are bulk capacitor, output (boost) diode, boost FET and the NCL30051 voltage rating.

While other power stage considerations are covered in the paragraphs below, the application of NCL30051 requires that the bulk voltage be limited to below 600 V maximum under all conditions. The NCL30051 high-voltage section is rated at 600 V – this includes pins HV and HVS. The HBoost and HDRVhi pins see the highest potential, given by Vbulk+Vcc. In normal operation the bulk is limited to 540 V based on the derating criteria. This is the same derating which would be applied to the 600 V output rectifier in the PFC stage.

## **PFC Output Capacitor - Cbulk**

The bulk capacitor is one of the most critical components in the PFC design. High value, high voltage capacitors are expensive and take up a large space. In traditional PFC applications, the voltage rating of this capacitor is about 450 V (some designers cut it to 420 V for cost savings), but for 277 Vac lighting applications, 450 V rating is not sufficient. As shown in the table above, if the output voltage is allowed to vary, the bulk voltage can go even higher. Availability of bulk capacitors above 450 V is limited. One solution is to take two capacitors and put them in series. The effective value of two series capacitors is lower, but for low-medium power applications, this should not be a big issue. For 600 V maximum bulk voltage, two 400 V capacitors need to be used, but for 90-135 Vac only applications, lower rated capacitors can be used. When putting capacitors in series, it is required to have a parallel high value resistor pair in order to ensure voltage sharing.

The effective bulk capacitance value also depends on the application requirements. Normal rule of thumb for traditional PFC circuits is to use around 1  $\mu$ F/W to achieve desired hold-up time and ripple performance. In this approach, due to absence of a regulated second stage, it may be prudent to increase the capacitance value if low ripple or fast transient response is required. Another factor in selecting the capacitor is that it handles high ripple current due to the CrM topology implemented here. The equations for ripple current through the capacitor are derived in ON Semiconductor application note AND8123 and should be used to determine that the selected capacitor can handle the ripple current without overheating or lifetime degradation.

### PFC Diode (D<sub>BST</sub>)

The PFC diode provides the rectification function and has to be rated above the peak value of Vbulk. In the CrM operation, with the diode current going to zero every cycle prior to its turn-off, the reverse recovery is not that prominent and an ultrafast diode can be used. In addition, there is little or no overshoot caused by the reverse recovery, so the FET voltage is also well contained. In most cases a 600 V diode is sufficient depending on the derating criteria.

# PFC Switch (Q<sub>BST</sub>)

Typically, the PFC switch is a MOSFET rated anywhere from 500 V to 650 V. Better commercial availability of higher voltage rated FETs in recent years has meant that the QBST is not a major constraint in implementation of variable Vbulk approach offered by NCL30051. However, depending on derating guidelines and practices, the 600 V rating of the FET may not be sufficient. In that case, a higher voltage FET is required.

# PFC Inductor (L<sub>BST</sub>)

The PFC inductor is designed using the standard CrM design equations. When the output voltage goes up from 390 V to 540 V, there is about 20% increase in value of

inductance required. Thus, variation in PFC voltage results in higher boost inductor value and size (and/or higher ripple current when the output voltage is higher).

## HBR Converter Design

The half-bridge resonant converter utilizes an LLC resonant circuit to achieve the ZVS of the primary switches and also to reduce the transition losses in the secondary. Additionally, this circuit offers a major benefit wherein the output inductor can be eliminated.

In traditional LLC approaches, when the second stage converter is regulated, the switching frequency of the HBR converter has to be varied to respond to load or line changes. As a result, operation near the resonant frequency is not always guaranteed and the efficiency takes a hit. Also, varying the frequency imposes additional design burden on the designer to ensure that the control circuit is stable and provides desired results over the full load and line range. The feedback design and loop closure is more challenging in this type of converter.

By keeping a constant switching frequency, not only is the control circuit simplified, the magnetics design also becomes easier. The transformer size can be reduced as it is designed for a single frequency and full optimization is available. Studies have shown that this approach leads to about 25-40% reduction in total magnetics area-product. Other design considerations for the LLC resonant converter remain the same as given in ON Semiconductor application note AND8311 and are not repeated here.

The power conversion architecture of the NCL30051 is ideal for many LED Lighting applications since it provides higher efficiency and power factor correction. Since hold-up time and output ripple are not major considerations in these applications, NCL30051 fits in very well. This means that it is ideal for fixed output voltage LED power supplies (ex: 24 Vdc and 48 Vdc) as well as constant current schemes where the output voltage varies depending on the number of LEDs and the variation of the LED forward voltage. This topology is best suited for applications where the output voltage variation is constrained to a ratio of about 1.5 for designs that require operation at 230 Vac.

# Supply Sequencing

The error amplifier of the PFC controller is enabled once  $V_{CC}$  reaches  $V_{CC(on)}$  and the PFB voltage exceeds  $V_{PUVP(high)}$ , typically 290 mV. Once enabled, the PControl voltage starts rising and when it exceeds  $V_{EA(OL)}$  and  $V_{CC}$  is above  $V_{CC(enable)}$ , the first PFC drive pulse is generated. The half-bridge driver is enabled after the first PFC drive pulse is generated. This ensures a monotonic output voltage rise as the input voltage to the half bridge stage is regulated.

In the event that  $V_{CC}$  falls below  $V_{CC(enable)}$  before the control voltage exceeds  $V_{EA(OL)}$ , the error amplifier will remain on and  $V_{CC}$  will fall to  $Vcc_{(OFF)}$  at which time the HV startup circuit will be enabled and a new startup sequence will be initiated.

## **High Voltage Startup Circuit**

The NCL30051 internal startup regulator eliminates the need for external startup components. In addition, this regulator increases the efficiency of the supply as it uses no power when in the normal mode of operation, but instead uses power supplied by an auxiliary winding. The startup regulator consists of a constant current source that supplies current from the high voltage line (V<sub>in</sub>) to the supply capacitor on the V<sub>CC</sub> pin (C<sub>CC</sub>). The startup current (I<sub>start</sub>) is typically 7.5 mA. The startup circuit is rated at a maximum voltage of 600 V.

Once  $C_{CC}$  is charged to 15.3 V ( $V_{CC(on)}$ ), the startup regulator is disabled and the PFC controller is enabled if the PFB voltage exceeds  $V_{PUVP(high)}$ . The startup regulator remains disabled until the lower supply threshold,  $V_{CC(off)}$ , (typically 9.3 V) is reached. Once reached, the drive outputs are disabled and the startup current source is enabled. Once the outputs are disabled, the bias current of the NCL30051 is reduced, allowing  $V_{CC}$  to charge back up.

The supply capacitor provides power to the controller while operating in the power up or self-bias mode. During the converter power up,  $C_{CC}$  must be sized such that a  $V_{CC}$  voltage greater than  $V_{CC(off)}$  is maintained while the auxiliary supply voltage is building up. Otherwise,  $V_{CC}$  will collapse and the controller will turn off. The IC bias current and gate charge load at the drive outputs must be considered to correctly size  $C_{CC}$ . The increase in current consumption due to external gate charge is calculated using Equation 1.

$$I_{CC(qate charge)} = f \cdot Q_{G}$$

(eq. 1)

where, f is the operating frequency and  $Q_G$  is the gate charge of the external MOSFETs.

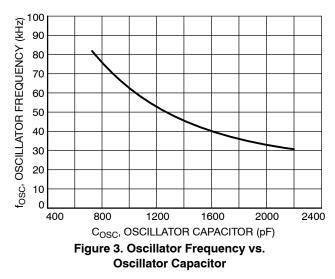

### Main Oscillator

The oscillator frequency is set by the oscillator capacitor,  $C_{OSC}$ , on the OSC pin. The oscillator operates at a fixed 80% duty ratio. A current source charges  $C_{OSC}$  to its peak voltage, typically 5 V. Once the peak voltage is reached, the charge current is disabled and  $C_{OSC}$  is discharged down to 3 V by another current source. The charge and discharge currents are typically 173 and 692  $\mu$ A, respectively. The oscillator frequency vs oscillator capacitance graph is shown in Figure 3.

An internal clock signal is generated by dividing the oscillator frequency by two. This clock signal is used to control the half-bridge driver. The half-bridge duty ratio is limited to 50%. The PFC is not synchronized to the oscillator as it operates in variable frequency mode.

#### Half-Bridge Disable

The half-bridge oscillator and the half-bridge low and high side drivers are disabled once the voltage on the OSC pin is brought below the half-bridge disable threshold,  $V_{HB(DIS)}$  (typically 1.955 V). This can be accomplished by pulling down on the oscillator pin using a transistor or open collector/drain device. Once the oscillator pin is released the oscillator capacitor returns to its normal operating range and the half bridge is re-enabled. The low side half-bridge driver generates the first drive pulse during initial power up or re-starting of the half-bridge. This ensures boost voltage is generated to supply the high side driver.

#### Voltage Reference

The internal voltage reference,  $V_{REF}$ , is brought out of the controller to ease compensation requirements. The reference voltage is typically 7.0 V. A 0.1 µF bypass capacitor is required for stability. The reference should not be loaded with external circuitry.

## **PFC Regulator**

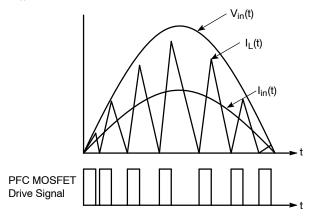

The PFC inductor current,  $I_{L(t)}$ , reaches zero at the end of the switch cycle as shown in Figure 4 and the average input current,  $I_{in(t)}$ , is in phase with the ac line voltage,  $V_{in(t)}$ .

Figure 4. Inductor Current in CrM

High power factor is achieved in CrM by maintaining a constant on time  $(t_{on})$  for a given RMS input voltage  $(V_{ac(RMS)})$  and load conditions. Equation 2 shows the relationship between on time and system operating conditions.

$$t_{on} = \frac{2 \cdot P_{out} \cdot L}{\eta \cdot V_{ac(RMS)}^{2}} \qquad (eq. 2)$$

where,  $P_{out}$  is the output power, L is the PFC inductor inductance and  $\eta$  is the system efficiency.

### **On Time Control**

The NCL30051 controls the on time by charging an external timing capacitor on the PCT pin,  $C_T$ , with a constant current source,  $I_{PCT(C)}$ . The  $C_T$  ramp is then compared to the control voltage,  $V_{PControl}$ . The control voltage is constant for a given RMS line voltage and output load, satisfying Equation 2. The block diagram of the constant on time section is shown in Figure 5.

Figure 5. Constant On Time Control Block Diagram

The PControl voltage is internally clamped between 2.25 V and 5.65 V. A voltage offset,  $V_{PCT(offset)}$ , is added to the C<sub>T</sub> ramp to account for the control voltage range. This allows the PFC stage to stop the drive pulses (0% duty ratio) and regulate at light loads. The delta between the PControl voltage needed to generate a PDRV pulse and the minimum PControl Clamp voltage is  $V_{PCT(offset)}$ .

The timing capacitor is discharged and held low once the  $C_T$  ramp voltage plus offset reaches  $V_{PControl}$ . The PFC drive pulse terminates once the  $C_T$  voltage reaches its peak voltage threshold,  $V_{PCT(peak)}$ . A new cycle starts once the inductor current reaches zero detected by a transition on the ZCD pin or the maximum off time has been reached.

The timing capacitor is sized such that the  $C_T$  ramp peak voltage is reached at low line and full load. In this operating mode  $V_{PControl}$  is at its maximum. Equation 3 is used to calculate the on time for a given  $C_T$ .

$$t_{on(MAX)} = \frac{C_{T} \cdot V_{PCT(peak)}}{I_{PCT(C)}} \qquad (eq. 3)$$

Substituting  $t_{on}$  in Equation 2 with Equation 3 and rearranging Equation 4 provides a maximum value for  $C_{T}$ .

$$C_{\mathsf{T}} \geq \frac{2 \cdot \mathsf{P}_{\mathsf{out}} \cdot \mathsf{L} \cdot \mathsf{I}_{\mathsf{PCT}(\mathsf{C})}}{\eta \cdot \mathsf{V}_{\mathsf{ac}(\mathsf{RMS})}{}^2 \cdot \mathsf{V}_{\mathsf{PCT}(\mathsf{peak})}} \tag{eq. 4}$$

where,  $V_{PCT(peak)}$ , is the maximum PCT voltage, typically 3.0 V.

## **PFC Startup**

The output of the error amplifier is pulled low with an internal pull down transistor when the supply voltage has not reached  $V_{CC(on)}$  or if there is a PFC undervoltage fault. This ensures a soft–start sequence once the PFC is enabled and eliminates output voltage overshoot during on/off tests. Once the error amplifier is enabled the output of the error amplifier charges quickly to the minimum clamp voltage.

### **Off Time Control**

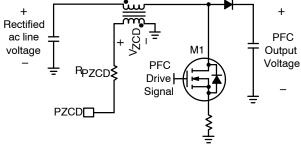

The PFC off time varies with the instantaneous line voltage and it is adjusted every cycle to allow the inductor current to reach zero before the next switch cycle begins. The inductor is demagnetized once its current reaches zero. Once the inductor is demagnetized the drain voltage of the PFC switch begins to drop. The inductor demagnetization is detected by sensing the voltage across the inductor using an auxiliary winding. This winding is commonly known as a zero crossing detector (ZCD) winding. This winding provides a scaled version of the inductor voltage. Figure 6 shows the ZCD winding arrangement.

Figure 6. ZCD Winding Implementation

A negative voltage appears on the ZCD winding while the PFC switch is on. The PZCD voltage is positive while the PFC switch is off and current is flowing through the inductor. The PZCD voltage drops to and rings around zero volts once the inductor is demagnetized. Once a negative transition is detected in the PZCD pin the next switch cycle commences. A positive transition (corresponding to the PFC switch turn off) arms the ZCD detector to prevent false triggering. The arming of the ZCD detector is typically 2.1 V (V<sub>PZCD</sub> increasing) and the triggering is typically 1.5 V (V<sub>PZCD</sub> decreasing).

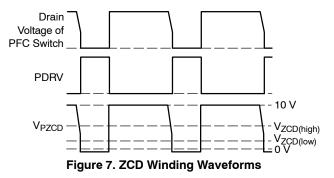

The PZCD pin is internally clamped to 10 V with a zener diode. A resistor in series with the ZCD pin is required to limit the current into the PZCD pin. The zener diode prevents the voltage from exceeding the 10 V clamp or going below ground. Figure 7 shows typical ZCD waveforms.

During startup there are no ZCD transitions to enable the PFC switch. A watchdog timer enables the PFC controller if no switch pulses are detected for a period of 180  $\mu$ s (typical). The watchdog timer is also useful while operating at light load because the amplitude of the ZCD signal may be very small to cross the ZCD thresholds. The watchdog timer is reset at the beginning of a PFC drive pulse and in a PFC undervoltage fault.

The watchdog timer is disabled if the voltage on the PZCD pin is above  $V_{ZCD(high)}$ . It is re-enabled once the voltage on the PZCD pin drops below  $V_{ZCD(low)}$ . Disabling the watchdog timer allows the PFC to be disabled by pulling up on the PZCD pin. Care should be taken to limit the current into the PZCD pin to prevent exceeding the internal 10 V zener clamp.

## PFC Compensation

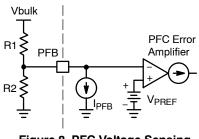

A transconductance error amplifier regulates the PFC output voltage, Vbulk, by comparing the PFC feedback signal to an internal 2.5 V reference. As shown in Figure 8 a resistor divider from the PFC output voltage consisting of R1 and R2 generates the PFC feedback signal.

Figure 8. PFC Voltage Sensing

The feedback signal is applied to the amplifier inverting input. The internal 2.5 V reference,  $V_{PREF}$ , is applied to the amplifier non-inverting input. The reference is trimmed during manufacturing to achieve an accuracy of  $\pm 3.2\%$ . Figure 8 shows the PFC error amplifier and sensing network. Equation 5 is used to calculate the values of the PFC feedback network.

$$V_{PFC} = V_{PREF} \cdot \frac{R_1 + R_2}{R_2} + I_{PFB} \cdot R_1 \quad (eq. 5)$$

A transconductance amplifier has a voltage–to–current gain, gm. That is, the output current is controlled by the differential input voltage. The NCL30051 amplifier has a typical gm of 95  $\mu$ S. The PControl pin provides access to the amplifier output for compensation. The compensation network is ground referenced allowing the PFC feedback signal to be used to detect an overvoltage condition.

The compensation network on the PControl pin is selected to filter the bulk voltage ripple such that a constant control voltage is maintained across the ac line cycle. A capacitor between the PControl pin and ground sets a pole. A pole at or below 20 Hz is enough to filter the ripple voltage for a 50 and 60 Hz system. The low frequency pole,  $f_p$ , of the system is calculated using Equation 6.

$$f_{\rm p} = \frac{\rm gm}{2\pi C_{\rm PControl}} \qquad (\rm eq.~6)$$

where, C<sub>PControl</sub> is the capacitor on the PControl pin to ground.

A key feature to using a transconductance type amplifier, is that the input is allowed to move independently with respect to the output, since the compensation capacitor is connected to ground. This allows dual usage of the feedback pin by the error amplifier and by the overvoltage comparator.

#### **PFC Undervoltage**

The NCL30051 safely disables the controller if the PFB pin is left open. An undervoltage detector disables the controller if the voltage on the PFB pin is below  $V_{PUVP(low)}$ , typically 0.23 V. A 1.2  $\mu$ A (typical) pull down current source, I<sub>PFB</sub>, ensures  $V_{PFB}$  falls below  $V_{PUVP(low)}$  if the PFB pin is floating. The PFB pull down current source affects the PFC output voltage regulation setpoint.

#### **PFC Overvoltage**

An overvoltage detector monitors the PFC feedback voltage and disables the PFC driver if an overvoltage condition is detected. This is set internal to the IC at 5% above the nominal setting of the PFC voltage If an OVP event is detected, drive pulses are suppressed until the over voltage condition is removed. The overvoltage detector tolerance is better than  $\pm 2\%$ . The overvoltage detector threshold, V<sub>POVB</sub> is the midpoint between the PFC driver disable and enable thresholds. The overvoltage comparator hysteresis is the voltage difference between the disable and enable thresholds. An overvoltage condition is detected once V<sub>PFB</sub> exceeds V<sub>POVP</sub> by half of V<sub>POVP(HYS)</sub>. The controller is re-enabled once V<sub>PFB</sub> drops below V<sub>POVP</sub> by half of V<sub>POVP(HYS)</sub>.

## PFC Overcurrent

The PFC current is monitored by means of an overcurrent detector. The PCS pin provides access to the overcurrent detector. The PFC drive pulse is terminated if the voltage on the PCS pin exceeds the overcurrent threshold,  $V_{PCS(ILIM)}$ . This comparison is done on a cycle by cycle basis. The overcurrent threshold is typically 0.84 V.

The current sense signal is prone to leading edge spikes caused by the power switch transitions. The NCL30051 has leading edge blanking circuitry that blocks out the first 110 ns (typical) of each current pulse.

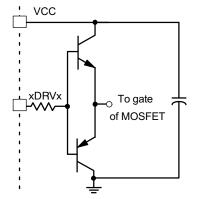

# **PFC Driver**

The PFC driver source and sink impedances are typically 60 and 15  $\Omega$ , respectively. Depending on the external MOSFET gate charge requirements, an external driver may be needed to drive the PFC power switch. A driver such as the one shown in Figure 9 can be easily implemented using small bipolar transistors.

Figure 9. External Driver

#### Half-Bridge Driver

The half-bridge stage operates at a fixed 50% duty ratio. The oscillator frequency is divided by two before it is applied to the half-bridge controller.

The half-bridge controller has a low side driver, HDRVlo, and a 600 V high side driver, HDRVhi. The built in high voltage driver eliminates the need for an external transformer or dedicated driver. A built-in delay between each drive transition eliminates the risk of cross conduction. The delay is typically 785 ns. The typical duty ratio of each half-bridge driver is 48%.

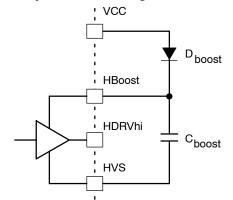

The high side driver is connected between the HBoost and the HVS pins as shown in Figure 10.

Figure 10. Half-bridge High Side Driver

A boost circuit comprised of  $D_{boost}$  and  $C_{boost}$  generates the supply voltage for the high side driver. Once HDRVlo turns on, the HVS pin is effectively grounded through the external power switch. This allows  $C_{boost}$  to charge to  $V_{CC}$ . Once HDRVlo turns off, HVS floats high and  $D_{boost}$  is reversed biased. An undervoltage detector monitors the HBoost voltage. Once the HBoost voltage is greater than  $V_{Boost(UV)}$ , typically, 6.1 V, the high side driver is enabled. The low side driver generally starts before the high side driver because the boost voltage is generated by the low side driver switch transitions.

The half-bridge low side driver source and sink impedances are typically 75 and 15  $\Omega$ , respectively. The half-bridge high side driver source and sink impedances are typically 75 and 15  $\Omega$ , respectively. Depending on the

external MOSFETs gate charge requirements, an external driver may be needed to drive the low and high side power switches.

### Analog and Power Ground

The NCL30051 has an analog ground, GND, and a power ground, PGND, terminal. GND is used for analog connections such as VREF and OSC. PGND is used for high current connections such as the gate drivers. It is recommended to have independent analog and power ground planes and connect them at a single point, preferably at the ground terminal of the system. This will prevent high current flowing on PGND from injecting noise in GND. The PGND connection should be as short and wide as possible to reduce inductance–induced spikes.

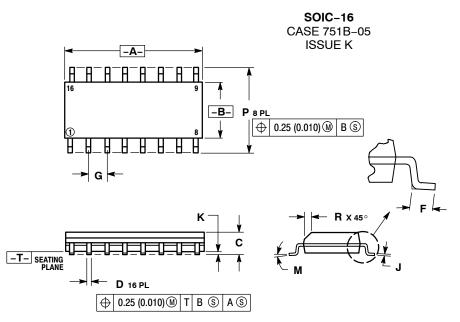

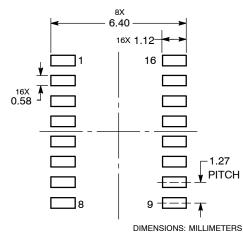

#### PACKAGE DIMENSIONS

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INCHES |       |  |

|-----|--------|--------|--------|-------|--|

| DIM | MIN    | MAX    | MIN    | MAX   |  |

| Α   | 9.80   | 10.00  | 0.386  | 0.393 |  |

| В   | 3.80   | 4.00   | 0.150  | 0.157 |  |

| C   | 1.35   | 1.75   | 0.054  | 0.068 |  |

| D   | 0.35   | 0.49   | 0.014  | 0.019 |  |

| F   | 0.40   | 1.25   | 0.016  | 0.049 |  |

| G   | 1.27   | BSC    | 0.050  | ) BSC |  |

| J   | 0.19   | 0.25   | 0.008  | 0.009 |  |

| K   | 0.10   | 0.25   | 0.004  | 0.009 |  |

| M   | 0 °    | 7°     | 0°     | 7 °   |  |

| Р   | 5.80   | 6.20   | 0.229  | 0.244 |  |

| R   | 0.25   | 0.50   | 0.010  | 0.019 |  |

SOLDERING FOOTPRINT