# High Performance Dual MOSFET Gate Driver

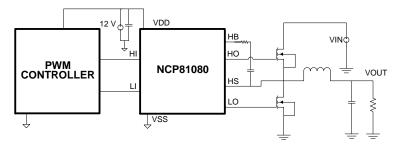

The NCP81080 is a high performance dual MOSFET gate driver optimized to drive half bridge N–Channel MOSFETs. The NCP81080 uses a bootstrap technique to ensure a proper drive of the high–side power switch. A high floating top driver design can accommodate HB voltage as high as 180 V. The NCP81080 has an internal anti–cross conduction circuit with a 135 ns fixed internal dead–time to prevent current shoot–through. The NCP81080 is available in 2x2mm DFN and SOIC packages.

# Features

- Drives Two N–Channel MOSFETs in High–Side and Low–Side Configuration

- Floating Top Driver Accommodates Boost Voltage up to 180 V

- Switching Frequency up to 500 Khz

- Current Shoot–Through Protection

- 135 ns Fixed internal Dead–Time

- 44 ns Rising and 30 ns Falling Propagation Delay Times

- 0.5 A peak Source Current with 0.8 A Peak Sink Current

- 19 ns Rise/17 ns Fall Times with 1000-pF Load

- High–Side & Low–Side UVLO Protection

# Applications

- Telecom and Datacom

- Isolated Non–Isolated Power Supply Architectures

- Class–D Audio Amplifiers

- Two Switch and Active Clamp Forward Converters

- Motor Drives

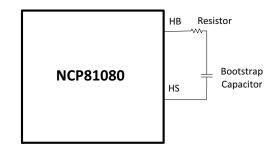

Figure 1. Typical Application Circuit

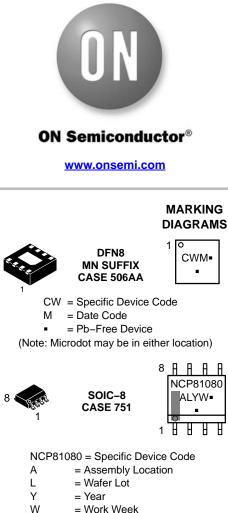

- = WORK Week

- = Pb-Free Package

(Note: Microdot may be in either location)

# **ORDERING INFORMATION<sup>†</sup>**

| Device        | Package            | Shipping              |

|---------------|--------------------|-----------------------|

| NCP81080MNTBG | DFN8<br>(Pb–Free)  | 3000 / Tape &<br>Reel |

| NCP81080DR2G  | SOIC8<br>(Pb–Free) | 2500 / Tape &<br>Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

1

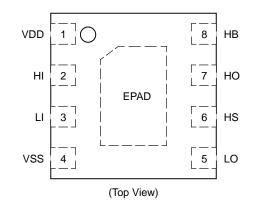

# Table 1. PIN DESCRIPTION TABLE

| Pin No. | Symbol | Description                                 |

|---------|--------|---------------------------------------------|

| 1       | VDD    | Positive supply for the low-<br>side driver |

| 2       | HI     | High-Side Input                             |

| 3       | LI     | Low–Side Input                              |

| 4       | VSS    | Negative Supply Return                      |

| 5       | LO     | Low–Side Output                             |

| 6       | HS     | High–Side Source                            |

| 7       | HO     | High-Side Output                            |

| 8       | HB     | High-Side Bootstrap                         |

| 9       | EPAD   | Connect EPAD to VSS                         |

# Table 2. MAXIMUM RATINGS

| Parameter                            |                                             | Value                                                                | Unit |  |

|--------------------------------------|---------------------------------------------|----------------------------------------------------------------------|------|--|

| VDD                                  |                                             | -0.3 to 24                                                           | V    |  |

| V <sub>HB</sub> – V <sub>SS</sub>    |                                             | -0.3 to 200                                                          | V    |  |

| V <sub>HO</sub> – V <sub>HS</sub>    | DC                                          | –0.3 to V <sub>HB</sub> + 0.3                                        | V    |  |

|                                      | Repetitive Pulse < 100 ns                   | -2 to V <sub>HB</sub> + 0.3, (V <sub>HB</sub> - V <sub>HS</sub> <20) |      |  |

| V <sub>HS</sub> – V <sub>SS</sub>    | DC                                          | -20 to 200 - VDD                                                     | V    |  |

| V <sub>LO</sub> – V <sub>SS</sub>    | DC                                          | -0.3 to VDD + 0.3                                                    | V    |  |

|                                      | Repetitive pulse < 100 ns                   | -2 to VDD + 0.3                                                      |      |  |

| V <sub>HI</sub> , V <sub>LI</sub>    |                                             | -10 to 24                                                            | V    |  |

| V <sub>HB –</sub> V <sub>HS</sub>    |                                             | -0.3 to 24                                                           | V    |  |

| I <sub>Diode</sub>                   | AC (Peak current)                           | 8                                                                    | А    |  |

| Operating                            | virtual Junction Temp Range, T <sub>J</sub> | -40 to 170                                                           | °C   |  |

| St                                   | orage Temperature, T <sub>STG</sub>         | -65 to 150                                                           | °C   |  |

| Lead Temperature (Soldering, 10 sec) |                                             | +300                                                                 | °C   |  |

| НВМ                                  |                                             | 800                                                                  | V    |  |

|                                      | CDM                                         | 2000                                                                 | V    |  |

# Table 3. RECOMMENDED OPERATING CONDITIONS

|                 | Parameter                            | Min                   | Nom | Max                  | Unit   |

|-----------------|--------------------------------------|-----------------------|-----|----------------------|--------|

| V <sub>DD</sub> | Supply Voltage Range                 | 5.5                   | 12  | 20                   | V      |

| V <sub>HS</sub> | Voltage on HS (DC)                   | -10                   |     | 180                  |        |

| V <sub>HB</sub> | Voltage on HB                        | V <sub>HS</sub> + 5.5 |     | V <sub>HS</sub> + 20 |        |

|                 | Voltage Slew Rate on HS              |                       |     | 30                   | V / ns |

| TJ              | Operating Junction Temperature Range | -40                   |     | +140                 | °C     |

# **Table 4. ABSOLUTE MAXIMUM RATINGS**

| Thermal Characteristic                                             | DFN | SOIC | Unit |

|--------------------------------------------------------------------|-----|------|------|

| $\theta_{\text{JA}}$ Junction to Ambient thermal resistance        | 97  | 146  | °C/W |

| $\theta_{\text{JCT}}$ Junction to case (Top) thermal resistance    | 181 | 72   |      |

| $\theta_{\text{JCB}}$ Junction to case (Bottom) thermal resistance | 1.9 | 67   |      |

| $\psi_{\text{JT}}$ Junction to top characterization parameter      | 2.2 | 7.2  |      |

| $\psi_{JB}$ Junction to board characterization parameter           | 2.0 | 64   |      |

| Moisture Sensitivity Level – QFN Package                           | MSL | 1    |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

\*The maximum package power dissipation must be observed.

2) JESD 51–5 (1S2P Direct–Attach Method) with 0 LFM

3) JESD 51–7 (1S2P Direct–Attach Method) with 0 LFM

\*All signals referenced to VSS unless otherwise noted.

#### **Table 5. ELECTRICAL CHARACTERISTICS**

Unless otherwise stated:  $T_A = T_J = -40^{\circ}C$  to  $140^{\circ}C$ ; VDD = VHB = 12 V, VHS = VSS = 0 V, No load on LO or HO

|                   | Parameter                      | Test Condition                            | Min | Тур  | Max | Units |

|-------------------|--------------------------------|-------------------------------------------|-----|------|-----|-------|

| JPPLY CURR        | ENTS                           |                                           |     |      |     | -     |

| I <sub>DD</sub>   | VDD quiescent current          | $V_{LI} = V_{HI} = 0$                     |     | 0.85 | 1.6 | mA    |

| I <sub>DDO</sub>  | VDD operating current          | $f = 500 \text{ kHz}, C_{LOAD} = 0$       |     | 5.1  | 9.0 |       |

|                   |                                | $f = 300 \text{ kHz}, C_{LOAD} = 0$       |     | 3.5  | 6.5 |       |

| I <sub>HB</sub>   | Boot voltage quiescent current | $V_{LI} = V_{HI} = 0 V$                   |     | 0.65 | 1.6 |       |

| I <sub>HBO</sub>  | Boot voltage operating current | $f = 500 \text{ kHz}, C_{LOAD} = 0$       |     | 4.8  | 9.0 |       |

|                   |                                | $f = 300 \text{ kHz}, C_{LOAD} = 0$       |     | 3.4  | 6.5 |       |

| I <sub>HBS</sub>  | HB to Vss quiescent current    | V <sub>HS</sub> = V <sub>HB</sub> = 110 V |     | 8.0  | 100 | μΑ    |

| I <sub>HBSO</sub> | HB to Vss operating current    | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 0.2  |     | mA    |

INPUT

| $V_{HIH,} V_{LIH}$ | Input voltage high        | 2.0 |     |     |   |

|--------------------|---------------------------|-----|-----|-----|---|

| $V_{HIL,} V_{LIL}$ | Input voltage low         |     |     | 0.8 |   |

| R <sub>IN</sub>    | Input Pulldown Resistance | 100 | 175 | 350 | ľ |

#### **UNDERVOLTAGE PROTECTION (UVLO)**

| VDD | VDD rising threshold     | 3.4 | 4.4  | 5.4 | V |

|-----|--------------------------|-----|------|-----|---|

| VDD | VDD Threshold hysteresis |     | 0.4  |     |   |

| VHB | VHB rising threshold     | 3.4 | 4.4  | 5.4 |   |

| VHB | VHB Threshold hysteresis |     | 0.35 |     |   |

**BOOTSTRAP DIODE**

| VF              | Low-current forward voltage              | I <sub>VDD</sub> – HB = 100 μA    | 0.61 | 0.85 | V |

|-----------------|------------------------------------------|-----------------------------------|------|------|---|

| V <sub>FI</sub> | High-current forward voltage             | $I_{VDD} - HB = 100 \text{ mA}$   | 0.93 | 1.1  |   |

| R <sub>D</sub>  | Dynamic resistance, $\Delta VF/\Delta I$ | $I_{VDD}$ – HB = 100 mA and 80 mA | 2.1  | 3.5  | Ω |

LO GATE DRIVER

| V <sub>LOL</sub>         | Low level output voltage  | I <sub>LO</sub> = 100 mA                            | 0.31 | 1.2 | V |

|--------------------------|---------------------------|-----------------------------------------------------|------|-----|---|

| V <sub>LOH</sub>         | High level output voltage | $I_{LO}$ = -100 mA, $V_{LOH}$ = $V_{DD}$ - $V_{LO}$ | 0.75 | 1.6 |   |

|                          | Peak Pull–Up Current      | $V_{LO} = 0 V$                                      | 0.55 |     | Α |

|                          | Peak Pull–Down Current    | V <sub>LO</sub> = 12 V                              | 0.8  |     |   |

| R <sub>O, Unbiased</sub> |                           | VCC = VSS                                           | 20k  |     | Ω |

# Table 5. ELECTRICAL CHARACTERISTICS

Unless otherwise stated:  $T_A = T_J = -40^{\circ}$ C to  $140^{\circ}$ C; VDD = VHB = 12 V, VHS = VSS = 0 V, No load on LO or HO

|                          | Parameter                                         | Test Condition                                                   | Min | Тур  | Max | Units |

|--------------------------|---------------------------------------------------|------------------------------------------------------------------|-----|------|-----|-------|

| HO GATE DRIVER           | ł                                                 |                                                                  |     |      |     |       |

| V <sub>HOL</sub>         | Low level output voltage                          | I <sub>HO</sub> = 100 mA                                         |     | 0.3  | 1.2 | V     |

| V <sub>HOH</sub>         | High level output voltage                         | $I_{HO} = -100 \text{ mA}, V_{HOH} = V_{HB} - V_{HO}$            |     | 0.71 | 1.6 | 1     |

|                          | Peak Pull–Up Current                              | V <sub>HO</sub> = 0 V                                            |     | 0.55 |     | А     |

|                          | Peak Pull–Down Current                            | V <sub>HO</sub> = 12 V                                           |     | 0.8  |     | 1     |

| R <sub>O, Unbiased</sub> |                                                   | HB – HS = 0 V                                                    |     | 20k  |     | Ω     |

| PROPAGATION D            | ELAYS                                             |                                                                  |     |      |     |       |

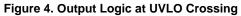

| t <sub>DLFF</sub>        | PWM falling to VLo falling                        | C <sub>LOAD</sub> = 0                                            |     | 30   |     | ns    |

| <b>t</b> DHFF            | PWM falling to VHO falling                        | $C_{LOAD} = 0$                                                   |     | 30   |     | 1     |

| tDLRR                    | PWM rising to VLO rising                          | $C_{LOAD} = 0$                                                   |     | 44   |     | 1     |

| <b>t</b> DHRR            | PWM rising to VHO rising                          | $C_{LOAD} = 0$                                                   |     | 44   |     | 1     |

| DEAD-TIME                | •<br>•                                            |                                                                  |     |      |     |       |

| Fixed Deadtime           | Internal Fixed Dead-Time                          |                                                                  |     | 135  |     | ns    |

| DEAD-TIME MAT            | CHING                                             |                                                                  |     |      |     | -     |

| t <sub>DTM</sub>         | LI OFF, HI ON                                     |                                                                  |     | 10   |     | ns    |

| OUTPUT RISE AN           | ID FALL TIME                                      |                                                                  |     |      |     |       |

| t <sub>R</sub>           | LO, HO                                            | C <sub>LOAD</sub> = 1000 pF                                      |     | 19   |     | ns    |

| t <sub>F</sub>           | LO, HO                                            | C <sub>LOAD</sub> = 1000 pF                                      |     | 17   |     | 1     |

| MISCELLANEOUS            | 6                                                 |                                                                  |     |      |     |       |

|                          | Minimum input pulse width that changes the output |                                                                  |     | 30   |     | ns    |

|                          | Bootstrap diode turn-off time                     | I <sub>F</sub> = 20 mA, I <sub>REV</sub> = 0.5 A<br>(Notes 1, 2) |     | 50   |     |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product Product parametric performance is indicated in the Electrical Characteristics for the listed test condition performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Typical values for TA = 25°C

IF: Forward current applied to bootstrap diode, IREV: Reverse current applied to bootstrap diode.

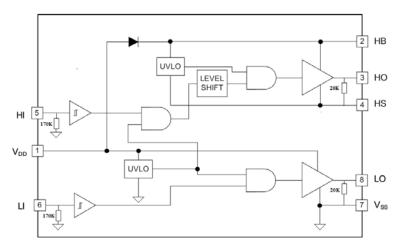

Figure 2. Internal Block Diagram

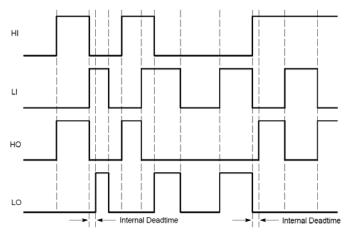

Figure 3. Timing Diagram

NOTE: The NCP81080 has a fixed internal dead-time of 135 ns.

Figure 5. Dead-Time Matching

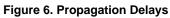

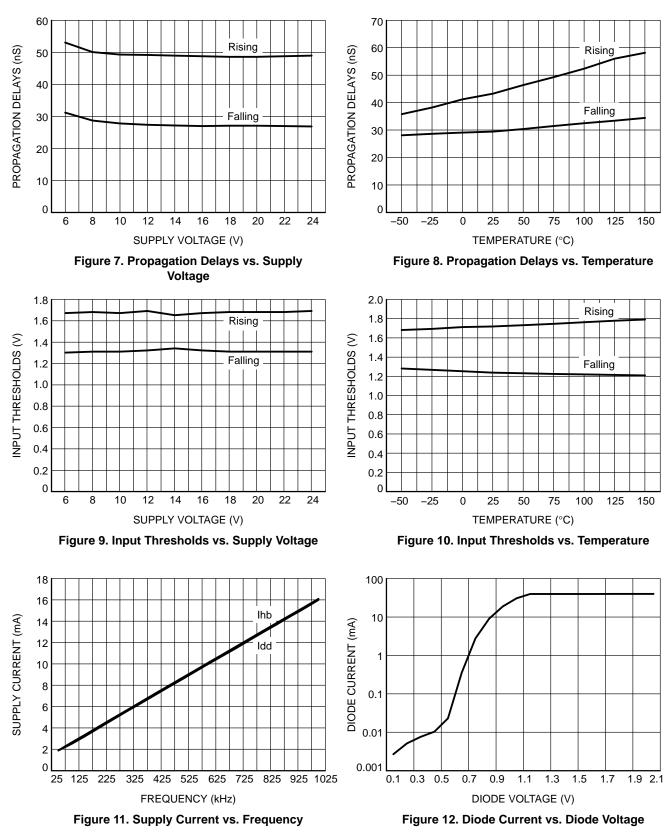

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

# APPLICATION INFORMATION

The NCP81080 is a high performance dual MOSFET gate driver optimized to drive half bridge N–Channel MOSFETs. A high and a Low input signals are all that is required to properly drive the power stage. The input signals are independently controlled and monitored by an anti–cross conduction circuit in order to prevent current shoot through. The NCP81080 has UVLO protections for the high–side and low–side drivers forcing the outputs low if the bias supplies drop below the specified UVLO thresholds. The NCP81080 also features an on–chip high voltage bootstrap diode which reduces the external component count. The NCP81080 has a fixed internal dead–time of 135 ns.

#### **Driver Supply Voltage**

As a general rule of thumb the local bypass should be 20 times the bootstrap capacitor. It is recommended to use a 4.7  $\mu$ F bypass capacitor on VDD to VSS. The bootstrap capacitor is recharged on a cycle by cycle basis through the bootstrap diode from the VDD bypass capacitor. The charging cycle involves bursts in peak currents that require careful considerations by keeping a tight layout and short loops to avoid reliability issues.

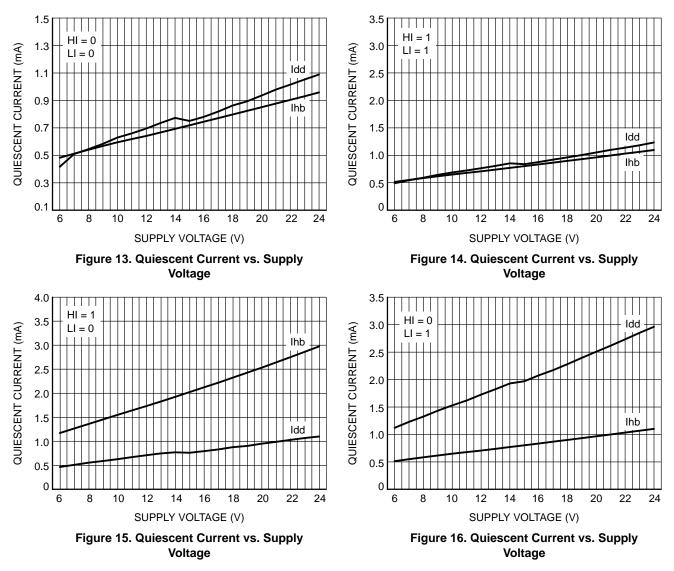

If for any reason the application requires the VDD voltage to discharge to ground at rapid rates  $(3 + V/\mu s)$  the user is required to add an external diode between the supply voltage and the bypass capacitor.

Figure 17. VDD Diode

# Low-Side Driver

The low side driver is designed to drive low  $RDS_{ON}$  N-channel MOSFETs. The typical output resistances for the driver are 7.5 ohms for sourcing and 3.1 ohms for sinking gate current. The bias to the low side driver is internally connected to the VDD supply and VSS. When the driver is enabled, the driver's output is in phase with LI. When the NCP81080 is disabled, the low side gate is held low.

# High-Side Driver

The high side driver is designed to drive a floating low  $RDS_{ON}$  N-channel MOSFET. The output resistances for the driver are 7.1 ohms for sourcing and 3.1 ohms for sinking gate current. The bias voltage for the high side driver is realized by an external bootstrap supply circuit which is connected between the HB and HS Pins.

The peak diode current that the part can handle is 8 A. It is required to add an external limiting resistor in series with the bootstrap capacitor to prevent damaging the internal diode.

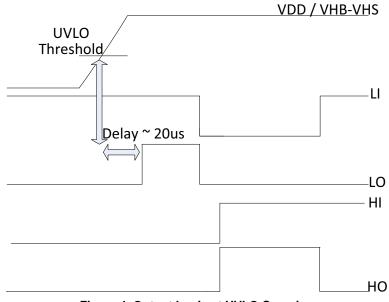

At power–up, the HS Pin is at ground, the bootstrap capacitor will charge up to VDD through the internal diode. The designer must factor in at least 3 time constants (RC) plus the internal UVLO delays (20  $\mu$ s typical) before the output can react to a logic input (Refer to Figure 4). If for any reason the voltage across the bootstrap capacitor drops below UVLO, it is required to charge the capacitor back up to VDD while accounting for 3 time constants and the 20  $\mu$ s UVLO delay before the High–Side channel can react to an HI input.

When the HI pin goes high, the high side driver will begin to turn the high side MOSFET ON by pulling charge out of the bootstrap capacitor. As the external MOSFET turns ON, the HS Pin will rise up to VIN, forcing the HB Pin to VIN +  $V_{BstCap}$  which is enough gate to source voltage to hold the switch On. To complete the cycle, the MOSFET is switched OFF by pulling the gate down to the voltage at the HS Pin. When the low side MOSFET turns On, the HS Pin is pulled to ground. This allows the bootstrap capacitor to charge back up to VDD. The high–side driver's output is in phase with the HI input. When the driver is disabled, the high side gate is held low.

# Table 6. TYPICAL EXTERNAL CURRENT LIMITING RESISTOR VALUES

| VDD (V) | Bootstrap Capacitor<br>(μF) | External Resistor<br>(ohms) |

|---------|-----------------------------|-----------------------------|

| 12      | 0.1                         | 2                           |

| 12      | 1                           | 3                           |

| 18      | 0.1                         | 3                           |

Figure 18. External Current Limiting Resistor

# UVLO (Under Voltage Lockout)

The bias supplies of the high-side and low-side drivers have UVLO protection. The VDD UVLO disables both drivers when the VDD voltage crosses the specified threshold. The typical rising threshold is 4.4 V with 0.4 V hysteresis. The VHB UVLO disables only the high-side driver when the VHB to VHS is below the specified threshold. The typical VHB UVLO rising threshold is 4.4 V with 0.35 V hysteresis.

At power up, when the supply voltage ramps up to set VDD and crosses the UVLO thresholds, **users must take into account a 20 \mus delay** before the output drivers can react to a logic input. The 20  $\mu$ s delay applies to both High–side and Low–side drivers. Figure 4 only shows the delay for the low–side channel.

#### Input Stage

The input stage of the NCP81080 is TTL compatible. The logic rising threshold level is 2.0 V and the logic falling threshold is 0.8 V.

#### **Cross-Conduction Protection**

The NCP81080's inputs HI & LI are controlled independently. In order to prevent the power stage MOSFETs from turning on at the same time an internal logic circuit is implemented to monitor the state of HI & LI. If both input signals are high at the same time, the output signals HO & LO are forced low. (See Timing Diagram)

#### **UVLO Crossing**

When VDD & VHB cross their respective UVLO thresholds if HI and LI were already set the NCP81080 will keep HO pulled Low until it detects a rising edge on HI, however LO will follow LI allowing the Low–Side FET to turn on. (Refer to Figure 4)

#### Layout Guidelines

Gate drivers experience high di/dt during the switching transitions. So, the inductance at the gate drive traces must be minimized to avoid excessive ringing on the switch node. Gate drive traces should be kept as short and wide (>20 mil) as practical. The input capacitor must be placed as close as possible to the IC. Connect the VSS pin of the NCP81080 as close as possible to the source of the lower MOSFET. The use of vias is highly desirable to maximize thermal conduction away from driver.

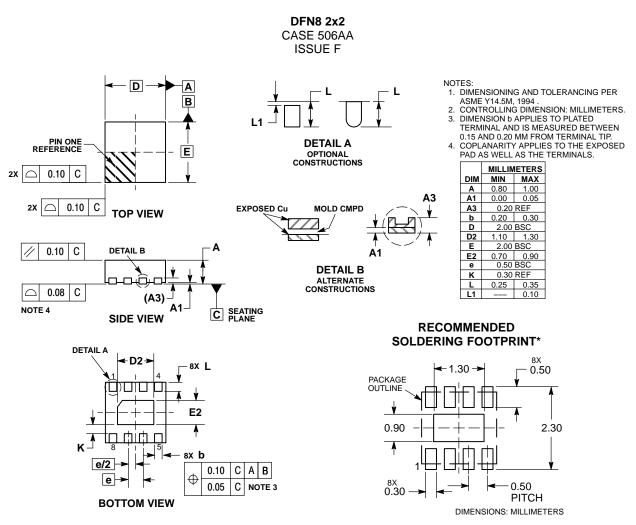

# PACKAGE DIMENSIONS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

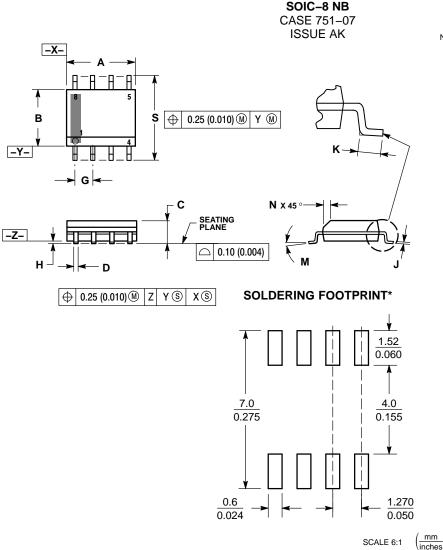

# PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- 3.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) 4.

- PER SIDE. DIMENSION D DOES NOT INCLUDE DAMBAR 5. PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07. 6

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| κ   | 0.40        | 1.27 | 0.016     | 0.050 |

| Μ   | 0 °         | 8 °  | 0 °       | 8 °   |

| Ν   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

٥