# STPTIC-47G2

### Parascan<sup>™</sup> tunable integrated capacitor

**Datasheet - production data**

### Features

- High power capability

- 5:1 tuning range

- High linearity

- High quality factor (Q)

- Low leakage current

- Compatible with high voltage control IC (STHVDAC series)

- Available in wafer level chip scale package:

WLCSP package 0.61 x 0.66 x 0.3 mm

- ECOPACK<sup>®</sup>2 compliant component

#### Benefit

• RF tunable passive implementation in mobile phones to optimize antenna radiated performance

### Applications

- Cellular antenna open loop tunable matching network in multi-band GSM/WCDMA/LTE mobile phone

- Open loop tunable RF filters

### Description

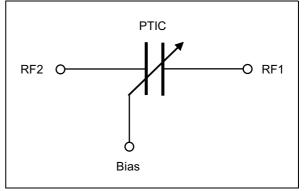

The ST integrated tunable capacitor offers excellent RF performance, low power consumption and high linearity required in adaptive RF tuning applications. The fundamental building block of PTIC is a tunable material called Parascan<sup>™</sup>, which is a version of barium strontium titanate (BST) developed by Paratek Microwave.

BST capacitors are tunable capacitors intended for use in mobile phone application and dedicated to RF tunable applications. These tunable capacitors are controlled through an extended bias voltage ranging from 1 to 24 V. The implementation of BST tunable capacitor in mobile phones enables significant improvement in terms of radiated performance making the performance almost insensitive to the external environment.

#### Figure 1. PTIC functional block diagram

TM: Parascan is a trademark of Paratek Microwave Inc.

DocID028154 Rev 1

This is information on a product in full production.

## 1 Electrical characteristics

|                       |                                                          | ,                       |      |

|-----------------------|----------------------------------------------------------|-------------------------|------|

| Symbol                | Parameter                                                | Rating                  | Unit |

| P <sub>IN</sub>       | Input peak power RF <sub>IN</sub> (CW mode)/all RF ports | +40                     | dBm  |

| V <sub>ESD(HBM)</sub> | Human body model, JESD22-A114-B, all I/O                 | Class 1B <sup>(1)</sup> | V    |

| V <sub>ESD(MM)</sub>  | Machine model, JESD22-A115-A, all I/O                    | 100                     | V    |

| T <sub>device</sub>   | Device temperature                                       | +125                    | °C   |

| T <sub>stg</sub>      | Storage temperature                                      | -55 to +150             | C    |

| V <sub>x</sub>        | Bias voltage                                             | 25                      | V    |

#### Table 1. Absolute maximum ratings (limiting values)

1. Class 1B defined as passing 500 V, but fails after exposure to 1000V ESD pulse.

#### Table 2. Recommended operating conditions

| Symbol              | Parameter             |      | Unit |      |      |

|---------------------|-----------------------|------|------|------|------|

|                     | Falanielei            | Min. | Тур. | Max. | Unit |

| P <sub>IN</sub>     | RF input power        |      | +33  |      | dBm  |

| F <sub>OP</sub>     | Operating frequency   | 700  |      | 2700 | MHz  |

| T <sub>device</sub> | Device temperature    |      |      | +100 | °C   |

| T <sub>OP</sub>     | Operating temperature | -30  |      | +85  | C    |

| V <sub>BIAS</sub>   | Bias voltage          | 1    |      | 24   | V    |

| Symbol           | Parameter                   | Conditions                                                      |      | Value |      |       |  |  |

|------------------|-----------------------------|-----------------------------------------------------------------|------|-------|------|-------|--|--|

| Symbol           | Parameter                   | Conditions                                                      | Min  | Тур   | Мах  | Unit  |  |  |

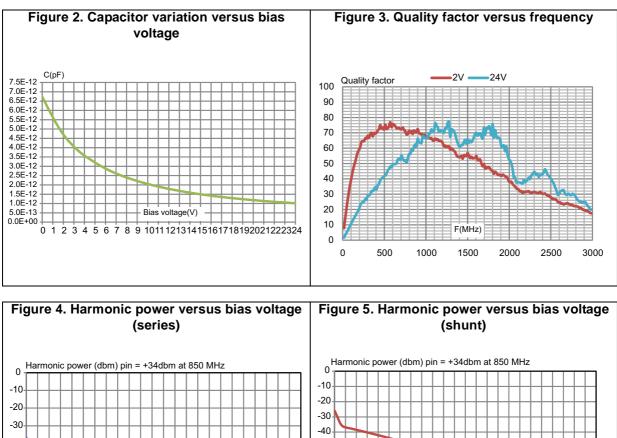

| C <sub>1V</sub>  | capacitor at 1 V bias       | STPTIC-47G2                                                     | 4.84 | 5.5   | 6.16 | pF    |  |  |

| C <sub>2V</sub>  | capacitor at 2 V bias       | STPTIC-47G2                                                     |      | 4.7   |      | pF    |  |  |

| C <sub>24V</sub> | capacitor at 24 V bias      | STPTIC-47G2                                                     | 0.86 | 0.94  | 1.02 | pF    |  |  |

| ΔC               | Tuning range                | Ratio between C <sub>1V</sub> /C <sub>24V</sub> <sup>(1)</sup>  | 5/1  |       |      |       |  |  |

| ١L               | Leakage current             | Measured with V <sub>bias</sub> = 24 V                          |      |       | 100  | nA    |  |  |

| Q <sub>LB</sub>  | Quality factor              | Measured at 700 MHz at 2 V                                      | 55   | 65    |      |       |  |  |

| Q <sub>HB</sub>  | Quality factor              | Measured at 2700 MHz at 2 V                                     | 35   | 50    |      |       |  |  |

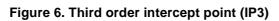

| IP3              | Third order intercept point | $V_{bias} = 1 V^{(2)(4)}$                                       | 52   | 60    |      | dBm   |  |  |

| 11-2             |                             | $V_{\text{bias}} = 24 V^{(2)(4)}$                               |      | 75    |      | UDIII |  |  |

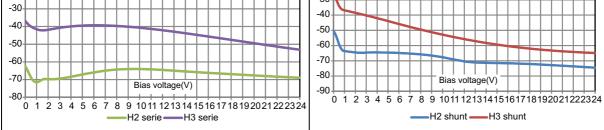

| H2               | Second harmonic             | $V_{\text{bias}} = 1 V^{(3)(4)}$                                |      | -65   | -45  | dBm   |  |  |

| 112              |                             | $V_{\text{bias}} = 24 V^{(3)(4)}$                               |      | -75   |      | ubiii |  |  |

| H3               | Third harmonic              | $V_{bias} = 1 V^{(3)(4)}$                                       |      | -35   | -30  | dBm   |  |  |

| пэ               |                             | $V_{\text{bias}} = 24 V^{(3)(4)}$                               |      | -65   |      | UDIII |  |  |

| +                | Transition time             | Average for any transition between $C_{min}$ to $C_{max}^{(5)}$ |      | 40    |      | 110   |  |  |

| t <sub>T</sub>   | I ransition time            | Average transition between $C_{max}$ to $C_{min}^{(5)}$         |      | 20    |      | μs    |  |  |

Table 3. Representative performance (T<sub>amb</sub> = 25 °C otherwise specified)

1. Measured at low frequency

2.  $F_1$  = 894 MHz,  $F_2$  = 849 MHz,  $P_1$  = +25 dBm,  $P_2$  = +25 dBm,  $2f_1$  -  $f_2$  = 939 MHz

3. 850 MHz, P<sub>in</sub> = +34 dBm

4. IP3 and harmonics are measured in the shunt configuration in a 50  $\Omega$  environment

5. One or both of  $\mathrm{RF}_{\mathrm{in}}$  and  $\mathrm{RF}_{\mathrm{out}}$  must be connected to DC ground, using the HVDAC turbo mode

DocID028154 Rev 1

### 2 Package information

- Epoxy meets UL94, V0

- Lead-free package

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com.* ECOPACK<sup>®</sup> is an ST trademark.

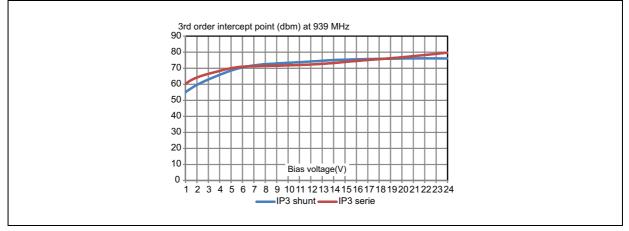

### 2.1 Flip-Chip package information

Figure 7. Flip-Chip package outline

The land pattern below is recommended for soldering the STPTIC-G2 on PCB.

NC stands for No Connect, this pad must not be connected on application board. Please leave this pad floating.

|                         |     | -   |       |     |     |     |     |     |     |     |     |       |    |     |     |     |

|-------------------------|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-------|----|-----|-----|-----|

| Dimensions (micron)     | A1  | A2  | B1    | B2  | В4  | C1  | C2  | D1  | D2  | D3  | E1  | E2    |    |     |     |     |

| STPTIC-15/27/33/39/47G2 | 640 |     |       |     | 120 |     |     |     |     |     |     |       |    |     |     |     |

| STPTIC-56G2             | 710 | 590 | 120   | 400 | 190 | 85  | 420 | 200 | 90  | 290 | 125 | 165   |    |     |     |     |

| STPTIC-68G2             | 780 | )   | 0 120 | 120 | 120 | 120 | 120 | 400 | 260 | 00  | 420 | 200 3 | 30 | 230 | 125 | 105 |

| STPTIC-82G2             | 880 |     |       |     | 360 |     |     |     |     |     |     |       |    |     |     |     |

| Tolerance               | ±30 | ±30 | ±15   | ±10 | ±15 | ±15 | ±10 | ±20 | ±20 | ±40 | ±20 | ±20   |    |     |     |     |

Table 4. Flip-Chip package dimensions

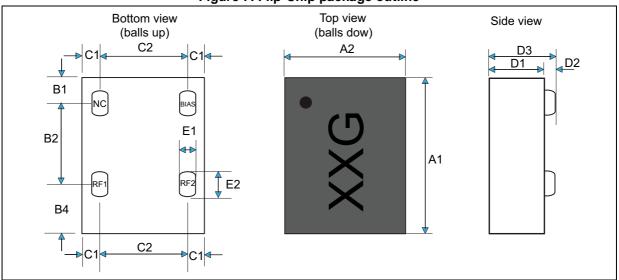

#### Figure 8. Recommended PCB land pattern for Flip-Chip package

#### Table 5. Dimensions

| Dimensions              | L1  | W1  | L3  | L2  | W2  | L4  | X1  | X2  | Y1  | Y2  |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Typical values (micron) | 160 | 160 | 260 | 210 | 210 | 310 | 320 | 270 | 240 | 190 |

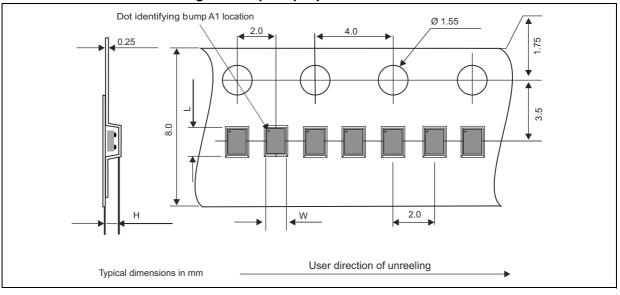

### 2.2 Packing information

#### Figure 9. Flip-Chip tape and reel outline

Table 6. Dimensions

| Pocket dimensions       | L   | W   | н   |

|-------------------------|-----|-----|-----|

| STPTIC-15/27/33/39/47G2 | 730 | 680 | 380 |

| STPTIC-56G2             | 800 | 680 | 380 |

| STPTIC-68G2             | 870 | 680 | 380 |

| STPTIC-82G2             | 970 | 680 | 380 |

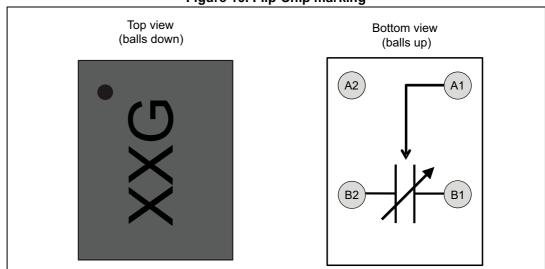

#### Figure 10. Flip-Chip marking

#### Table 7. Pinout description

| Pad / ball number | Pin name | Description                      |

|-------------------|----------|----------------------------------|

| A1                | DC bias  | DC bias voltage                  |

| B1                | RF2      | RF input / output <sup>(1)</sup> |

| A2                | NC       | Not connected                    |

| B2                | RF1      | RF input / output                |

1. When connected in shunt, please connect RF2 (B1 ball) to GND

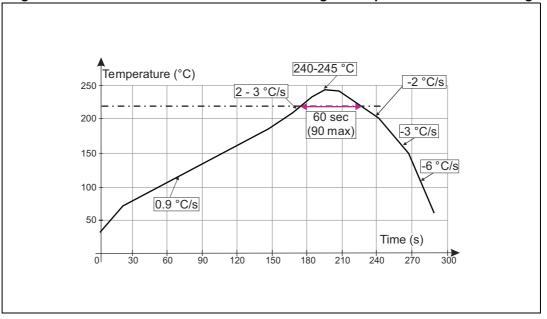

## 3 Reflow profile

Minimize air convection currents in the reflow oven to avoid component movement.

| Drafila                                         | Va            | lue     |

|-------------------------------------------------|---------------|---------|

| Profile                                         | Typical       | Max.    |

| Temperature gradient in preheat (T = 70-180 °C) | 0.9 °C/s      | 3 °C/s  |

| Temperature gradient (T = 200-225 °C)           | 2 °C/s        | 3 °C/s  |

| Peak temperature in reflow                      | 240-245 °C    | 260 °C  |

| Time above 220 °C                               | 60 s          | 90 s    |

| Temperature gradient in cooling                 | -2 to -3 °C/s | -6 °C/s |

| Time from 50 to 220 °C         160 to 220 s     |               |         |

#### Table 8. Recommended values for soldering reflow

## 4 Evaluation board

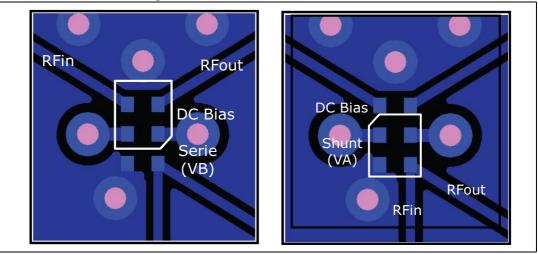

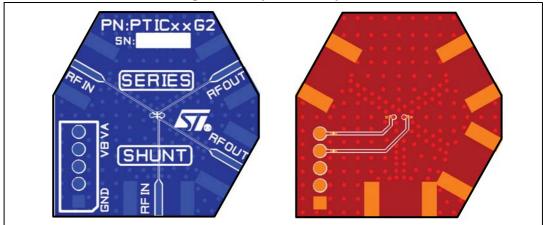

Figure 12. Series and shunt connection

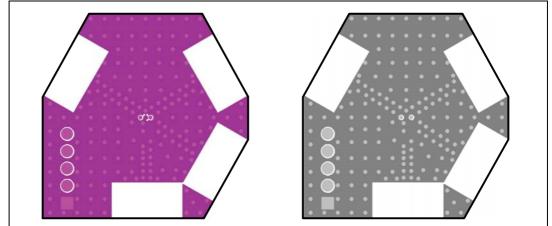

Figure 13. Layer 1 and layer 4

Figure 14. Layer 2 and layer 3

## 5 Ordering information

|                        | Tigure 1                                          | <u>.                                    </u> |                                                                                                                      | ormation schen                                          |                                  |                        |

|------------------------|---------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------|------------------------|

| ST                     | PTIC                                              | -                                            | 47                                                                                                                   | G                                                       | 2                                | C5                     |

| Manufacturer           | Product family                                    | -                                            | <u>Capacitor</u><br>value                                                                                            | Linearity                                               | Tuning                           | Package                |

| ST<br>Microelectronics | PTIC<br>Parascan™ tunable<br>Integrated capacitor |                                              | 12 = 1.2 pF<br>27 = 2.7 pF<br>33 = 3.3 pF<br>39 = 3.9 pF<br>47 = 4.7 pF<br>56 = 5.6 pF<br>68 = 6.8 pF<br>82 = 8.2 pF | F: Standard (x24)<br>G: Standard (x24)<br>L: High (x48) | 1 = 4/1 tuning<br>2 = 5/1 tuning | M6 : QFN<br>C5 : WLCSP |

Figure 15. Ordering information scheme

#### Table 9. Ordering information

| Part number   | Marking | Base qty | Package   | Delivery mode |

|---------------|---------|----------|-----------|---------------|

| STPTIC-47G2C5 | 47G     | 15 000   | Flip-Chip | Tape and reel |

## 6 Revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 23-Jul-2015 | 1        | Initial release. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID028154 Rev 1