- Dual Circuits Capable of Driving High-Capacitance Loads at High Speeds

- Output Supply Voltage Range up to 24 V

- Low Standby Power Dissipation

# description

The SN75372 is a dual NAND gate interface circuit designed to drive power MOSFETs from TTL inputs. It provides high current and voltage levels necessary to drive large capacitive loads at high speeds. The device operates from a  $V_{CC1}$  of 5 V and a  $V_{CC2}$  of up to 24 V.

The SN75372 is characterized for operation from 0°C to 70°C.

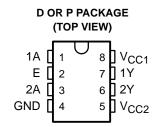

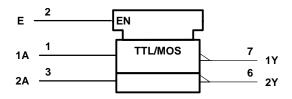

# logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

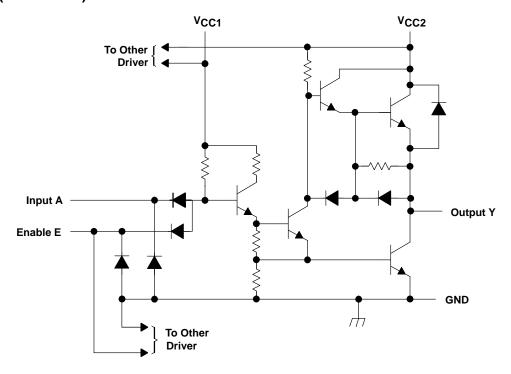

# schematic (each driver)

SLRS029 - D3004, JULY 1986

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC1</sub> (see Note 1)             | 0.5 V to 7 V                 |

|-----------------------------------------------------------------|------------------------------|

| Supply voltage range, V <sub>CC2</sub>                          | 0.5 V to 25 V                |

| Input voltage                                                   | 5.5 V                        |

| Peak output current, (t <sub>w</sub> < 10 ms, duty cycle < 50%) | 500 mA                       |

| Continuous total power dissipation                              | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub>            | 0°C to 70°C                  |

| Storage temperature range                                       | 65°C to 150°C                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    | 260°C                        |

NOTE 1: Voltage values are with respect to network GND.

# **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> = 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |  |  |

|---------|---------------------------------------|------------------------------------------------|---------------------------------------|--|--|

| D       | 725 mW                                | 5.8 mW/°C                                      | 464 mW                                |  |  |

| Р       | 1000 mW                               | 8.0 mW/°C                                      | 640 mW                                |  |  |

# recommended operating conditions

|                                                | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC1</sub>               | 4.75 | 5   | 5.25 | V    |

| Supply voltage, V <sub>CC2</sub>               | 4.75 | 20  | 24   | V    |

| High-level input voltage, VIH                  | 2    |     |      | V    |

| Low-level input voltage, V <sub>IL</sub>       |      |     | 8.0  | V    |

| High-level output current, IOH                 |      |     | -10  | mA   |

| Low-level output current, IOL                  |      |     | 40   | mA   |

| Operating free-air temperature, T <sub>A</sub> | 0    |     | 70   | °C   |

SLRS029 - D3004, JULY 1986

# electrical characteristics over recommended ranges of $V_{CC1},\ V_{CC2},\$ and operating free-air temperature (unless otherwise noted)

| PARAMETER                      |                                                          | TEST CONDI               | MIN                                                         | TYP <sup>†</sup>                    | MAX                   | UNIT                  |      |    |  |

|--------------------------------|----------------------------------------------------------|--------------------------|-------------------------------------------------------------|-------------------------------------|-----------------------|-----------------------|------|----|--|

| VIK                            | Input clamp voltage                                      |                          | I <sub>I</sub> = -12 mA                                     |                                     |                       |                       | -1.5 | V  |  |

| Vous High lovel output voltage |                                                          | V <sub>IL</sub> = 0.8 V, | I <sub>OH</sub> = -50 μA                                    | V <sub>CC2</sub> -1.3               | V <sub>CC2</sub> -0.8 |                       | V    |    |  |

| VOH                            | OH High-level output voltage                             |                          | V <sub>IL</sub> = 0.8 V,                                    | $I_{OH} = -10 \text{ mA}$           | V <sub>CC2</sub> -2.5 | V <sub>CC2</sub> -1.8 |      | V  |  |

|                                |                                                          |                          | V <sub>IH</sub> = 2 V,                                      | $I_{OL} = 10 \text{ mA}$            |                       | 0.15                  | 0.3  |    |  |

| VOL                            | L Low-level output voltage                               |                          | V <sub>CC2</sub> = 15 V to 24 V,<br>I <sub>OL</sub> = 40 mA | V <sub>IH</sub> = 2 V,              |                       | 0.25                  | 0.5  | ٧  |  |

| ٧F                             | Output clamp-diode forward voltage                       |                          | V <sub>I</sub> = 0,                                         | IF = 20mA                           |                       |                       | 1.5  | V  |  |

| 11                             | Input current at maximum input voltage                   |                          | V <sub>I</sub> = 5.5 V                                      |                                     |                       |                       | 1    | mA |  |

|                                | Aliah lavalianut sumat                                   |                          | V. 0.4V                                                     |                                     |                       |                       | 40   |    |  |

| ΊΗ                             | High-level input current                                 | Any E                    | V <sub>I</sub> = 2.4 V                                      |                                     |                       |                       | 80   | μΑ |  |

|                                | Low-level input current                                  | Any A                    | V <sub>I</sub> = 0.4 V                                      |                                     |                       | -1                    | -1.6 | mA |  |

| ΊL                             | Low-level input current                                  | Any E                    | V  = 0.4 V                                                  |                                     |                       | -2                    | -3.2 | ША |  |

| ICC1(H)                        | Supply current from $V_{CC1}$ , both outputs high        | 1                        | V <sub>CC1</sub> = 5.25 V,                                  | V <sub>CC2</sub> = 24 V,            |                       | 2                     | 4    | mA |  |

| ICC2(H)                        | Supply current from V <sub>CC2</sub> , both outputs high |                          | All inputs at 0 V,                                          | No load                             |                       |                       | 0.5  | mA |  |

| ICC1(L)                        | Supply current from V <sub>CC1</sub> , both outputs low  | 1                        | V <sub>CC1</sub> = 5.25 V,                                  | V <sub>CC2</sub> = 24 V,            |                       | 16                    | 24   | mA |  |

| ICC2(L)                        | Supply current from V <sub>CC2</sub> , both outputs low  | 1                        | All inputs at 5 V,                                          | No load                             |                       | 7                     | 13   | mA |  |

| ICC2(S)                        | Supply current from V <sub>CC2</sub> , standby condition |                          | V <sub>CC1</sub> = 0,<br>All inputs at 5 V,                 | V <sub>CC2</sub> = 24 V,<br>No load |                       |                       | 0.5  | mA |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC1} = 5$  V,  $V_{CC2} = 20$  V, and  $T_A = 25$ °C.

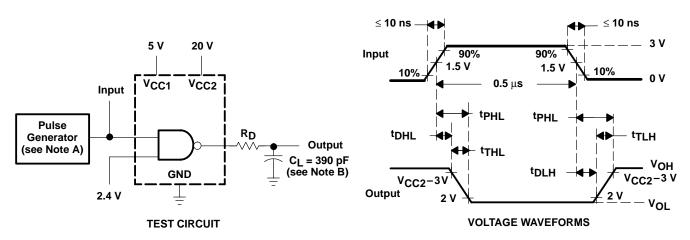

# switching characteristics, $V_{CC1}$ = 5 V, $V_{CC2}$ = 20 V, $T_A$ = 25°C

|                  | PARAMETER                                        |                          | TEST CONDITIONS        |                 |    | TYP | MAX | UNIT |

|------------------|--------------------------------------------------|--------------------------|------------------------|-----------------|----|-----|-----|------|

| <sup>t</sup> DLH | Delay time, low-to-high-level output             |                          |                        | Ω, See Figure 1 |    | 20  | 35  | ns   |

| <sup>t</sup> DHL | Delay time, high-to-low-level output             |                          |                        |                 |    | 10  | 20  | ns   |

| <sup>t</sup> TLH | Transition time, low-to-high-level output        | C <sub>1</sub> = 390 pF, | R <sub>D</sub> = 10 Ω, |                 |    | 20  | 30  | ns   |

| tTHL             | Transition time, high-to-low-level output        | TCL = 390 pr,            | KD = 10 sz,            |                 |    | 20  | 30  | ns   |

| tPLH             | Propagation delay time, low-to-high-level output |                          |                        |                 | 10 | 40  | 65  | ns   |

| tPHL             | Propagation delay time, high-to-low-level output |                          |                        |                 | 10 | 30  | 50  | ns   |

# PARAMETER MEASUREMENT INFORMATION

- NOTES: A. The pulse generator has the following characteristics: PRR = 1 MHz,  $Z_O \approx 50~\Omega$ .

- B. C<sub>L</sub> includes probe and jig capacitance.

Figure 1. Test Circuit and Voltage Waveforms, Each Driver

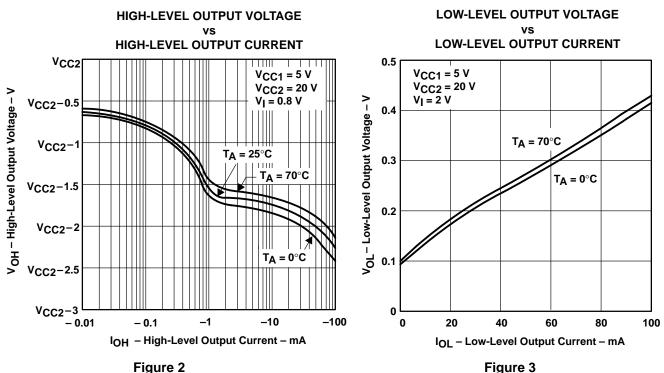

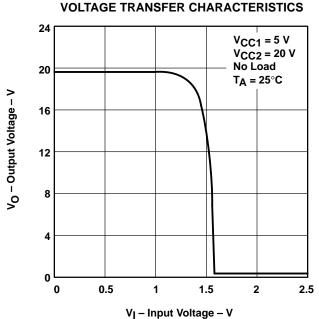

# TYPICAL CHARACTERISTICS

## TYPICAL CHARACTERISTICS

Figure 4

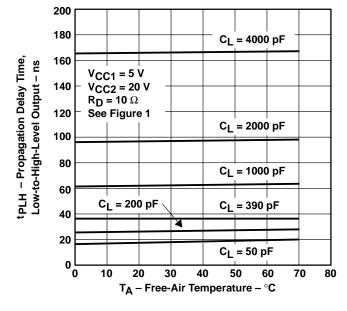

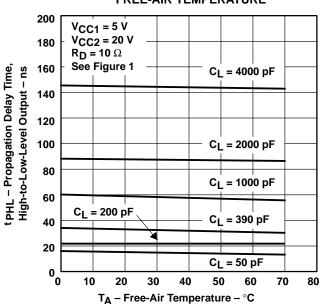

# PROPAGATION DELAY TIME,

# **LOW-TO-HIGH-LEVEL OUTPUT** FREE-AIR TEMPERATURE

Figure 6

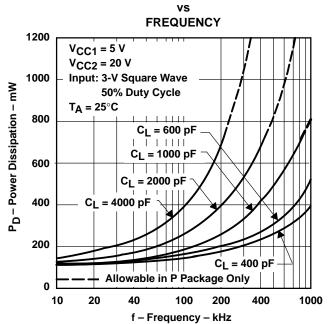

# **POWER DISSIPATION (BOTH DRIVERS)**

Figure 5

# PROPAGATION DELAY TIME, **HIGH-TO-LOW-LEVEL OUTPUT**

# FREE-AIR TEMPERATURE

Figure 7

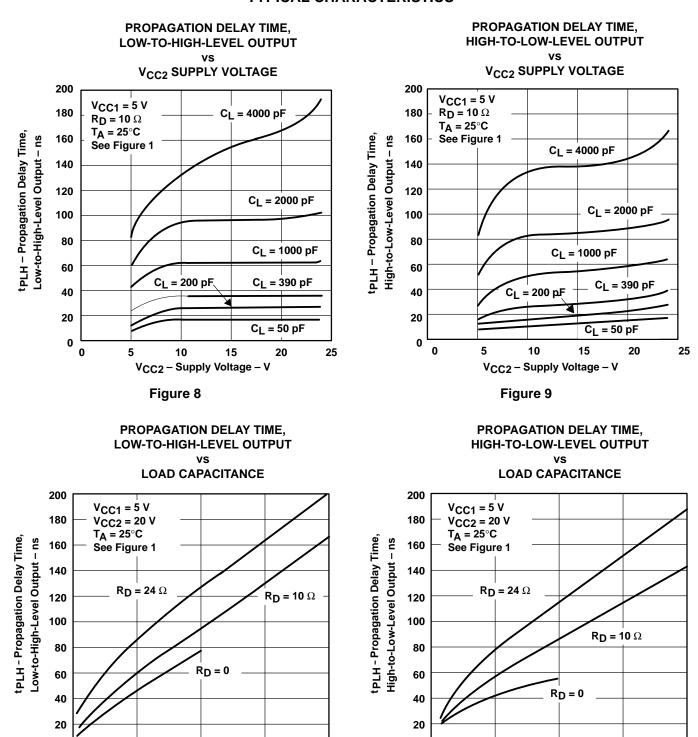

# **TYPICAL CHARACTERISTICS**

NOTE: For  $R_D = 0$ , operation with  $C_L > 2000 \, pF$  violates absolute maximum current rating.

2000

C<sub>L</sub> – Load Capacitance – pF

Figure 10

4000

0

0

1000

Figure 11

2000

C<sub>L</sub> - Load Capacitance - pF

3000

4000

0

0

## **APPLICATION INFORMATION**

# driving power MOSFETs

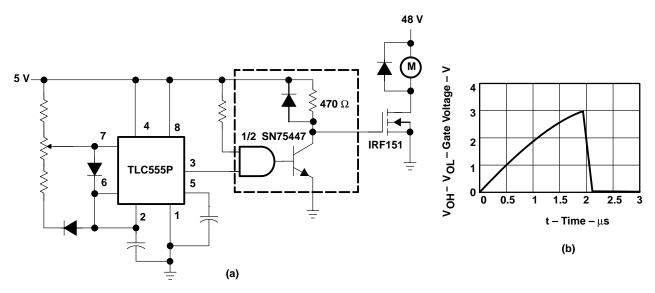

The drive requirements of power MOSFETs are much lower than comparable bipolar power transistors. The input impedance of a FET consists of a reverse biased PN junction that can be described as a large capacitance in parallel with a very high resistance. For this reason, the commonly used open-collector driver with a pullup resistor is not satisfactory for high-speed applications. In Figure 12(a), an IRF151 power MOSFET switching an inductive load is driven by an open-collector transistor driver with a 470- $\Omega$  pullup resistor. The input capacitance ( $C_{iss}$ ) specification for an IRF151 is 4000 pF maximum. The resulting long turn-on time due to the combination of  $C_{iss}$  and the pullup resistor is shown in Figure 12(b).

Figure 12. Power MOSFET Drive Using SN75447

## APPLICATION INFORMATION

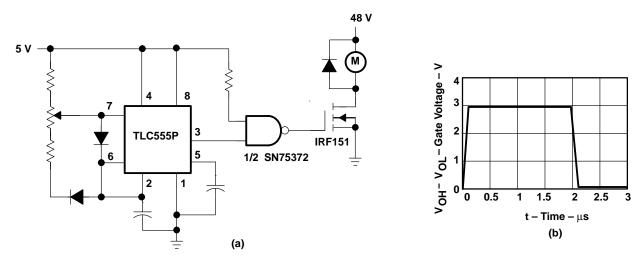

A faster, more efficient drive circuit uses an active pullup as well as an active pulldown output configuration, referred to as a totem-pole output. The SN75372 driver provides the high speed, totem-pole drive desired in an application of this type, see Figure 13(a). The resulting faster switching speeds are shown in Figure 13(b).

Figure 13. Power MOSFET Drive Using SN75372

Power MOSFET drivers must be capable of supplying high peak currents to achieve fast switching speeds as shown by the equation

$$I_{pk} = \frac{VC}{t_r}$$

where C is the capacitive load, and  $t_r$  is the desired drive time. V is the voltage that the capacitance is charged to. In the circuit shown in Figure 13(a), V is found by the equation

$$V = V_{OH} - V_{OL}$$

Peak current required to maintain a rise time of 100 ns in the circuit of Figure 13(a) is

$$I_{PK} = \frac{(3-0)4(10^{-9})}{100(10^{-9})} = 120 \text{ mA}$$

Circuit capacitance can be ignored because it is very small compared to the input capacitance of the IRF151. With a  $V_{CC}$  of 5 V, and assuming worst-cast conditions, the gate drive voltage is 3 V.

For applications in which the full voltage of  $V_{CC2}$  must be supplied to the MOSFET gate, the SN75374 quad MOSFET driver should be used.

## THERMAL INFORMATION

# power dissipation precautions

Significant power may be dissipated in the SN75372 driver when charging and discharging high-capacitance loads over a wide voltage range at high frequencies. Figure 5 shows the power dissipated in a typical SN75372 as a function of load capacitance and frequency. Average power dissipated by this driver is derived from the equation

$$P_{T(AV)} = P_{DC(AV)} + P_{C(AV)} = P_{S(AV)}$$

where  $P_{DC(AV)}$  is the steady-state power dissipation with the output high or low,  $P_{C(AV)}$  is the power level during charging or discharging of the load capacitance, and  $P_{S(AV)}$  is the power dissipation during switching between the low and high levels. None of these include energy transferred to the load, and all are averaged over a full cycle.

The power components per driver channel are

$$P_{DC(AV)} = \frac{P_H t_H + P_L t_L}{T}$$

$$P_{C(AV)} \approx C V_C^2 f$$

$$P_{S(AV)} = \frac{P_L H t_L H + P_{HL} t_{HL}}{T}$$

where the times are as defined in Figure 14.

Figure 14. Output Voltage Waveform

$P_L$ ,  $P_H$ ,  $P_{LH}$ , and  $P_{HL}$  are the respective instantaneous levels of power dissipation, C is the load capacitance.  $V_C$  is the voltage across the load capacitance during the charge cycle shown by the equation

$$V_C = V_{OH} - V_{OL}$$

P<sub>S(AV)</sub> may be ignored for power calculations at low frequencies.

## THERMAL INFORMATION

# power dissipation precautions (continued)

In the following power calculation, both channels are operating under identical conditions:

$V_{OH}$  =19.2 V and  $V_{OL}$  = 0.15 V with  $V_{CC1}$  = 5 V,  $V_{CC2}$  = 20 V,  $V_{C}$  = 19.05 V, C = 1000 pF, and the duty cycle = 60%. At 0.5 MHz,  $P_{S(AV)}$  is negligible and can be ignored. When the output voltage is high,  $I_{CC2}$  is negligible and can be ignored.

On a per-channel basis using data sheet values,

$$\mathsf{P}_{\mathsf{DC}(\mathsf{AV})} = \left[ (5 \ \mathsf{V}) \ \left( \frac{2 \ \mathsf{mA}}{2} \right) \ + \ (20 \ \mathsf{V}) \ \left( \frac{0 \ \mathsf{mA}}{2} \right) \right] \ (0.6) \ + \left[ (5 \ \mathsf{V}) \ \left( \frac{16 \ \mathsf{mA}}{2} \right) \ + \ (20 \ \mathsf{V}) \ \left( \frac{7 \ \mathsf{mA}}{2} \right) \right] \ (0.4)$$

$P_{DC(AV)} = 47 \text{ mW per channel}$

Power during the charging time of the load capacitance is

$$P_{C(AV)} = (1000 \text{ pF}) (19.05 \text{ V})^2 (0.5 \text{ MHz}) = 182 \text{ mW per channel}$$

Total power for each driver is

$$P_{T(AV)} = 47 \text{ mW} + 182 \text{ mW} = 229 \text{ mW}$$

and total package power is

$$P_{T(AV)} = (229) (2) = 458 \text{ mW}.$$

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated