- 8-Bit Resolution

- Linearity . . . ±1/2 LSB Maximum

- Differential Nonlinearity . . . ± 1/2 LSB Maximum

- Conversion Rate . . . 60 MHz Min

- Nominal Output Signal Operating Range V<sub>CC</sub> to V<sub>CC</sub> – 1 V

- TTL Digital Input Voltage

- 5-V Single Power Supply Operation

- Low Power Consumption . . . 350 mW Typ

#### description

The TL5632C is a low-power ultra-high-speed video digital-to-analog converter that uses the Advanced Low-Power Schottky (ALS) process. The device has a three channel I/O; the red, the blue, and the green channel. The red, blue, and green signals are referred to collectively as the RGB signal. An internally generated reference is also provided for the standard video output voltage range. Conversion of digital signals to analog signals can be at a sampling rate of dc to 60 MHz. The high conversion rate makes the TL5632C suitable for digital television, computer digital video processing, and high-speed data conversion.

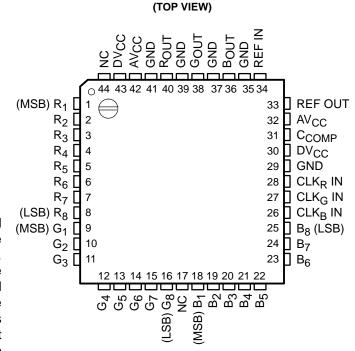

FR PACKAGE

SLAS091 - DECEMBER 1994

NC - No internal connection

The TL5632C is characterized for operation from 0°C to 70°C.

| FUNCTION TABLE |               |                |  |  |  |  |  |

|----------------|---------------|----------------|--|--|--|--|--|

| STEP           | DIGITAL INPUT | OUTPUT VOLTAGE |  |  |  |  |  |

| 0              | LLLLLLL       | 3.980 V        |  |  |  |  |  |

| 1              | LLLLLLH       | 3.984 V        |  |  |  |  |  |

| •              | •             | •              |  |  |  |  |  |

| •              | •             | •              |  |  |  |  |  |

| •              | •             | •              |  |  |  |  |  |

| 127            | LHHHHHHH      | 4.488 V        |  |  |  |  |  |

| 128            | HLLLLLL       | 4.492 V        |  |  |  |  |  |

| 129            | HLLLLLH       | 4.996 V        |  |  |  |  |  |

| •              | •             | •              |  |  |  |  |  |

| •              | •             | •              |  |  |  |  |  |

| •              | •             | •              |  |  |  |  |  |

| 254            | HHHHHHL       | 4.996 V        |  |  |  |  |  |

| 255            | ннннннн       | 5.000 V        |  |  |  |  |  |

#### **AVAILABLE OPTIONS**

| Т <sub>А</sub> | PACKAGE   |  |  |

|----------------|-----------|--|--|

| 0°C to 70°C    | TL5632CFR |  |  |

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLAS091 - DECEMBER 1994

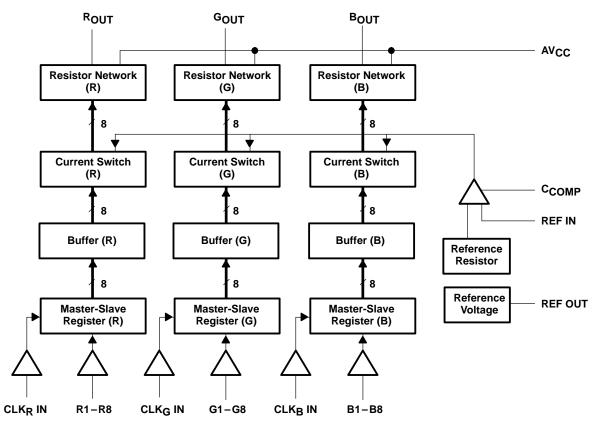

## functional block diagram

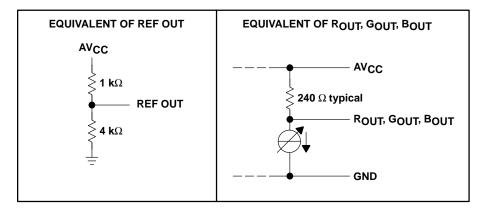

schematics of outputs

SLAS091 - DECEMBER 1994

#### **Terminal Functions**

| TERMINAL I/                     |                       |     | DECODIDITION                                                                                                                                                               |  |  |

|---------------------------------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                 |                       | 1/0 | DESCRIPTION                                                                                                                                                                |  |  |

| B <sub>1</sub> – B <sub>8</sub> | 18 – 25               | I   | B-channel digital input (B <sub>1</sub> = MSB)                                                                                                                             |  |  |

| BOUT                            | 36                    | 0   | B-channel analog output                                                                                                                                                    |  |  |

| CCOMP                           | 31                    |     | Phase compensation capacitance. A 1 $\mu F$ capacitor is connected from C_COMP to GND.                                                                                     |  |  |

| CLK <sub>B</sub> IN             | 26                    | I   | B-channel clock input                                                                                                                                                      |  |  |

| CLK <sub>G</sub> IN             | 27                    | I   | G-channel clock input                                                                                                                                                      |  |  |

| CLK <sub>R</sub> IN             | 28                    | I   | R-channel clock input                                                                                                                                                      |  |  |

| G <sub>1</sub> – G <sub>8</sub> | 9 – 16                | Ι   | G-Channel digital input (G <sub>1</sub> = MSB)                                                                                                                             |  |  |

| GND                             | 29, 35, 37,<br>39, 41 |     | Ground. All GND terminals are connected internally; however, all GND terminals should be connected externally to a ground plane or equivalent low impedance ground return. |  |  |

| GOUT                            | 38                    | 0   | G-channel analog output                                                                                                                                                    |  |  |

| NC                              | 17, 44                |     | No connection internally                                                                                                                                                   |  |  |

| R <sub>1</sub> – R <sub>8</sub> | 1 – 8                 | I   | R-channel digital input (R <sub>1</sub> = MSB)                                                                                                                             |  |  |

| ROUT                            | 40                    | 0   | R-channel analog output                                                                                                                                                    |  |  |

| AVCC                            | 32, 42                |     | Analog power supply voltage                                                                                                                                                |  |  |

| DVCC                            | 30, 43                |     | Digital power supply voltage                                                                                                                                               |  |  |

| REF IN                          | 34                    | I   | Reference voltage input. REF IN accepts the reference voltage on REF OUT. An external reference can also be applied consistent with Note 1.                                |  |  |

| REF OUT                         | 33                    | 0   | Reference voltage output. An internal voltage divider generates the voltage level (see schematics of outputs, page 2).                                                     |  |  |

NOTE 1:  $V_{CC} - V_{ref} \le 1.2 \text{ V}$

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Power supply voltage range, AV <sub>CC</sub> , DV <sub>CC</sub> (see Note 2)                                                 |                                            |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Digital input voltage range,V <sub>1</sub>                                                                                   | -0.3 V to DV <sub>CC</sub>                 |

| Analog output voltage range, R <sub>OUT</sub> , G <sub>OUT</sub> , B <sub>OUT</sub> , C <sub>COMP</sub> (externally applied) | $\dots$ -0.3 V to AV <sub>CC</sub> + 0.3 V |

| Reference input range, REF IN                                                                                                | -0.3  V to AV <sub>CC</sub> + 0.3 V        |

| Reference output range, REF OUT                                                                                              | $\dots$ -0.3 V to AV <sub>CC</sub> + 0.3 V |

| Operating free-air temperature range, T <sub>A</sub>                                                                         | 0°C to 70°C                                |

| Storage temperature range                                                                                                    | −65°C to 150°C                             |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                                                                 |                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SLAS091 - DECEMBER 1994

### recommended operating conditions

|                                                             | MIN  | NOM | MAX  | UNIT |

|-------------------------------------------------------------|------|-----|------|------|

| Supply voltage, AV <sub>CC</sub> , DV <sub>CC</sub>         | 4.75 | 5   | 5.25 | V    |

| High-level input voltage, VIH                               | 2    |     |      | V    |

| Low-level input voltage, VIL                                |      |     | 0.8  | V    |

| Reference voltage, V <sub>ref</sub> (see Note 1)            | 3.8  | 4   | 4.2  | V    |

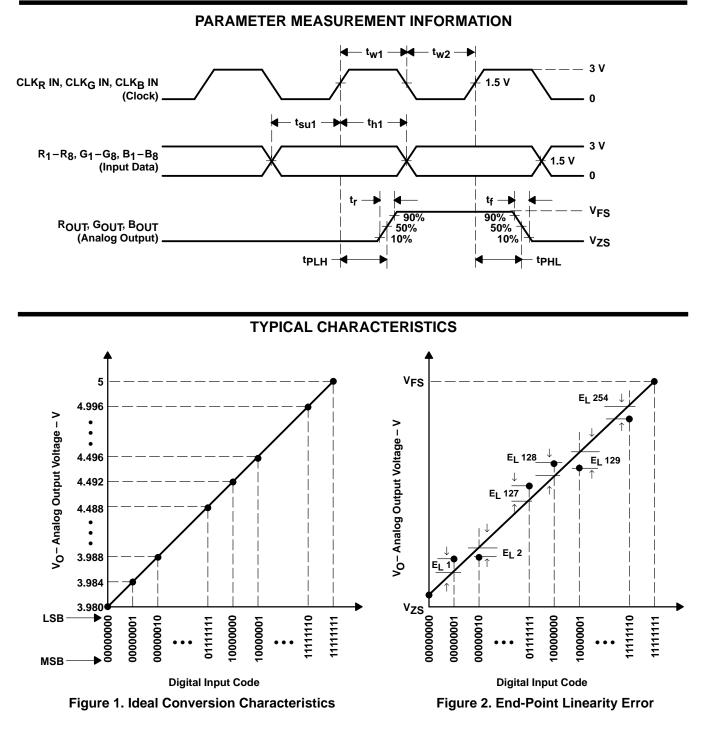

| Setup time, data before CLK <sup>↑</sup> , t <sub>Su1</sub> | 10   |     |      | ns   |

| Hold time, data after CLK↑, t <sub>h1</sub>                 | 3    |     |      | ns   |

| Pulse duration at high level, t <sub>W1</sub>               | 8.3  |     |      | ns   |

| Pulse duration at low level, tw2                            | 8.3  |     |      | ns   |

| External phase compensation capacitance, CCOMP              | 1    |     |      | μF   |

| Operating free-air temperature, T <sub>A</sub>              | 0    |     | 70   | °C   |

NOTE 1:  $V_{CC} - V_{ref} \le 1.2 \text{ V}$

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        |                                  | TEST                      | TEST CONDITIONS         |                      |      | MAX                  | UNIT |

|------------------|----------------------------------|---------------------------|-------------------------|----------------------|------|----------------------|------|

|                  | Resolution                       |                           |                         |                      |      | 8                    | Bit  |

| Iн               | High-level input current         | V <sub>CC</sub> = 5.25 V, | V <sub>IH</sub> = 2.7 V |                      |      | 20                   | μA   |

| ۱ <sub>IL</sub>  | Low-level input current          | V <sub>CC</sub> = 5.25 V, | V <sub>IH</sub> = 2.7 V | -400                 |      |                      | μA   |

| I <sub>ref</sub> | Reference input current          | REF IN = 4 V              |                         |                      |      | 10                   | μA   |

| V <sub>ref</sub> | Reference output voltage         | V <sub>CC</sub> = 5 V,    | With internal reference | 3.8                  | 4    | 4.2                  | V    |

| VFS              | Full-scale analog output voltage | VIH = 2 V,                | REF IN = 4 V            | AV <sub>CC</sub> -15 | AVCC | AV <sub>CC</sub> +15 | mV   |

| VZS              | Zero-scale analog output voltage | V <sub>IL</sub> = 0.8 V,  | REF IN = 4 V            | 3.9                  | 3.98 | 4.05                 | V    |

|                  | RGB full-scale ratio             |                           |                         | 0%                   | 4%   | 8%                   |      |

| z <sub>0</sub>   | Output impedance                 |                           |                         | 200                  | 240  | 280                  | Ω    |

| ICC              | Supply current                   |                           |                         |                      | 70   | 90                   | mA   |

#### operating characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        |                                           | TEST CONDITIONS        |                                    | MIN | TYP† | MAX  | UNIT |  |

|------------------|-------------------------------------------|------------------------|------------------------------------|-----|------|------|------|--|

| EL               | Linearity error                           | End point,             | REF IN = 4 V                       |     |      | ±0.5 | LSB  |  |

| ED               | Differential linearity error              | REF IN = 4 V           |                                    |     |      | ±0.5 | LSB  |  |

| f <sub>C</sub>   | Maximum conversion rate                   |                        |                                    | 60  |      |      | MHz  |  |

| <sup>t</sup> PLH | Propagation delay time, low-to-high level |                        |                                    |     | 10   |      | 50   |  |

| <sup>t</sup> PHL | Propagation delay time, high-to-low level | T <sub>A</sub> = 25°C, | = 25°C, $C_L \leq 5 pF^{\ddagger}$ |     | 10   |      | ns   |  |

| tr               | Rise time                                 |                        |                                    |     | 5    |      |      |  |

| t <sub>f</sub>   | Fall time                                 |                        |                                    |     | 5    |      | ns   |  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. <sup>‡</sup> C<sub>L</sub> includes probe and jig capacitances.

SLAS091 - DECEMBER 1994

SLAS091 – DECEMBER 1994

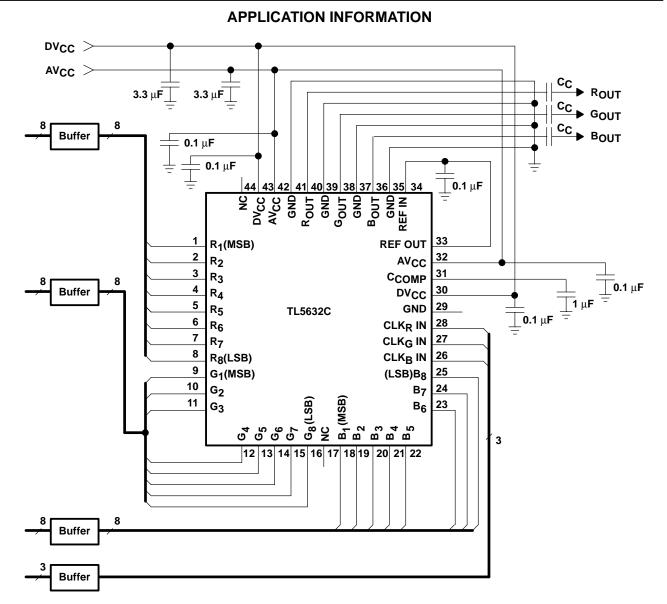

## **APPLICATION INFORMATION**

The following design procedures should be used for optimum operation.

- External analog and digital circuitry should be physically separated and shielded as much as possible to reduce system noise.

- RF breadboarding or RF printed-circuit-board (PCB) techniques should be used throughout the evaluation and production process.

- Wide ground leads or a ground plane should be used on the PCB layouts to minimize parasitic inductance and resistance. A ground plane is the better choice for noise reduction.

- AV<sub>CC</sub> and DV<sub>CC</sub> are also separate internally, so they must be connected externally. These external PCB leads should also be made as wide as possible. A ferrite bead or equivalent inductance should be placed in series with AV<sub>CC</sub> and the decoupling capacitor before the AV<sub>CC</sub> and DV<sub>CC</sub> leads are connected together on the board. It is critical that the supply voltage applied to AV<sub>CC</sub> be as noise free and ripple free as possible. Ripple and noise rejection should be a minimum of 60 dB below the full-scale output range of 1 V peak-to-peak.

- AV<sub>CC</sub> to GND and DV<sub>CC</sub> to GND should be decoupled with 3.3-μF and 0.1-μF capacitors, respectively, as close as possible to the appropriate device terminals. A ceramic chip capacitor is recommended for the 0.1-μF capacitor.

- The phase compensation capacitor should be connected between C<sub>COMP</sub> and GND with as short a lead-in as possible.

- The no-connection (NC) terminals on the small-outline package should be connected to GND.

- AV<sub>CC</sub>, DV<sub>CC</sub>, and R<sub>OUT</sub>, G<sub>OUT</sub>, and B<sub>OUT</sub> should be shielded from the high-frequency terminals CLK<sub>R</sub> IN, CLK<sub>G</sub> IN, and CLK<sub>B</sub> IN and the input data terminals. GND traces should be placed on both sides of the R<sub>OUT</sub>, G<sub>OUT</sub>, and B<sub>OUT</sub> traces on the PCB to the following signal processing stage. These output traces should be as short as possible.

SLAS091 - DECEMBER 1994

NOTES: A. Buffers are SN74AS244 or equivalent.

B. 0.1  $\mu$ F capacitors should be placed as close to the device terminals as possible.

C. The coupling capacitor (C<sub>C</sub>) value is application specific and selectable by the user.

Figure 3. Typical Bypass, Buffer, and Output Configuration

SLAS091 – DECEMBER 1994

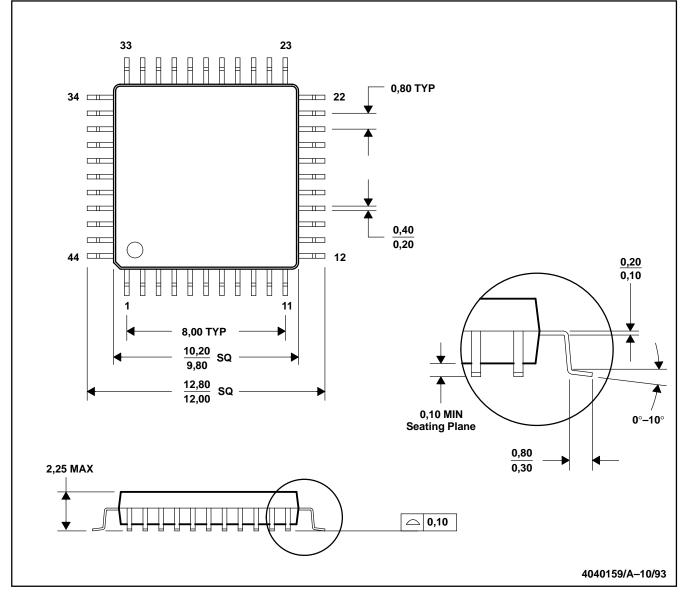

MECHANICAL DATA

FR/S-PQFP-G44

PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated