SLLS533A - MAY 2002 - REVISED AUGUST 2002

# **HIGH OUTPUT RS-485 TRANSCEIVERS**

# FEATURES

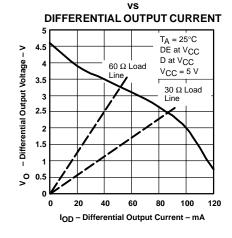

- Minimum Differential Output Voltage of 2.5 V Into a 54-Ω Load

- Open-Circuit and Idle-Bus Failsafe Receiver

- 1/8<sup>th</sup> Unit-Load Option Available (Up to 256 Nodes on the Bus)

- Bus-Pin ESD Protection Exceeds 16 kV HBM

- Driver Output Slew Rate Control Options

- Electrically Compatible With ANSI TIA/EIA-485-A Standard

- Low-Current Standby Mode . . . 1 μA Typical

- Glitch-Free Power-Up and Power-Down Protection for Hot-Plugging Applications

- Pin Compatible With Industry Standard SN75176

# APPLICATIONS

- Data Transmission Over Long or Lossy Lines or Electrically Noisy Environments

- Profibus Line Interface

- Industrial Process Control Networks

- Point-of-Sale (POS) Networks

- Electric Utility Metering

- Building Automation

- Digital Motor Control

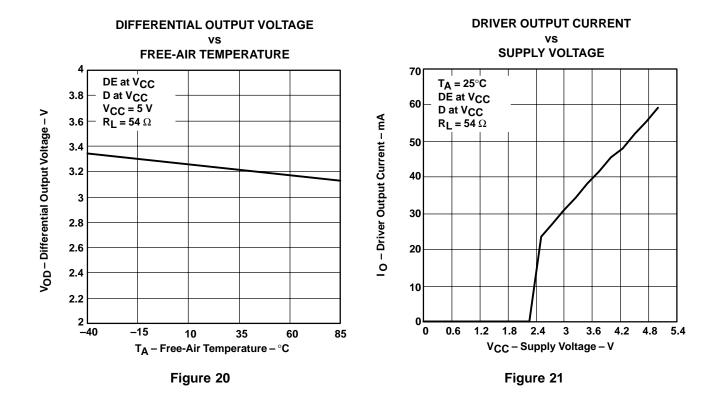

DIFFERENTIAL OUTPUT VOLTAGE

# DESCRIPTION

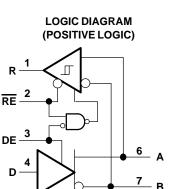

The SN65HVD05, SN75HVD05, SN65HVD06, SN75HVD06, SN65HVD07, and SN75HVD07 combine a 3-state differential line driver and differential line receiver. They are designed for balanced data interoperate ANSI transmission and with TIA/EIA-485-A and ISO 8482E standard-compliant devices. The driver is designed to provide a differential output voltage greater than that required by these standards for increased noise margin. The drivers and receivers have active-high and active-low enables respectively, which can be externally connected together to function as direction control.

The driver differential outputs and receiver differential inputs connect internally to form a differential input/ output (I/O) bus port that is designed to offer minimum loading to the bus whenever the driver is disabled or not powered. These devices feature wide positive and negative common-mode voltage ranges, making them suitable for party-line applications.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ÆÀ

SLLS533A - MAY 2002 - REVISED AUGUST 2002

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ORDERING INFORMATION(1)**

|                   |              |                                   |                |                            |            |                                              | (ED AS                                |

|-------------------|--------------|-----------------------------------|----------------|----------------------------|------------|----------------------------------------------|---------------------------------------|

| SIGNALING<br>RATE | UNIT<br>LOAD | DRIVER<br>OUTPUT SLOPE<br>CONTROL | Т <sub>А</sub> | PART NUMBER <sup>(2)</sup> |            | PLASTIC<br>DUAL-IN-LINE<br>PACKAGE<br>(PDIP) | SMALL OUTLINE<br>IC (SOIC)<br>PACKAGE |

| 40 Mbps           | 1/2          | No                                |                | SN65HVD05D                 | SN65HVD05P | 65HVD05                                      | VP05                                  |

| 10 Mbps           | 1/8          | Yes                               | –40°C to 85°C  | SN65HVD06D                 | SN65HVD06P | 65HVD06                                      | VP06                                  |

| 1 Mbps            | 1/8          | Yes                               |                | SN65HVD07D                 | SN65HVD07P | 65HVD07                                      | VP07                                  |

| 40 Mbps           | 1/2          | No                                |                | SN75HVD05D                 | SN75HVD05P | 75HVD05                                      | VN05                                  |

| 10 Mbps           | 1/8          | Yes                               | –0°C to 70°C   | SN75HVD06D                 | SN75HVD06P | 75HVD06                                      | VN06                                  |

| 1 Mbps            | 1/8          | Yes                               |                | SN75HVD07D                 | SN75HVD07P | 75HVD07                                      | VN07                                  |

(1) For the most current specification and package information, refer to our web site at www.ti.com.

<sup>(2)</sup> The D package is available taped and reeled. Add an R suffix to the device type (i.e., SN65HVD05DR).

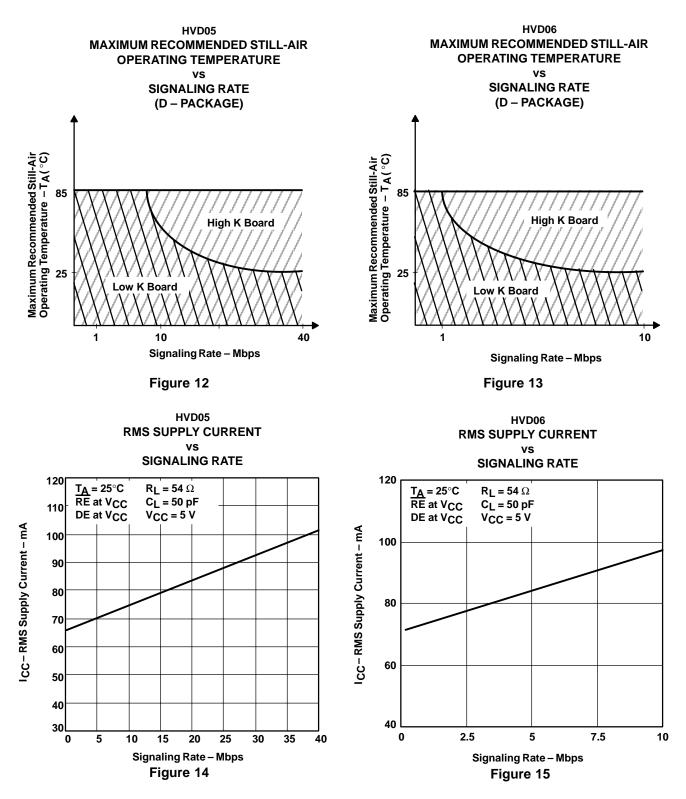

#### PACKAGE DISSIPATION RATINGS (SEE FIGURES 12 & 13)

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C POWER<br>RATING |

|---------|---------------------------------------|---------------------------------------------------------------|---------------------------------------|---------------------------------------|

| D(2)    | 710 mW                                | 5.7 mW/°C                                                     | 455 mW                                | 369 mW                                |

| D(3)    | 1282 mW                               | 10.3 mW/°C                                                    | 821 mW                                | 667 mW                                |

| Р       | 1000 mW                               | 8.0 mW/°C                                                     | 640 mW                                | 520 mW                                |

| (4)     |                                       |                                                               |                                       |                                       |

(1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

(2) Tested in accordance with the Low-K thermal metric definitions of EIA/JESD51-3

(3) Tested in accordance with the High-K thermal metric definitions of EIA/JESD51-7

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted (1) (2)

|                                                                                     |                                  |                                   | SN65HVD05, SN65HVD06, SN65HVD07<br>SN75HVD05, SN75HVD06, SN75HVD07 |

|-------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|--------------------------------------------------------------------|

| Supply voltage range, VC                                                            | С                                |                                   | -0.3 V to 6 V                                                      |

| Voltage range at A or B                                                             | –9 V to 14 V                     |                                   |                                                                    |

| Input voltage range at D,                                                           | DE, R or RE                      | -0.5 V to V <sub>CC</sub> + 0.5 V |                                                                    |

| Voltage input range, transient pulse, A and B, through 100 $\Omega$ (see Figure 11) |                                  |                                   | –50 V to 50 V                                                      |

|                                                                                     | Human body model(3)              | A, B, and GND                     | 16 kV                                                              |

| Electrostatic discharge                                                             |                                  | All pins                          | 4 kV                                                               |

|                                                                                     | Charged-devicemodel(4)           | All pins                          | 1 kV                                                               |

| Continuous total power dissipation                                                  |                                  |                                   | See Dissipation Rating Table                                       |

| Storage temperature range, T <sub>stg</sub>                                         |                                  |                                   | -65°C to 150°C                                                     |

| Lead temperature 1,6 mm                                                             | n (1/16 inch) from case for 10 s | seconds                           | 260°C                                                              |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-A.

(4) Tested in accordance with JEDEC Standard 22, Test Method C101.

# **RECOMMENDED OPERATING CONDITIONS**

|                                                |                      | M   | N NOM | MAX | UNIT |

|------------------------------------------------|----------------------|-----|-------|-----|------|

| Supply voltage, V <sub>CC</sub>                |                      | 4   | 5     | 5.5 | V    |

| Voltage at any bus terminal (separately or con | mmon mode) VI or VIC | _7( | 1)    | 12  | V    |

| High-level input voltage, VIH                  | D, DE, RE            |     | 2     |     | V    |

| Low-level input voltage, VIL                   | D, DE, RE            |     |       | 0.8 | V    |

| Differential input voltage, VID (see Figure 7) |                      | -^  | 2     | 12  | V    |

| High-level output current, IOH                 | Driver               | -10 | 0     |     |      |

|                                                | Receiver             | -   | -8    |     | mA   |

|                                                | Driver               |     |       | 100 | mA   |

| Low-level output current, IOL                  | Receiver             |     |       | 8   |      |

|                                                | SN65HVD05            |     |       |     |      |

|                                                | SN65HVD06            | _4  | 0     | 85  | °C   |

|                                                | SN65HVD07            |     |       |     |      |

| Operating free-air temperature, T <sub>A</sub> | SN75HVD05            |     |       |     |      |

|                                                | SN75HVD06            |     | 0     | 70  | °C   |

|                                                | SN75HVD07            |     |       |     |      |

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

# **DRIVER ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range unless otherwise noted  $^{(1)}$

| PARAMETER           |                                                 | TEST CONDITIONS |                                                                                        | MIN                                                   | TYP(1)       | MAX | UNIT |    |     |   |

|---------------------|-------------------------------------------------|-----------------|----------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|-----|------|----|-----|---|

| VIK                 | Input clamp voltage                             |                 | II = -18 mA                                                                            |                                                       | -1.5         |     |      | V  |     |   |

|                     |                                                 |                 | No Load                                                                                |                                                       |              |     | VCC  |    |     |   |

| <b>IVOD</b>         | Differential output voltage                     |                 | $R_L = 54 \Omega$ , See Figure 1                                                       |                                                       | 2.5          |     |      | V  |     |   |

| -                   |                                                 |                 | $V_{test} = -7 V \text{ to } 12 V$ , See                                               | Figure 2                                              | 2.2          |     |      |    |     |   |

|                     | Change in magnitude of dif output voltage       | ferential       | See Figure 1 and Figure 2                                                              |                                                       | -0.2         |     | 0.2  | V  |     |   |

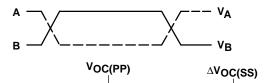

| V <sub>OC(SS)</sub> | Steady-state common-moo<br>voltage              | leoutput        |                                                                                        |                                                       |              |     | 2.2  |    | 3.3 | V |

| $\Delta V_{OC(SS)}$ | Change in steady-state common-mode output volta | ige             | See Figure 3                                                                           |                                                       | See Figure 3 |     | -0.1 |    | 0.1 | V |

|                     | HVD05                                           |                 |                                                                                        |                                                       |              | 600 |      |    |     |   |

| VOC(PP)             | Peak-to-peak common-<br>mode output voltage     | HVD06           | See Figure 3                                                                           |                                                       |              | 500 |      | mV |     |   |

|                     | mode output voltage                             | HVD07           |                                                                                        |                                                       |              | 900 |      |    |     |   |

| IOZ                 | High-impedance output cur                       | rent            | See receiver input currents                                                            |                                                       |              |     |      |    |     |   |

| 1.                  | logut ourroat                                   | D               |                                                                                        |                                                       | -100         |     | 0    |    |     |   |

| I                   | Input current                                   | DE              |                                                                                        |                                                       | 0            |     | 100  | μA |     |   |

| los                 | Short-circuit output current                    |                 | $-7 \text{ V} \le \text{V}_0 \le 12 \text{ V}$                                         |                                                       | -250         |     | 250  | mA |     |   |

| C <sub>(diff)</sub> | Differential output capacita                    | nce             | V <sub>ID</sub> = 0.4 sin (4E6πt) + 0.5 V, DE at 0 V                                   |                                                       |              | 16  |      | pF |     |   |

|                     |                                                 |                 | RE at V <sub>CC</sub> ,<br>D & DE at V <sub>CC</sub> , No load                         | Receiver disabled and driver enabled                  |              | 9   | 15   | mA |     |   |

| ICC Supply current  |                                                 |                 | $\overline{\text{RE}}$ at V <sub>CC</sub> , D at V <sub>CC</sub><br>DE at 0 V, No load | Receiver disabled and<br>driver disabled<br>(standby) |              | 1   | 5    | μΑ |     |   |

|                     |                                                 |                 |                                                                                        | Receiver enabled and driver enabled                   |              | 9   | 15   | mA |     |   |

(1) All typical values are at 25°C and with a 5-V supply.

SLLS533A - MAY 2002 - REVISED AUGUST 2002

TEXAS STRUMENTS www.ti.com

over operating free-air temperature range unless otherwise noted

|                         | PARAMETER                                                   |          | TEST<br>CONDITIONS                                             | MIN | ТҮР(1) | МАХ | UNIT |  |

|-------------------------|-------------------------------------------------------------|----------|----------------------------------------------------------------|-----|--------|-----|------|--|

|                         |                                                             | HVD05    |                                                                |     | 6.5    | 11  |      |  |

| <sup>t</sup> PLH        | Propagation delay time, low-to-high-level output            | HVD06    |                                                                |     | 27     | 40  | ns   |  |

|                         |                                                             | HVD07    |                                                                |     | 250    | 400 |      |  |

|                         |                                                             | HVD05    | -                                                              |     | 6.5    | 11  |      |  |

| <sup>t</sup> PHL        | Propagation delay time, high-to-low-level output            | HVD06    | -                                                              |     | 27     | 40  | ns   |  |

|                         |                                                             | HVD07    | -                                                              |     | 250    | 400 |      |  |

|                         |                                                             | HVD05    | R <sub>L</sub> = 54 Ω,                                         | 2.7 | 3.6    | 6   |      |  |

| tr                      | Differential output signal rise time                        | HVD06    | $C_{L} = 50 \text{ pF},$                                       | 18  | 28     | 55  | ns   |  |

| -                       |                                                             | HVD07    | See Figure 4                                                   | 150 | 300    | 450 |      |  |

|                         |                                                             | HVD05    |                                                                | 2.7 | 3.6    | 6   |      |  |

| tf                      | Differential output signal fall time                        | HVD06    |                                                                | 18  | 28     | 55  | ns   |  |

| •                       |                                                             | HVD07    | -                                                              | 150 | 300    | 450 |      |  |

|                         |                                                             | HVD05    | -                                                              |     |        | 2   |      |  |

| <sup>t</sup> sk(p)      | Pulse skew ( t <sub>PHL</sub> – t <sub>PLH</sub>  )         | HVD06    |                                                                |     |        | 2.5 | ns   |  |

| - <b>s</b> k(p)         |                                                             | HVD07    |                                                                |     |        | 10  |      |  |

|                         |                                                             | HVD05    |                                                                |     |        | 3.5 |      |  |

| t <sub>sk(pp)</sub> (2) | Part-to-part skew                                           | HVD06    |                                                                |     |        | 14  | ns   |  |

| <b>.sk</b> (pp)(=)      |                                                             | HVD07    |                                                                |     |        | 100 |      |  |

|                         |                                                             | HVD05    |                                                                |     |        | 25  | ns   |  |

| <sup>t</sup> PZH1       | Propagation delay time, high-impedance-to-high-level output | HVD06    | -                                                              |     |        | 45  |      |  |

| FZUI                    |                                                             | HVD07    | RE at 0 V,                                                     |     |        | 250 |      |  |

|                         |                                                             | HVD05    | $R_L = 110 \Omega$ ,<br>See Figure 5                           |     |        | 25  |      |  |

| <sup>t</sup> PHZ        | Propagation delay time, high-level-to-high-impedance output | HVD06    | See Figure 5                                                   |     |        | 60  | ns   |  |

| *F11Z                   |                                                             | HVD07    |                                                                |     |        | 250 |      |  |

|                         |                                                             | HVD05    |                                                                |     |        | 15  |      |  |

| <sup>t</sup> PZL1       | Propagation delay time, high-impedance-to-low-level output  | HVD06    | -                                                              |     |        | 45  | ns   |  |

| FZLI                    |                                                             | HVD07    | RE at 0 V,                                                     |     |        | 200 | 115  |  |

|                         |                                                             | HVD05    | $R_L = 110 \Omega$ ,                                           |     |        | 14  |      |  |

| <sup>t</sup> PLZ        | Propagation delay time, low-level-to-high-impedance output  | HVD06    | See Figure 6                                                   |     |        | 90  | ns   |  |

| PLZ                     | r ropugatorradiay and, low lover to high impedance output   | HVD07    | -                                                              |     |        | 550 | 115  |  |

| <sup>t</sup> PZH2       | Propagation delay time, standby-to-high-level output        | <u> </u> | $R_{I}$ = 110 Ω,<br>RE at 3 V,<br>See Figure 5                 |     |        | 6   | μs   |  |

| <sup>t</sup> PZL2       | Propagation delay time, standby-to-low-level output         |          | $\frac{R_{L}}{RE} = 110 \Omega,$<br>RE at 3 V,<br>See Figure 6 |     |        | 6   | μs   |  |

(1) All typical values are at 25°C and with a 5-V supply.

(2) t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

SLLS533A - MAY 2002 - REVISED AUGUST 2002

# **RECEIVER ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range unless otherwise noted

|                                | PARAMETER                       |                                                                            |                                                      | <b>TEST CONDITIONS</b>                |                       | MIN   | ТҮР(1) | MAX   | UNIT |

|--------------------------------|---------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------|-----------------------|-------|--------|-------|------|

| V <sub>IT+</sub>               | Positive-going input th voltage | reshold                                                                    | I <sub>O</sub> = -8 mA                               |                                       |                       |       |        | -0.01 | V    |

| V <sub>IT</sub> –              | Negative-going input t voltage  | hreshold                                                                   | IO = 8 mA                                            |                                       |                       | -0.2  |        |       | V    |

| V <sub>hys</sub>               | Hysteresis voltage (V           | IT+-VIT_)                                                                  |                                                      |                                       |                       |       | 35     |       | mV   |

| VIK                            | Enable-input clamp vo           | oltage                                                                     | l <sub>l</sub> = –18 mA                              |                                       |                       | -1.5  |        |       | V    |

| VOH                            | High-level output volta         | age                                                                        | V <sub>ID</sub> = 200 mV,                            | I <sub>OH</sub> = -8 mA,              | See Figure 7          | 4     |        |       | V    |

| VOL                            | Low-level output volta          | ge                                                                         | $V_{ID} = -200 \text{ mV},$                          | I <sub>OL</sub> = 8 mA,               | See Figure 7          |       |        | 0.4   | V    |

| IOZ                            | High-impedance-state current    | e output                                                                   | $V_{O} = 0 \text{ or } V_{CC}$                       | RE at V <sub>CC</sub>                 |                       | -1    |        | 1     | μA   |

|                                |                                 |                                                                            |                                                      | $V_A \text{ or } V_B = 12 \text{ V}$  |                       |       | 0.23   | 0.5   |      |

|                                | HVD                             |                                                                            | Otherinput                                           | $V_A \text{ or } V_B = 12 \text{ V},$ | V <sub>CC</sub> = 0 V |       | 0.3    | 0.5   |      |

|                                |                                 | at 0 V $V_A \text{ or } V_B = -7 \text{ V}$                                |                                                      | -0.4                                  | -0.13                 |       | mA     |       |      |

|                                | <b>5</b> · · · ·                |                                                                            |                                                      | $V_A$ or $V_B = -7 V$ ,               | VCC = 0 V             | -0.4  | -0.15  |       |      |

| I                              | Bus input current               | $V_A \text{ or } V_B = 12 \text{ V}$                                       |                                                      | $V_A \text{ or } V_B = 12 \text{ V}$  |                       |       | 0.06   | 0.1   |      |

|                                |                                 |                                                                            | VCC = 0 V                                            |                                       | 0.8                   | 0.13  |        |       |      |

|                                |                                 | HVD07                                                                      | at 0 V                                               | $V_A \text{ or } V_B = -7 \text{ V}$  |                       | -0.1  | -0.05  |       | mA   |

|                                |                                 |                                                                            |                                                      | $V_A \text{ or } V_B = -7 \text{ V},$ | ACC = 0 A             | -0.05 | -0.03  |       |      |

| Iн                             | High-level input curre          | nt, RE                                                                     | V <sub>IH</sub> = 2 V                                |                                       |                       | -60   | -26.4  |       | μA   |

| ١ <sub>IL</sub>                | Low-level input currer          | nt, RE                                                                     | VIL = 0.8 V                                          |                                       |                       | -60   | -27.4  |       | μA   |

| C <sub>(diff)</sub>            | Differential input capa         | citance                                                                    | V <sub>I</sub> = 0.4 sin (4E6)                       | πt) + 0.5 V, DE at 0                  | V                     |       | 16     |       | pF   |

|                                | ···/                            |                                                                            | RE at 0 V,<br>D & DE at 0 V,<br>No load              | Receiver enabled a                    | nd driver disabled    |       | 5      | 10    | mA   |

| I <sub>CC</sub> Supply current |                                 | RE at V <sub>CC</sub> ,<br>DE at 0 V,<br>D at V <sub>CC</sub> ,<br>No load | Receiver disabled a (standby)                        | nd driver disabled                    |                       | 1     | 5      | μA    |      |

|                                |                                 |                                                                            | RE at 0 V,<br>D & DE at V <sub>CC</sub> ,<br>No load | Receiver enabled a                    | nd driver enabled     |       | 9      | 15    | mA   |

(1) All typical values are at 25°C and with a 5-V supply.

# **RECEIVER SWITCHING CHARACTERISTICS**

over operating free-air temperature range unless otherwise noted

|                        | PARAMETER                                                              |       | <b>TEST CONDITIONS</b>           | MIN | ТҮР(1) | MAX | UNIT |

|------------------------|------------------------------------------------------------------------|-------|----------------------------------|-----|--------|-----|------|

| <sup>t</sup> PLH       | Propagation delay time, low-to-high-level output 1/2 UL                | HVD05 |                                  |     | 14.6   | 25  | ns   |

| <sup>t</sup> PHL       | Propagation delay time, high-to-low-level output 1/2 UL                | HVD05 |                                  |     | 14.6   | 25  | ns   |

| 4                      | Dran a mation data stime to thigh layed as that 4 (01.11               | HVD06 |                                  |     | 55     | 70  |      |

| <sup>t</sup> PLH       | Propagation delay time, low-to-high-level output 1/8 UL                | HVD07 | VID = -1.5 V to 1.5 V,           |     | 55     | 70  | ns   |

| 4                      | Dran a mation data stimu high to law lawel as truth (01)               | HVD06 | $C_{L} = 15  \text{pF},$         |     | 55     | 70  |      |

| <sup>t</sup> PHL       | Propagation delay time, high-to-low-level output 1/8 UL                | HVD07 | See Figure 8                     |     | 55     | 70  | ns   |

|                        | HVD05       Pulse skew ( tpHL - tpLH )     HVD06       HVD07     HVD07 |       |                                  |     | 2      |     |      |

| <sup>t</sup> sk(p) P   |                                                                        | HVD06 |                                  |     |        | 4.5 | ns   |

|                        |                                                                        | HVD07 |                                  |     |        | 4.5 |      |

|                        | Part-to-part skew                                                      | HVD05 |                                  |     |        | 6.5 | ns   |

| tsk(pp) <sup>(2)</sup> |                                                                        | HVD06 |                                  |     |        | 14  |      |

| ,                      |                                                                        | HVD07 |                                  |     |        | 14  |      |

| t <sub>r</sub>         | Output signal rise time                                                |       | CL = 15 pF,                      |     | 2      | 3   |      |

| t <sub>f</sub>         | Output signal fall time                                                |       | See Figure 8                     |     | 2      | 3   | ns   |

| <sup>t</sup> PZH1      | Output enable time to high level                                       |       |                                  |     |        | 10  |      |

| <sup>t</sup> PZL1      | Output enable time to low level                                        |       | $C_L = 15 \text{ pF},$           |     |        | 10  |      |

| <sup>t</sup> PHZ       | Z Output disable time from high level                                  |       | DE at 3 V,<br>See Figure 9       |     |        | 15  | ns   |

| <sup>t</sup> PLZ       | Output disable time from low level                                     |       |                                  |     |        | 15  |      |

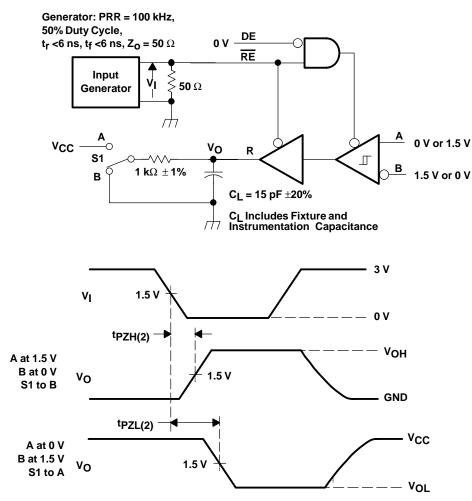

| <sup>t</sup> PZH2      | Propagation delay time, standby-to-high-level output                   |       | C <sub>L</sub> = 15 pF, DE at 0, |     |        | 6   |      |

| <sup>t</sup> PZL2      | Propagation delay time, standby-to-low-level output                    |       | See Figure 10                    |     |        | 6   | μs   |

(1) All typical values are at 25°C and with a 5-V supply.

(2) t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

SLLS533A - MAY 2002 - REVISED AUGUST 2002

# PARAMETER MEASUREMENT INFORMATION

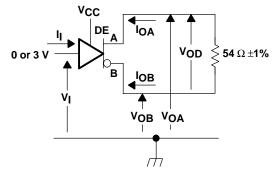

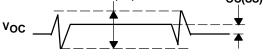

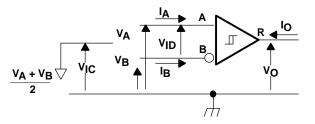

# Figure 1. Driver V<sub>OD</sub> Test Circuit and Voltage and Current Definitions

Input: PRR = 500 kHz, 50% Duty Cycle, $t_{f}$ <6ns,  $t_{f}$ <6ns,  $Z_{O}$  = 50  $\Omega$

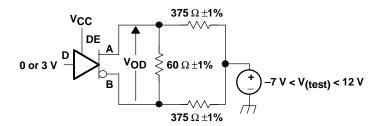

Figure 2. Driver V<sub>OD</sub> With Common-Mode

Loading Test Circuit

#### Figure 3. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

Generator: PRR = 500 kHz, 50% Duty Cycle, t<sub>f</sub> <6 ns, t<sub>f</sub> <6 ns, Z<sub>0</sub> = 50  $\Omega$

### PARAMETER MEASUREMENT INFORMATION

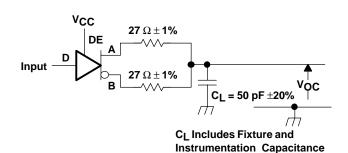

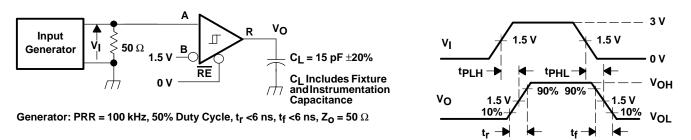

Generator: PRR = 100 kHz, 50% Duty Cycle, t<sub>r</sub> <6 ns, t<sub>f</sub> <6 ns, Z<sub>o</sub> = 50  $\Omega$

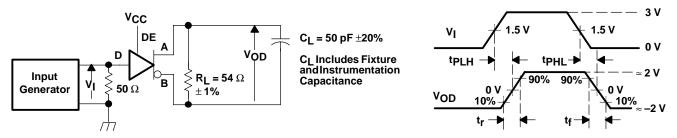

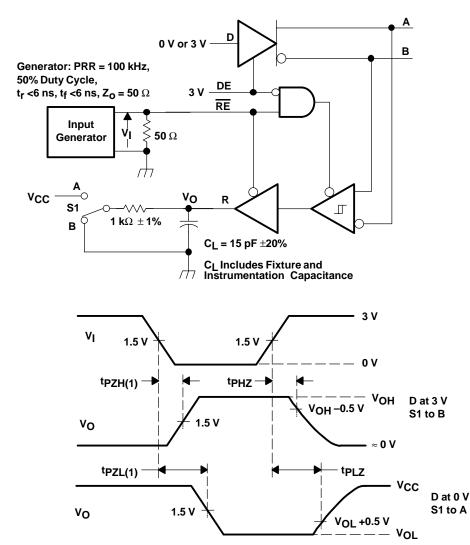

Figure 5. Driver High-Level Enable and Disable Time Test Circuit and Voltage Waveforms

Generator: PRR = 100 kHz, 50% Duty Cycle, tr <6 ns, tf <6 ns, Z\_0 = 50  $\Omega$

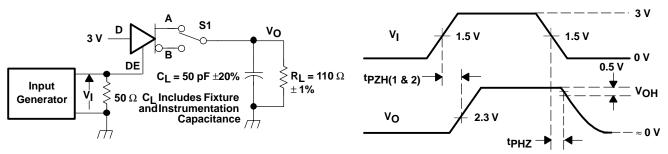

#### Figure 6. Driver Low-Level Output Enable and Disable Time Test Circuit and Voltage Waveforms

Figure 7. Receiver Voltage and Current Definitions

# PARAMETER MEASUREMENT INFORMATION

Figure 8. Receiver Switching Test Circuit and Voltage Waveforms

Figure 9. Receiver Enable and Disable Time Test Circuit and Voltage Waveforms With Drivers Enabled

#### PARAMETER MEASUREMENT INFORMATION

Figure 10. Receiver Enable Time From Standby (Driver Disabled)

NOTE: This test is conducted to test survivability only. Data stability at the R output is not specified.

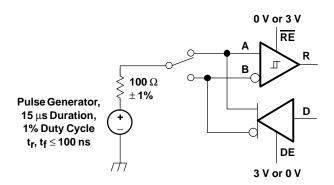

Figure 11. Test Circuit, Transient Over Voltage Test

#### **Function Tables**

| DRIVER |                |   |   |  |  |  |  |

|--------|----------------|---|---|--|--|--|--|

| INPUT  | ENABLE OUTPUTS |   |   |  |  |  |  |

| D      | DE             | Α | В |  |  |  |  |

| Н      | Н              | Н | L |  |  |  |  |

| L      | Н              | L | Н |  |  |  |  |

| Х      | L              | Z | Z |  |  |  |  |

| Open   | Н              | Н | L |  |  |  |  |

| Х      | Open           | Z | Z |  |  |  |  |

| RECEIVER |

|----------|

|          |

| DIFFERENTIAL INPUTS                                       | ENABLE | OUTPUT |

|-----------------------------------------------------------|--------|--------|

| $V_{ID} = V_A - V_B$                                      | RE     | R      |

| V <sub>ID</sub> ≤ -0.2 V                                  | L      | L      |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < -0.01 \text{ V}$ | L      | ?      |

| –0.01 V ≤ V <sub>ID</sub>                                 | L      | Н      |

| Х                                                         | Н      | Z      |

| Open Circuit                                              | L      | Н      |

| Short Circuit                                             | L      | Н      |

| Х                                                         | Open   | Z      |

H = high |eve|; L = low |eve|; Z = high impedance; X = irrelevant; ? = indeterminate

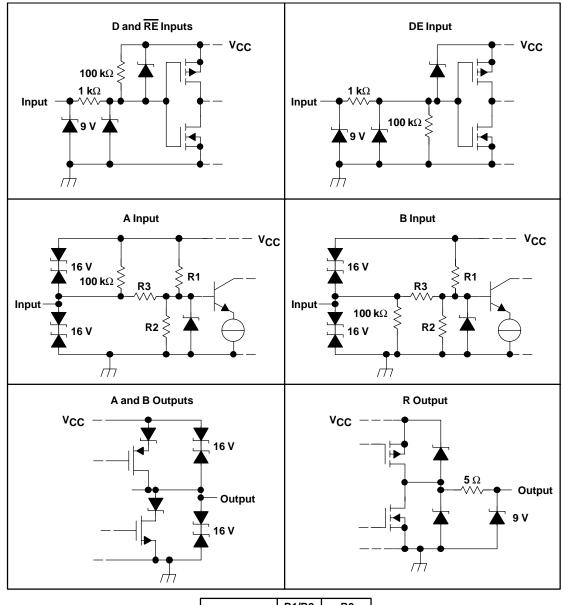

#### EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

|           | R1/R2         | R3             |

|-----------|---------------|----------------|

| SN65HVD05 | <b>9 k</b> Ω  | <b>45 k</b> Ω  |

| SN65HVD06 | <b>36 k</b> Ω | <b>180 k</b> Ω |

| SN65HVD07 | <b>36 k</b> Ω | <b>180 k</b> Ω |

SLLS533A - MAY 2002 - REVISED AUGUST 2002

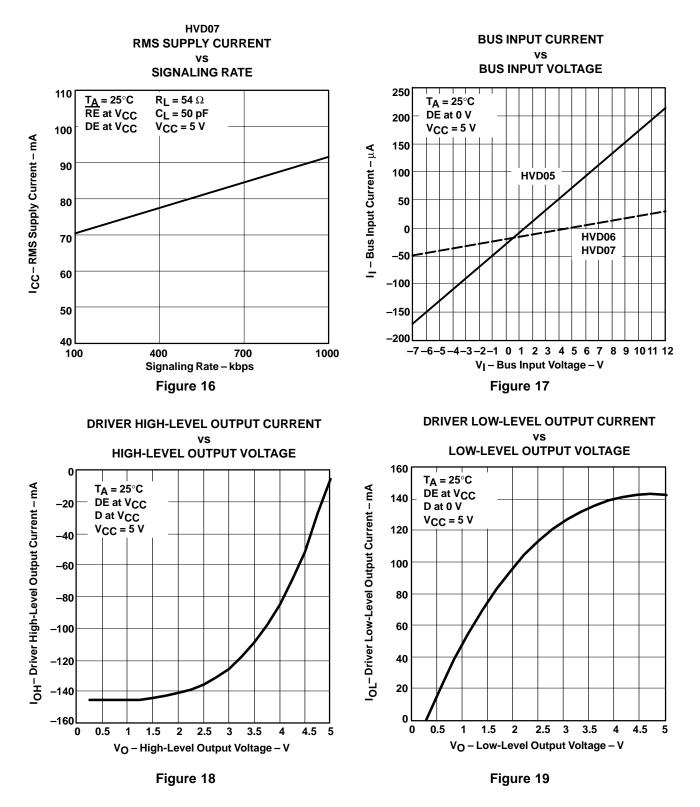

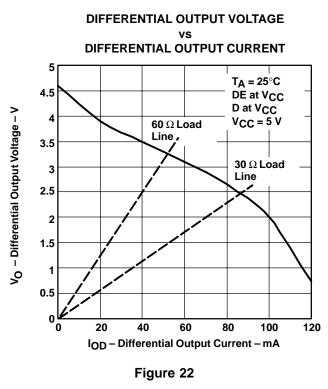

#### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

TEXAS INSTRUMENTS www.ti.com

SLLS533A - MAY 2002 - REVISED AUGUST 2002

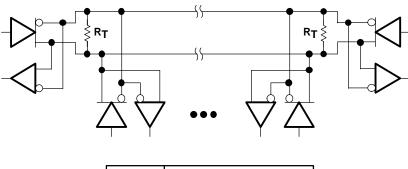

#### **APPLICATION INFORMATION**

| Device | Number of Devices on Bus |

|--------|--------------------------|

| HVD05  | 64                       |

| HVD06  | 256                      |

| HVD07  | 256                      |

NOTE: The line should be terminated at both ends with its characteristic impedance ( $R_T = Z_O$ ). Stub lengths off the main line should be kept as short as possible.

Figure 23. Typical Application Circuit

#### TEXAS INSTRUMENTS www.ti.com

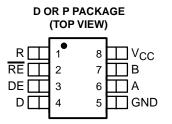

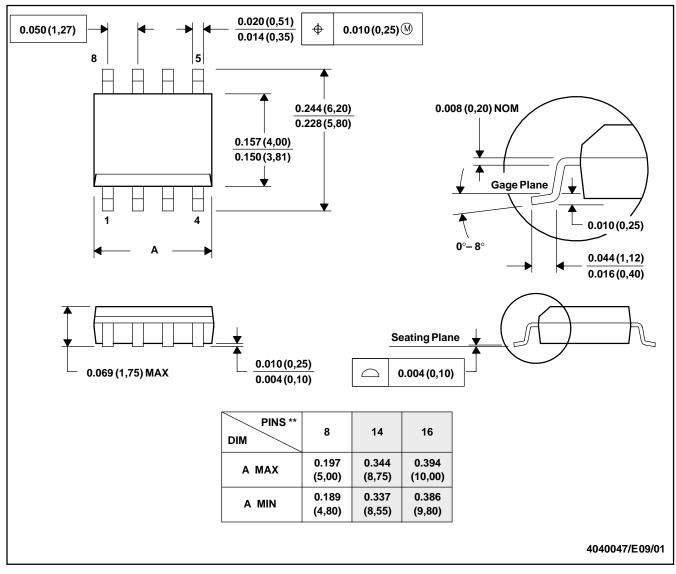

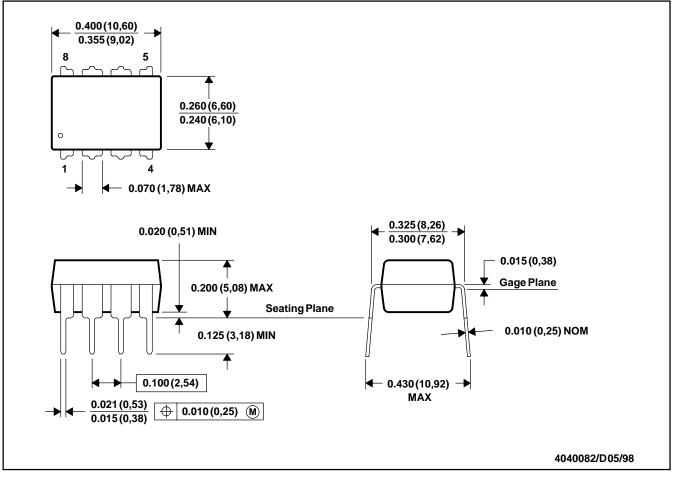

D (R-PDSO-G\*\*)

**8 PINS SHOWN**

# SN65HVD05, SN65HVD06, SN65HVD07 SN75HVD05, SN75HVD06, SN75HVD07

SLLS533A - MAY 2002 - REVISED AUGUST 2002

### MECHANICAL DATA

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012

#### **MECHANICAL DATA**

#### P (R-PDIP-T8)

PLASTIC DUAL-IN-LINE

NOTES:A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated