'LVDS389

SLLS362D – SEPTEMBER 1999 – REVISED MAY 2001

**'LVDS387**

- Designed for Signaling Rates<sup>†</sup> up to 630 Mbps With Very Low Radiation (EMI)

- Low-Voltage Differential Signaling With Typical Output Voltage of 350 mV and a 100- $\Omega$  Load

- **Propagation Delay Times Less Than 2.9 ns**

- **Output Skew Is Less Than 150 ps**

- Part-to-Part Skew Is Less Than 1.5 ns

- 35-mW Total Power Dissipation in Each **Driver Operating at 200 MHz**

- **Driver Is High Impedance When Disabled or** With  $V_{CC} < 1.5 \text{ V}$

- SN65' Version Bus-Pin ESD Protection Exceeds 15 kV

- Packaged in Thin Shrink Small-Outline Package With 20-mil Terminal Pitch

- Low-Voltage TTL (LVTTL) Logic Inputs Are 5-V Tolerant

## description

This family of four, eight, and sixteen differential line drivers implements the electrical characteristics of low-voltage differential signaling (LVDS). This signaling technique lowers the output voltage levels of 5-V differential standard levels (such as EIA/TIA-422B) to reduce the power, increase the switching speeds, and allow operation with a 3.3-V supply rail. Any of the sixteen current-mode drivers will deliver a minimum differential output voltage magnitude of 247 mV into a 100-Ω load when enabled.

| DBT PACKAGE     |       |         |      | D                 | DGG PACKAGE |                      |  |  |

|-----------------|-------|---------|------|-------------------|-------------|----------------------|--|--|

| (TOP VIEW)      |       |         | )    |                   | (TOF        | P VIEW)              |  |  |

| GND [           | 10    | 38      | A1Y  | GND [             | ┧╸╵         |                      |  |  |

| V <sub>CC</sub> | 2     | 37      | A1Z  | V <sub>CC</sub> [ | 2           | 63 A1Z               |  |  |

| GND             | 3     | 36      | A2Y  | V <sub>CC</sub> [ | 3           | 62 A2Y               |  |  |

| ENA 🛚           | 4     | 35      | A2Z  | GND [             | 4           | 61 A2Z               |  |  |

| A1A             | 5     | 34      | A3Y  | ENA [             | 5           | 60 A3Y               |  |  |

| A2A 🛮           | 6     | 33      | A3Z  | A1A [             | 6           | <sub>59</sub> ] A3Z  |  |  |

| АЗА [           | 7     | 32      | A4Y  | A2A [             | 7           | 58 🛚 A4Y             |  |  |

| A4A [           | 8     | 31      | A4Z  | A3A [             | 8           | 57 🛮 A4Z             |  |  |

| GND [           | 9     | 30      | ]NC  | A4A               | 9           | 56 B1Y               |  |  |

| Vcc [           | 10    | 29      | ]NC  | ENB [             | 10          | 55 B1Z               |  |  |

| GND [           | 11    | 28      | ]NC  | B1A [             | 11          | 54 B2Y               |  |  |

| B1A [           | 12    | 27      | B1Y  | B2A [             | 7           | 53 B2Z               |  |  |

| B2A 🏻           | 13    | 26      | B1Z  | B3A [             | 1           | 52 B3Y               |  |  |

| ВЗА 🛚           | 14    | 25      | B2Y  | B4A [             | 7           | 51 B3Z               |  |  |

| B4A [           | 15    | 24      | B2Z  | GND [             | 15          | 50 B4Y               |  |  |

| ENB [           | 16    | 23      | B3Y  | V <sub>CC</sub> [ | 16          | 49 B4Z               |  |  |

| GND [           | 17    | 22      | B3Z  | V <sub>CC</sub> [ | 17          | 48 C1Y               |  |  |

| V <sub>CC</sub> | 18    | 21      | B4Y  | GND [<br>C1A [    | 18          | 47 C1Z               |  |  |

| GND [           | 19    | 20      | B4Z  | C1A [             | 19          | 46 C2Y<br>45 C2Z     |  |  |

|                 |       |         |      | C2A [             | 20<br>21    | 45   C2Z<br>44   C3Y |  |  |

|                 | 'LVD  |         |      | C4A [             | 22          | 43 C3Z               |  |  |

|                 | PW F  |         |      | ENC [             | 23          | 43 0 032<br>42 C4Y   |  |  |

| (               | TOP \ | /IEVV)  |      | D1A [             | 24          | 41 C4Z               |  |  |

| EN1,2 [         | 1 C   | ر<br>16 | ] 1Y | D2A [             | 25          | 40 D1Y               |  |  |

| 1A              | 2     | 15      | 2    | D3A [             | 26          | 39 D1Z               |  |  |

| 2A [            | 3     |         | 2Y   | D4A               | 27          | 38 D2Y               |  |  |

| Vcc [           | 4     |         | 2Z   | END [             | 28          | 37 D2Z               |  |  |

| GND [           | 5     | 12      |      | GND [             | 29          | 36 D3Y               |  |  |

| 3A [            | 6     | 11      | 3Z   | V <sub>CC</sub> [ | 30          | 35 D3Z               |  |  |

| 4A [            | 7     | 10      | ] 4Y | Vcc [             | 31          | 34 🛭 D4Y             |  |  |

| EN3,4 [         | 8     | 9       | 4Z   | GND [             | 32          | 33 D4Z               |  |  |

|                 |       |         |      |                   | Щ           |                      |  |  |

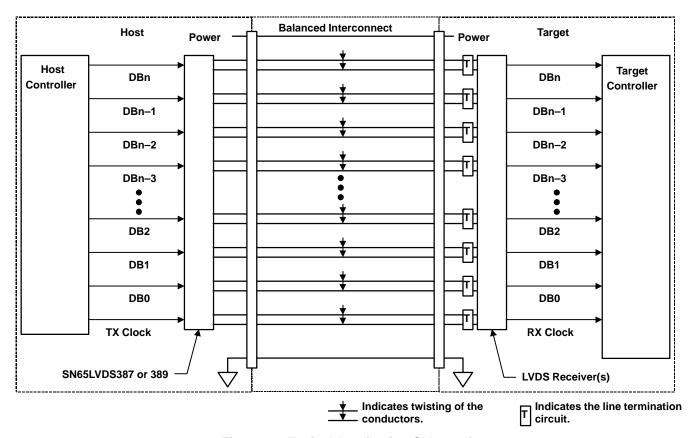

The intended application of this device and signaling technique is for point-to-point and multidrop baseband data transmission over controlled impedance media of approximately 100  $\Omega$ . The transmission media can be printed-circuit board traces, backplanes, or cables. The large number of drivers integrated into the same substrate, along with the low pulse skew of balanced signaling, allows extremely precise timing alignment of clock and data for synchronous parallel data transfers. When used with the companion 16- or 8-channel receivers, the SN65LVDS386 or SN65LVDS388, over 300 million data transfers per second in single-edge clocked systems are possible with very little power. (Note: The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media, the noise coupling to the environment, and other system characteristics.)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† Signaling rate, 1/t, where t is the minimum unit interval and is expressed in the units bits/s (bits per second)

## description (continued)

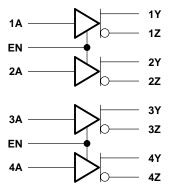

When disabled, the driver outputs are high impedance. Each driver input (A) and enable (EN) have an internal pulldown that will drive the input to a low level when open circuited.

The SN65LVDS387, SN65LVDS389, and SN65LVDS391 are characterized for operation from –40°C to 85°C. The SN75LVDS387, SN75LVDS389, and SN75LVDS391 are characterized for operation from 0°C to 70°C.

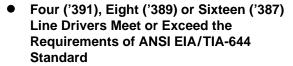

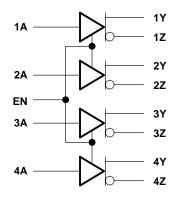

## logic diagram (positive logic)

(1/4 of 'LVDS387 or 1/2 of 'LVDS389 shown)

('LVDS391 shown)

#### **AVAILABLE OPTIONS**

| PART NUMBER†   | TEMPERATURE<br>RANGE | NO. OF<br>DRIVERS | BUS-PIN<br>ESD |

|----------------|----------------------|-------------------|----------------|

| SN65LVDS387DGG | –40°C to 85°C        | 16                | 15 kV          |

| SN75LVDS387DGG | 0°C to 70°C          | 16                | 4 kV           |

| SN65LVDS389DBT | –40°C to 85°C        | 8                 | 15 kV          |

| SN75LVDS389DBT | 0°C to 70°C          | 8                 | 4 kV           |

| SN65LVDS391D   | –40°C to 85°C        | 4                 | 15 kV          |

| SN75LVDS391D   | 0°C to 70°C          | 4                 | 4 kV           |

| SN65LVDS391PW  | –40°C to 85°C        | 4                 | 15 kV          |

| SN75LVDS391PW  | 0°C to 70°C          | 4                 | 4 kV           |

This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., SN65LVDS387DGGR).

#### **DRIVER FUNCTION TABLE**

| INPUT | ENABLE | OUTPUTS |   |

|-------|--------|---------|---|

| Α     | EN     | Υ       | Z |

| Н     | Н      | Н       | L |

| L     | Н      | L       | Н |

| Х     | L      | Z       | Z |

| OPEN  | Н      | L       | Н |

H = high-level, L = low-level, X = irrelevant,

Z = high-impedance (off)

## equivalent input and output schematic diagrams

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                      | 0.5 V to 4 V                   |

|------------------------------------------------------------|--------------------------------|

| Input voltage range: Inputs                                | 0.5 V to 6 V                   |

| Y or Z                                                     | 0.5 V to 4 V                   |

| Electrostatic discharge: SN65' (Y, Z, and GND)             | Class 3, A:15 kV, B: 500 V     |

| SN75' (Y, Z, and GND)                                      | Class 3, A:4 kV, B: 400 V      |

| Continuous power dissipation                               | (see Dissipation Rating Table) |

| Storage temperature range                                  | 65°C to 150°C                  |

| Lead temperature 1,6 mm (1/16 in) from case for 10 seconds | 260°C                          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | CKAGE 1 14 < 25°C 1 1 7 |            | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|-------------------------|------------|---------------------------------------|---------------------------------------|

| D       | 950 mW                  | 7.6 mW/°C  | 608 mW                                | 494 mW                                |

| DBT     | 1071 mW                 | 8.5 mW/°C  | 688 mW                                | 556 mW                                |

| DGG     | 2094 mW                 | 16.7 mW/°C | 1342 mW                               | 1089 mW                               |

| PW      | 774 mW                  | 6.2 mW/°C  | 496 mW                                | 402 mW                                |

<sup>‡</sup>This is the inverse of the junction-to-ambient thermal resistance when board-mounted (low-k) and with no air flow.

#### recommended operating conditions

|                                                |       | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-------|-----|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                |       |     |     | 3.6 | V    |

| High-level input voltage, V <sub>IH</sub>      |       |     |     |     | V    |

| Low-level input voltage, V <sub>IL</sub>       |       |     |     | 0.8 | V    |

| Operating free cir temperature T.              | SN75' | 0   |     | 70  | °C   |

| Operating free-air temperature, T <sub>A</sub> | SN65' | -40 |     | 85  | °C   |

NOTES: 1. All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

<sup>2.</sup> Tested in accordance with MIL-STD-883C Method 3015.7.

# SN65LVDS387, SN75LVDS387, SN65LVDS389 SN75LVDS389, SN65LVDS391, SN75LVDS391 HIGH-SPEED DIFFERENTIAL LINE DRIVERS

SLLS362D - SEPTEMBER 1999 - REVISED MAY 2001

## electrical characteristics over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                                              | TEST CONDITIONS                                        |                                                         | MIN   | TYP <sup>†</sup> | MAX   | UNIT |

|-----------------------|------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|-------|------------------|-------|------|

| IVODI                 | Differential output voltage magnitude                                  | D 400.0                                                |                                                         | 247   | 340              | 454   |      |

| Δ V <sub>OD</sub>     | Change in differential output voltage magnitude between logic states   |                                                        | $R_L = 100  \Omega_{\rm i}$ , See Figure 1 and Figure 2 |       |                  | 50    | mV   |

| V <sub>OC(SS)</sub>   | Steady-state common-mode output voltage                                |                                                        |                                                         | 1.125 |                  | 1.375 | V    |

| ΔV <sub>OC</sub> (SS) | Change in steady-state common-mode output voltage between logic states | See Figure 3                                           |                                                         | -50   |                  | 50    | mV   |

| V <sub>OC(PP)</sub>   | Peak-to-peak common-mode output voltage                                | 1                                                      |                                                         |       | 50               | 150   | mV   |

|                       |                                                                        | 'LVDS387                                               | Enabled,                                                |       | 85               | 95    |      |

|                       |                                                                        | 'LVDS389 $R_L = 100 \Omega$ ,                          | $R_L = 100 \Omega$ ,                                    |       | 50               | 70    |      |

|                       | VIN = 0.8 V or 2 V                                                     |                                                        | 20                                                      | 26    |                  |       |      |

| Icc                   |                                                                        | 'LVDS387                                               |                                                         |       | 0.5              | 1.5   | mA   |

|                       |                                                                        | 'LVDS389                                               |                                                         |       | 0.5              | 1.5   |      |

|                       |                                                                        | 'LVDS391                                               |                                                         |       | 0.5              | 1.3   |      |

| lн                    | High-level input current                                               | V <sub>IH</sub> = 2 V                                  |                                                         |       | 3                | 20    | μΑ   |

| I <sub>I</sub> L      | Low-level input current                                                | V <sub>IL</sub> = 0.8 V                                | V <sub>IL</sub> = 0.8 V                                 |       | 2                | 10    | μΑ   |

|                       | Chart singuit autout aumant                                            | $V_{OY}$ or $V_{OZ} = 0$ V                             |                                                         |       |                  | ±24   | mA   |

| los                   | Short-circuit output current $V_{OD} = 0 \text{ V}$                    |                                                        |                                                         |       |                  | ±12   | mA   |

| loz                   | High-impedance output current                                          | $V_O = 0 \text{ V or } V_{CC}$                         |                                                         |       |                  | ±1    | μΑ   |

| lO(OFF)               | Power-off output current                                               | $V_{CC} = 1.5 \text{ V}, \qquad V_{O} = 2.4 \text{ V}$ |                                                         |       |                  | ±1    | μΑ   |

| C <sub>IN</sub>       | Input capacitance                                                      | V <sub>I</sub> = 0.4 sin (4E6πt) + 0.5 V               |                                                         |       | 5                |       | pF   |

| СО                    | Output capacitance                                                     | V <sub>I</sub> = 0.4 sin (4E6πt) +<br>Disabled         | 0.5 V,                                                  |       | 9.4              |       | pF   |

<sup>†</sup> All typical values are at 25°C and with a 3.3-V supply.

## switching characteristics over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                                   | TEST CONDITIONS          | MIN | TYP† | MAX | UNIT |

|--------------------|-------------------------------------------------------------|--------------------------|-----|------|-----|------|

| tPLH               | Propagation delay time, low-to-high-level output            |                          | 0.9 | 1.7  | 2.9 | ns   |

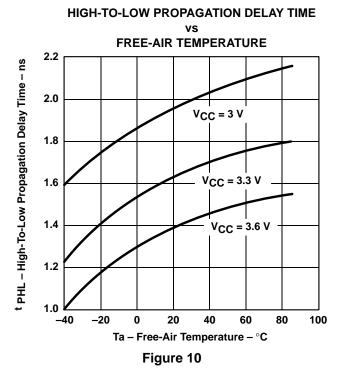

| t <sub>PHL</sub>   | Propagation delay time, high-to-low-level output            |                          | 0.9 | 1.6  | 2.9 | ns   |

| t <sub>r</sub>     | Differential output signal rise time                        | $R_1 = 100 \Omega$       | 0.4 | 0.8  | 1   | ns   |

| t <sub>f</sub>     | Differential output signal fall time                        | $C_{L} = 10 \text{ pF},$ | 0.4 | 0.8  | 1   | ns   |

| t <sub>sk(p)</sub> | Pulse skew ( tpHL - tpLH )                                  | See Figure 4             |     | 150  | 500 | ps   |

| t <sub>sk(o)</sub> | Output skew <sup>‡</sup>                                    |                          |     | 80   | 150 | ps   |

| tsk(pp)            | Part-to-part skew§                                          |                          |     |      | 1.5 | ns   |

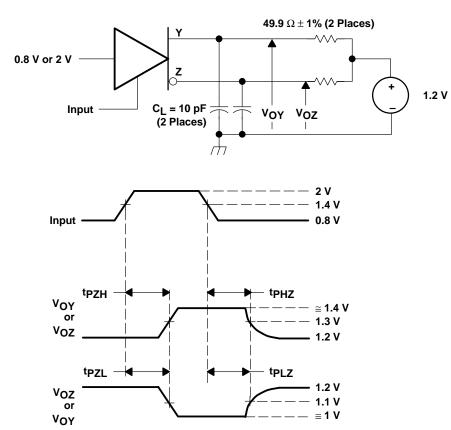

| <sup>t</sup> PZH   | Propagation delay time, high-impedance-to-high-level output |                          |     | 6.4  | 15  | ns   |

| tPZL               | Propagation delay time, high-impedance-to-low-level output  | See Figure 5             |     | 5.9  | 15  | ns   |

| <sup>t</sup> PHZ   | Propagation delay time, high-level-to-high-impedance output | See Figure 5             |     | 3.5  | 15  | ns   |

| t <sub>PLZ</sub>   | Propagation delay time, low-level-to-high-impedance output  |                          |     | 4.5  | 15  | ns   |

<sup>&</sup>lt;sup>†</sup> All typical values are at 25°C and with a 3.3-V supply.

<sup>‡</sup>t<sub>sk(0)</sub> is the magnitude of the time difference between the t<sub>PLH</sub> or t<sub>PHL</sub> of all drivers of a single device with all of their inputs connected together.

<sup>§</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of any two devices characterized in this data sheet when both devices operate with the same supply voltage, at the same temperature, and have the same test circuits.

## PARAMETER MEASUREMENT INFORMATION

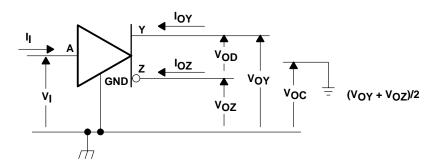

**Figure 1. Voltage and Current Definitions**

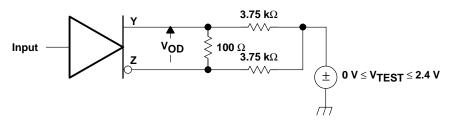

Figure 2. VOD Test Circuit

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_{\Gamma}$  or  $t_{\Gamma} \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width =  $500 \pm 10$  ns. C<sub>L</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T. The measurement of V<sub>OC</sub>(PP) is made on test equipment with a -3 dB bandwidth of at least 300 MHz.

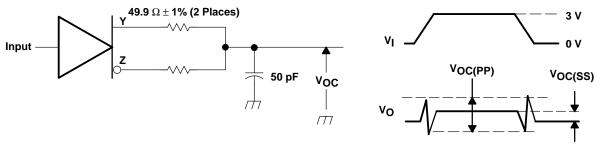

Figure 3. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

NOTE: All input pulses are supplied by a generator having the following characteristics: t<sub>r</sub> or t<sub>f</sub> ≤ 1 ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10 ± 0.2 ns. C<sub>I</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

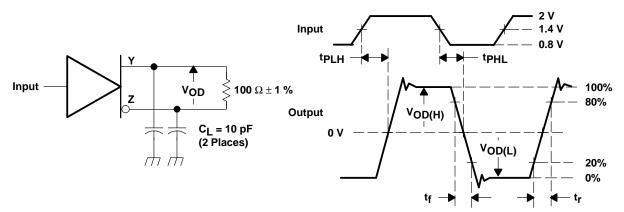

Figure 4. Test Circuit, Timing, and Voltage Definitions for the Differential Output Signal

#### PARAMETER MEASUREMENT INFORMATION

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_{\Gamma}$  or  $t_{f} \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width =  $500 \pm 10$  ns.  $C_{L}$  includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

Figure 5. Enable and Disable Time Circuit and Definitions

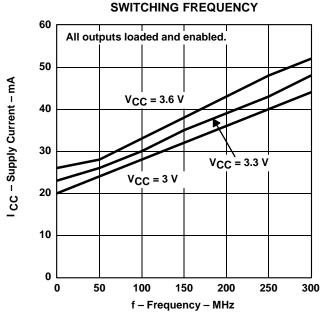

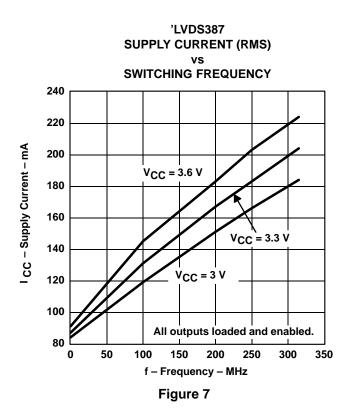

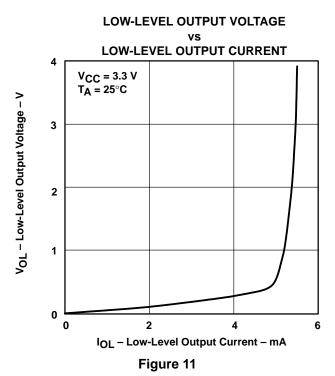

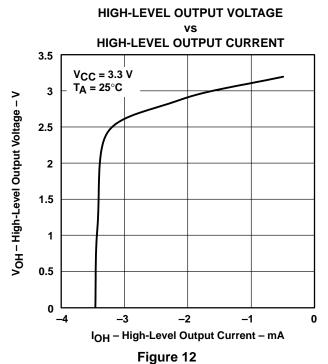

## **TYPICAL CHARACTERISTICS**

## 'LVDS391 SUPPLY CURRENT (RMS) vs

Figure 6

'LVDS389 **SUPPLY CURRENT (RMS) SWITCHING FREQUENCY** 110 100 I CC - Supply Current - mA 90 80  $V_{CC} = 3.6 V$ 70 V<sub>CC</sub> = 3.3 V 60  $V_{CC} = 3 V$ 50 All outputs loaded and enabled. 40 50 0 100 150 200 250 300 f - Frequency - MHz

Figure 8

#### **TYPICAL CHARACTERISTICS**

## **LOW-TO-HIGH PROPAGATION DELAY TIME** FREE-AIR TEMPERATURE 2.1 <sup>t</sup> PLH – Low-To-High Propagation Delay Time – ns 2.0 V<sub>CC</sub> = 3.6 V 1.9 1.8 1.7 V<sub>CC</sub> = 3 V 1.6 V<sub>CC</sub> = 3.3 V 1.5 1.4 1.3 -40 100 -20 20 40 80 60 T<sub>A</sub> - Free-Air Temperature - °C Figure 9

## **TYPICAL CHARACTERISTICS**

#### **OUTPUT VOLTAGE**

t - Time - ns

Figure 13

#### **APPLICATION INFORMATION**

Figure 14. Typical Application Schematic

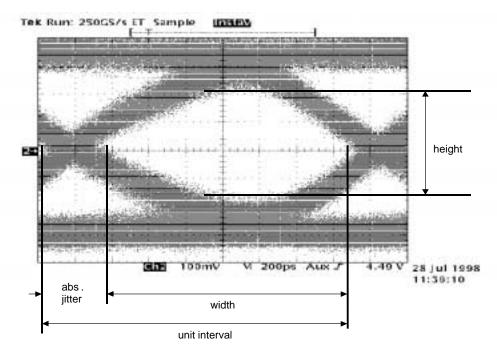

#### Signaling Rate vs Distance

The ultimate data transfer rate over a given cable or trace length involves many variables. Starting with the capabilities of this LVDS driver to reproduce a data pulse as short as 1.6 ns (a 630 Mbps signaling rate) with less than 500 ps of pulse distortion, any degradation of this pulse by the transmission media will necessarily reduce the timing margin at the receiving end of the data link.

The timing uncertainty induced by the transmission media is commonly referred to as jitter and comes from numerous sources. The characteristics of a particular transmission media can be quantified by using an eyepattern measurement such as shown in Figure 12, which shows about 340 ps of jitter or 20% of the data pulse width.

#### **APPLICATION INFORMATION**

Figure 15. Typical LVDS Eyepattern

A generally accepted range of jitter at the receiver inputs that allows data recovery is 5% to 20% of the unit interval (data pulse width). Table 1 shows the signaling rate achieved on various cables and lengths at a 5% eyepattern jitter with a typical LVDS driver.

Table 1. Signaling Rates for Various Cables for 5% Eyepattern Jitter

| LENGTH | CABLE <sup>†</sup> |             |             |             |             |             |  |

|--------|--------------------|-------------|-------------|-------------|-------------|-------------|--|

| (m)    | A<br>(Mbps)        | B<br>(Mbps) | C<br>(Mbps) | D<br>(Mbps) | E<br>(Mbps) | F<br>(Mbps) |  |

| 1      | 240                | 200         | 240         | 270         | 180         | 230         |  |

| 5      | 205                | 210         | 230         | 250         | 215         | 230         |  |

| 10     | 180                | 150         | 195         | 200         | 145         | 180         |  |

<sup>†</sup> Cable A: CAT 3, specified up to 16 MHz, no shield, outside conductor diameter (Ø) 0.52 mm

Cable B: CAT 5, specified up to 100 MHz, no shield, Ø 0.52 mm

Cable C: CAT 5, specified up to 100 MHz, taped over all shield,  $\varnothing$  0.52 mm

Cable D: CAT 5 (exceeding CAT 5), specified up to 300 MHz, braided over all shield plus taped individual shield for any pair,  $\varnothing$  0.64 mm (AWG22)

Cable E: CAT 5 (exceeding CAT 5), specified up to 350 MHz,  $\varnothing$  0.64 mm (AWG22), no shield

Cable F: CAT 5 (exceeding CAT 5), specified up to 350 MHz, "self-shielded", Ø 0.64 mm (AWG22)

During synchronous parallel transfers, skew between the data and clock lines will also reduce the timing margin. This must be accounted for in the system timing budget. Fortunately, the low output skew of this LVDS driver will generally be a small portion of this budget.

#### other LVDS products

For other products and applications notes in the LVDS and LVDM product families visit our Web site at http://www.ti.com/sc/datatran.

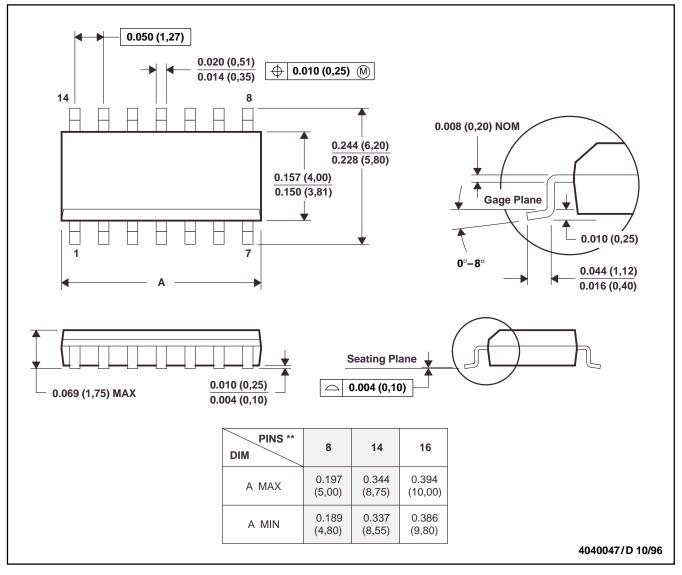

## **MECHANICAL DATA**

## D (R-PDSO-G\*\*)

#### 14 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-012

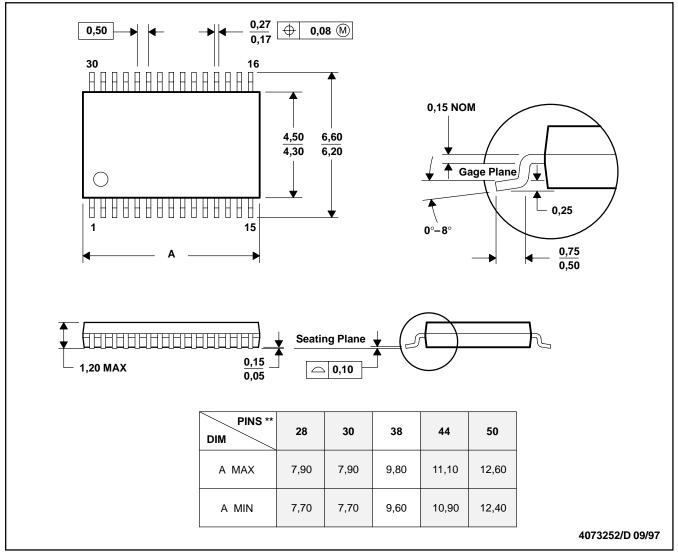

#### **MECHANICAL DATA**

## DBT (R-PDSO-G\*\*)

#### **30 PINS SHOWN**

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion.

D. Falls within JEDEC MO-153

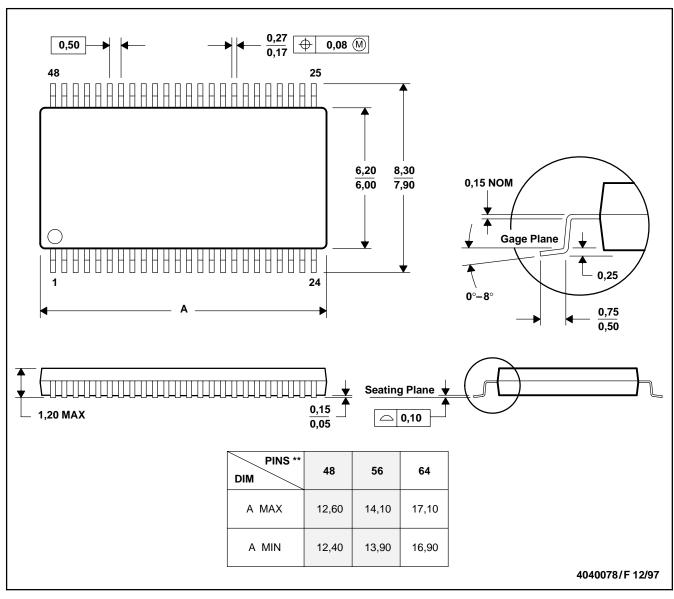

## **MECHANICAL DATA**

## DGG (R-PDSO-G\*\*)

## 48 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

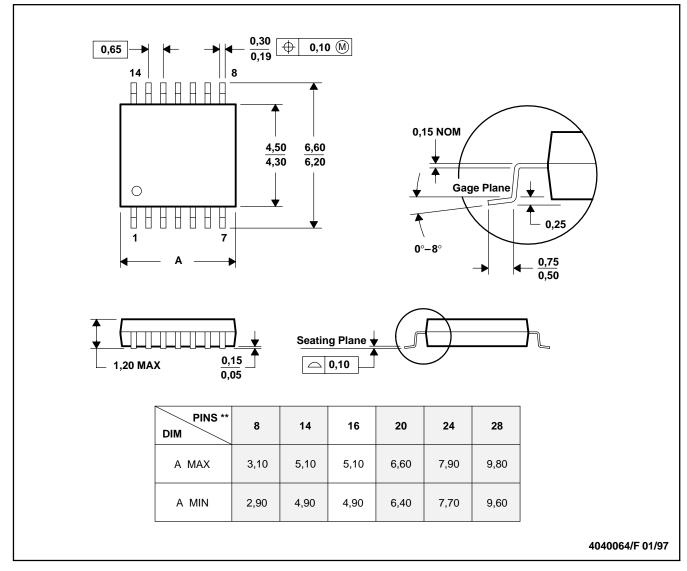

#### **MECHANICAL DATA**

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products, www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265