SBAS267A - MARCH 2003 - REVISED SEPTEMBER 2004

# Precision Analog-to-Digital Converter (ADC) and Digital-to-Analog Converters (DACs) with 8051 Microcontroller and Flash Memory

#### **FEATURES**

#### **ANALOG FEATURES**

- 24-BITS NO MISSING CODES

- 22-BITS EFFECTIVE RESOLUTION AT 10Hz Low Noise: 75nV

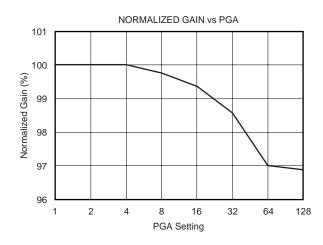

- PGA FROM 1 TO 128

- PRECISION ON-CHIP VOLTAGE REFERENCE:

Accuracy: 0.2% Drift: 5ppm/°C

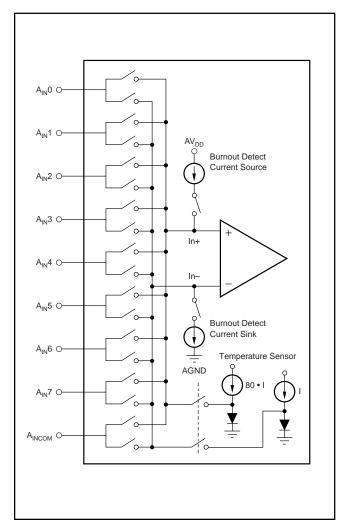

- 8 DIFFERENTIAL/SINGLE-ENDED CHANNELS

- ON-CHIP OFFSET/GAIN CALIBRATION

- OFFSET DRIFT: 0.02PPM/°C

- GAIN DRIFT: 0.5PPM/°C

- ON-CHIP TEMPERATURE SENSOR

- SELECTABLE BUFFER INPUT

- BURNOUT DETECT

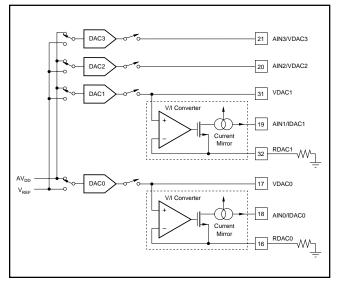

- QUAD 16-BIT MONOTONIC VOLTAGE DACs:

2 VDACs Can Be Programmed as IDACs

8µs Settling Time

#### **DIGITAL FEATURES**

#### **Microcontroller Core**

- 8051 COMPATIBLE

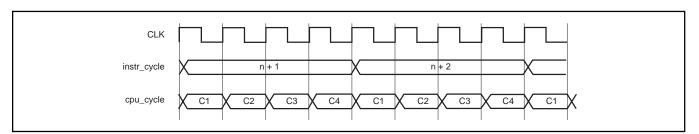

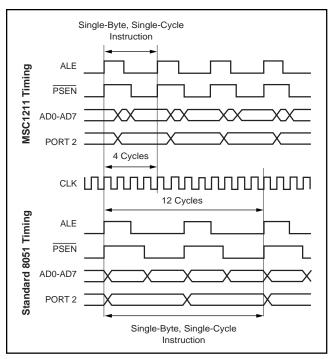

- HIGH SPEED CORE:

Clocks per Instruction

- 4 Clocks per Instruction Cycle

- DC TO 30MHz

- SINGLE INSTRUCTION 133ns

- DUAL DATA POINTER

#### Memory

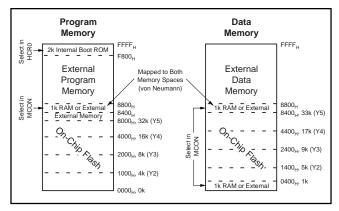

- UP TO 32kB FLASH DATA MEMORY

- FLASH MEMORY PARTITIONING

- ENDURANCE 1M ERASE/WRITE CYCLES,

100 YEAR DATA RETENTION

- IN-SYSTEM SERIALLY PROGRAMMABLE

- EXTERNAL PROGRAM/DATA MEMORY (64kB)

- 1280 BYTES DATA SRAM

- FLASH MEMORY SECURITY

- 2kB BOOT ROM

- PROGRAMMABLE WAIT STATE CONTROL

#### **Peripheral Features**

- 34 I/O PINS

- ADDITIONAL 32-BIT ACCUMULATOR

- THREE 16-BIT TIMER/COUNTERS

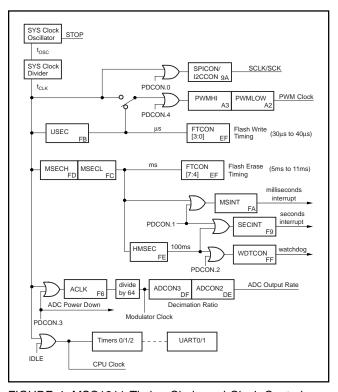

- SYSTEM TIMERS

- PROGRAMMABLE WATCHDOG TIMER

- FULL DUPLEX DUAL UART

- MASTER/SLAVE SPI<sup>™</sup> WITH DMA

- MULTI-MASTER I2C™

- 16-BIT PWM

- POWER MANAGEMENT CONTROL

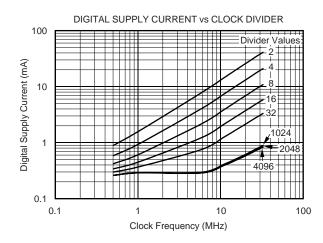

- INTERNAL CLOCK DIVIDER

- IDLE MODE CURRENT < 200µA

- STOP MODE CURRENT < 100nA

- PROGRAMMABLE BROWNOUT RESET

- PROGRAMMABLE LOW VOLTAGE DETECT

- 21 INTERRUPT SOURCES

- TWO HARDWARE BREAKPOINTS

#### **GENERAL FEATURES**

- PIN COMPATIBLE WITH MSC1210 FAMILY

- PACKAGE: TQFP-64

- LOW POWER: 4mW

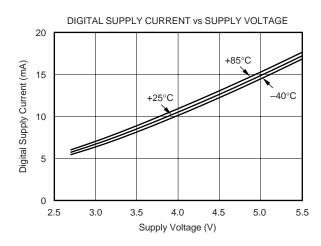

- INDUSTRIAL TEMPERATURE RANGE: -40°C to +85°C

- POWER SUPPLY: 2.7V to 5.25V

#### **APPLICATIONS**

- INDUSTRIAL PROCESS CONTROL

- **INSTRUMENTATION**

- LIQUID/GAS CHROMATOGRAPHY

- BLOOD ANALYSIS

- SMART TRANSMITTERS

- PORTABLE INSTRUMENTS

- WEIGH SCALES

- PRESSURE TRANSDUCERS

- INTELLIGENT SENSORS

- PORTABLE APPLICATIONS

- DAS SYSTEMS

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

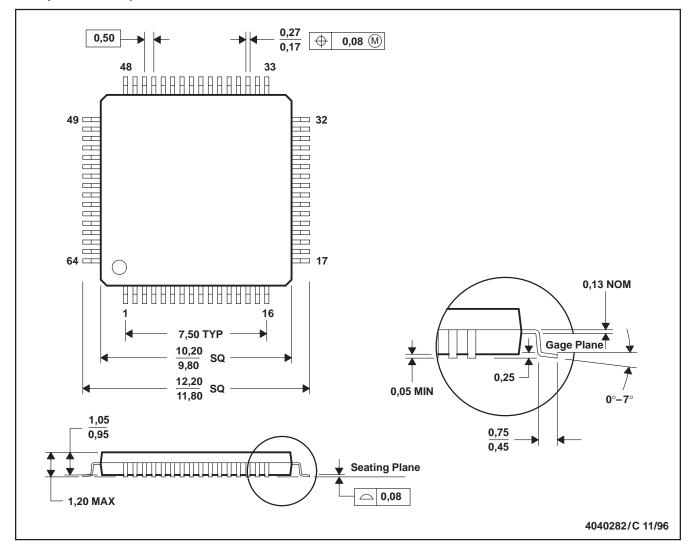

#### **PACKAGE/ORDERING INFORMATION**

| PRODUCT                | FLASH<br>MEMORY | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER             | TRANSPORT<br>MEDIA, QUANTITY              |

|------------------------|-----------------|--------------|--------------------------------------|-----------------------------------|--------------------|--------------------------------|-------------------------------------------|

| MSC1211Y2<br>MSC1211Y2 | 4k<br>4k        | TQFP-64      | PAG<br>"                             | -40°C to +85°C                    | MSC1211Y2          | MSC1211Y2PAGT<br>MSC1211Y2PAGR | Tape and Reel, 250<br>Tape and Reel, 2000 |

| MSC1211Y3<br>MSC1211Y3 | 8k<br>8k        | TQFP-64      | PAG<br>"                             | -40°C to +85°C                    | MSC1211Y3          | MSC1211Y3PAGT<br>MSC1211Y3PAGR | Tape and Reel, 250<br>Tape and Reel, 2000 |

| MSC1211Y4<br>MSC1211Y4 | 16k<br>16k      | TQFP-64      | PAG<br>"                             | –40°C to +85°C                    | MSC1211Y4          | MSC1211Y4PAGT<br>MSC1211Y4PAGR | Tape and Reel, 250<br>Tape and Reel, 2000 |

| MSC1211Y5<br>MSC1211Y5 | 32k<br>32k      | TQFP-64<br>" | PAG<br>"                             | -40°C to +85°C                    | MSC1211Y5          | MSC1211Y5PAGT<br>MSC1211Y5PAGR | Tape and Reel, 250<br>Tape and Reel, 2000 |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com/msc.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Analog Inputs  Input Current                                   |

|----------------------------------------------------------------|

| Input Current                                                  |

| Input Voltage                                                  |

| Power Supply DV <sub>DD</sub> to DGND0.3V to 6V                |

| DV <sub>DD</sub> to DGND0.3V to 6V                             |

|                                                                |

| Λ\/ +0 ΛCND 0.3\/ +0 6\/                                       |

| AV <sub>DD</sub> to AGND0.3V to 6V                             |

| AGND to DGND0.3V to +0.3V                                      |

| $V_{REF}$ to AGND $-0.3V$ to $AV_{DD} + 0.3V$                  |

| Digital Input Voltage to DGND0.3V to DV <sub>DD</sub> + 0.3V   |

| Digital Output Voltage to DGND0.3V to DV <sub>DD</sub> + 0.3V  |

| Maximum Junction Temperature+150°C                             |

| Operating Temperature Range –40°C to +85°C                     |

| Storage Temperature Range –65°C to +150°C                      |

| Lead Temperature (soldering, 10s)+300°C                        |

| Package Power Dissipation                                      |

| Output Current All Pins                                        |

| Output Pin Short Circuit10s                                    |

| Thermal Resistance, Junction-to-Ambient ( $\theta_{JA}$ )      |

| Thermal Resistance, Junction-to-Case ( $\theta_{JC}$ ) 4.3°C/W |

| Digital Outputs                                                |

| Output Current                                                 |

| I/O Source/Sink Current                                        |

| Power Pin Maximum                                              |

NOTE: (1) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **MSC1211Yx FAMILY FEATURES**

| FEATURES <sup>(1)</sup>              | MSC1211Y2 <sup>(2)</sup> | MSC1211Y3 <sup>(2)</sup> | MSC1211Y4 <sup>(2)</sup> | MSC1211Y5 <sup>(2)</sup> |

|--------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| Flash Program Memory (Bytes)         | Up to 4k                 | Up to 8k                 | Up to 16k                | Up to 32k                |

| Flash Data Memory (Bytes)            | Up to 4k                 | Up to 8k                 | Up to 16k                | Up to 32k                |

| Internal Scratchpad RAM (Bytes)      | 256                      | 256                      | 256                      | 256                      |

| Internal MOVX SRAM (Bytes)           | 1024                     | 1024                     | 1024                     | 1024                     |

| Externally Accessible Memory (Bytes) | 64k Program, 64k Data    |

NOTES: (1) All peripheral features are the same on all devices; the flash memory size is the only difference. (2) The last digit of the part number (N) represents the onboard flash size =  $(2^N)kBytes$ .

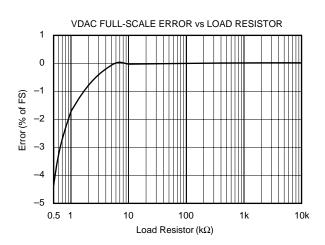

## ELECTRICAL CHARACTERISTICS: $AV_{DD} = 5V$

All specifications from  $T_{MIN}$  to  $T_{MAX}$ ,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 15.625kHz, PGA = 1, Buffer ON,  $f_{DATA}$  = 10Hz, Bipolar, and  $V_{REF}$   $\equiv$  (REF IN+) - (REF IN-) = +2.5V, unless otherwise noted. For  $V_{DAC}$ ,  $V_{REF}$  =  $AV_{DD}$ ,  $R_{LOAD}$  = 10k $\Omega$ , and  $C_{LOAD}$  = 200pF, unless otherwise noted.

|                                                     |                                                           | MSC1211Yx   |                              |                        |                      |  |

|-----------------------------------------------------|-----------------------------------------------------------|-------------|------------------------------|------------------------|----------------------|--|

| PARAMETER                                           | CONDITION                                                 | MIN         | MIN TYP MAX                  |                        |                      |  |

| ANALOG INPUT (AIN0-AIN7, AINCOM) Analog Input Range | Buffer OFF                                                | AGND - 0.1  |                              | AV <sub>DD</sub> + 0.1 | V                    |  |

| , maiog input rungo                                 | Buffer ON                                                 | AGND + 50mV |                              | AV <sub>DD</sub> – 1.5 | ľ                    |  |

| Full-Scale Input Voltage Range                      | (In+) – (In–) See Figure 4                                | THE TOURING |                              | ±V <sub>REF</sub> /PGA | ľ                    |  |

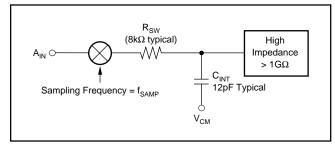

| Differential Input Impedance                        | Buffer OFF                                                |             | 5/PGA                        | ±VREF/1 OA             | MΩ                   |  |

| · ·                                                 |                                                           |             | 0.5                          |                        |                      |  |

| Input Current                                       | Buffer ON                                                 |             | 0.5                          |                        | nA                   |  |

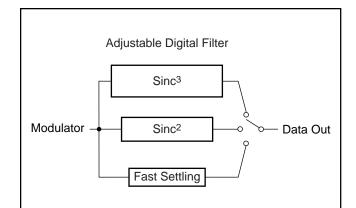

| Bandwidth                                           | 0.15                                                      |             |                              |                        |                      |  |

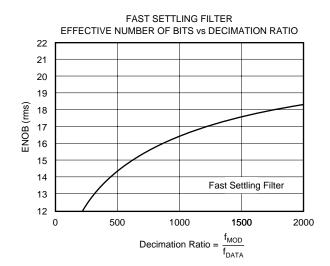

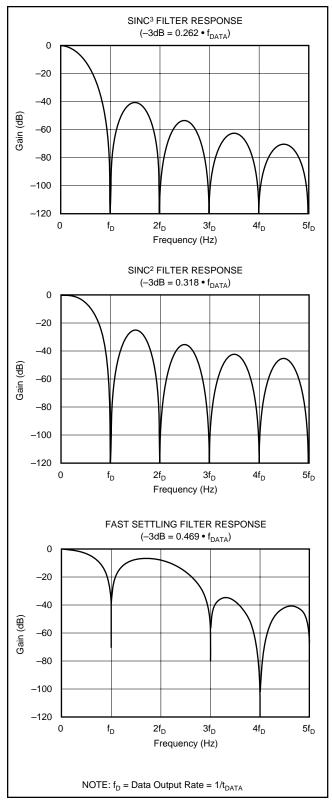

| Fast Settling Filter                                | -3dB                                                      |             | 0.469 • f <sub>DATA</sub>    |                        |                      |  |

| Sinc <sup>2</sup> Filter                            | -3dB                                                      |             | 0.318 • f <sub>DATA</sub>    |                        |                      |  |

| Sinc <sup>3</sup> Filter                            | −3dB                                                      |             | 0.262 • f <sub>DATA</sub>    |                        |                      |  |

| Programmable Gain Amplifier                         | User-Selectable Gain Ranges                               | 1           |                              | 128                    |                      |  |

| Input Capacitance                                   | Buffer ON                                                 |             | 4                            |                        | pF                   |  |

| Input Leakage Current                               | Multiplexer Channel Off, T = +25°C                        |             | 0.5                          |                        | pА                   |  |

| Burnout Current Sources                             | Sensor Input Open Circuit                                 |             | ±2                           |                        | μΑ                   |  |

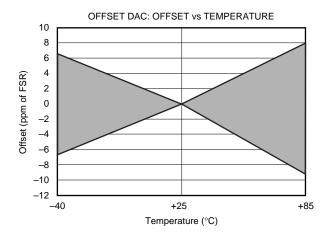

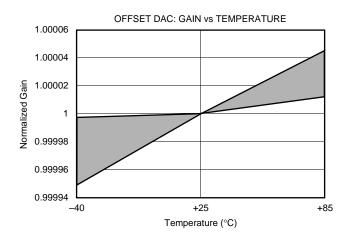

| ADC OFFSET DAC                                      |                                                           |             |                              |                        |                      |  |

| Offset DAC Range                                    |                                                           |             | ±V <sub>REF</sub> /(2 • PGA) |                        | V                    |  |

| Offset DAC Monotonicity                             |                                                           | 8           | - KEP (- 1 91 )              |                        | Bits                 |  |

| Offset DAC Gain Error                               |                                                           |             | ±1.5                         |                        | % of Range           |  |

| Offset DAC Gain Error Drift                         |                                                           |             | 1                            |                        | ppm/°C               |  |

|                                                     |                                                           |             |                              |                        | Pp, 0                |  |

| SYSTEM PERFORMANCE                                  |                                                           | 0.4         |                              |                        | D:4-                 |  |

| Resolution                                          |                                                           | 24          |                              |                        | Bits                 |  |

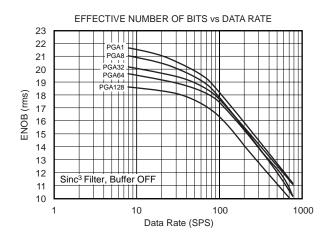

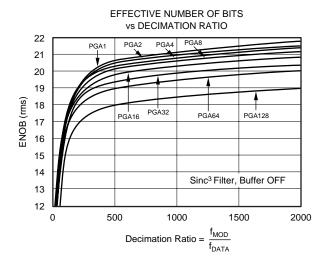

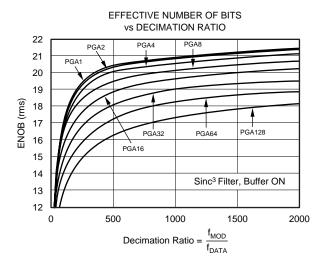

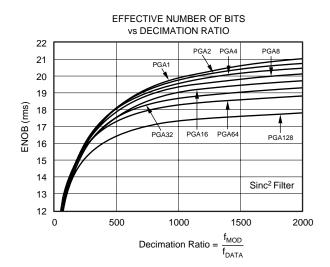

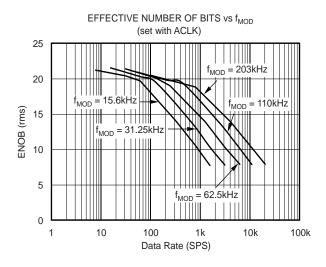

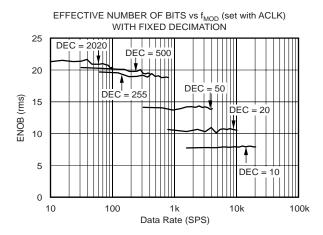

| ENOB                                                |                                                           |             | 22                           |                        | Bits                 |  |

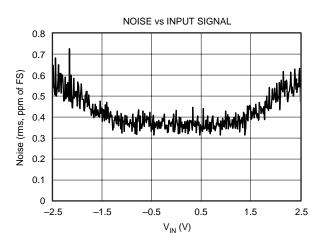

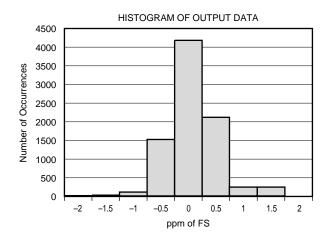

| Output Noise                                        |                                                           |             | Typical Characte             | ristics                |                      |  |

| No Missing Codes                                    | Sinc <sup>3</sup> Filter                                  | 24          |                              |                        | Bits                 |  |

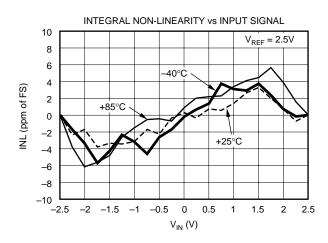

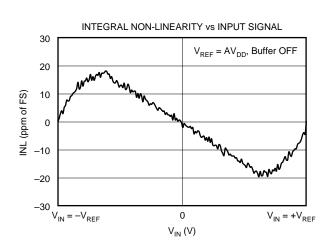

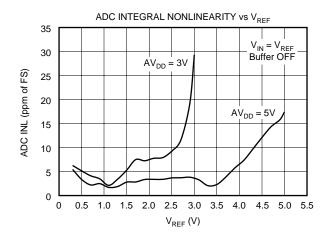

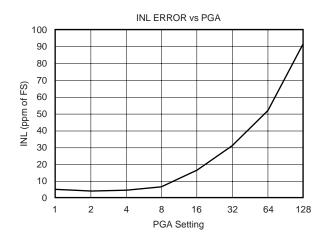

| Integral Nonlinearity                               | End Point Fit, Differential Input                         |             |                              | ±0.0015                | %FSR                 |  |

| Offset Error                                        | After Calibration                                         |             | 7.5                          |                        | ppm of FS            |  |

| Offset Drift <sup>(1)</sup>                         | Before Calibration                                        |             | 0.02                         |                        | ppm of FS/°          |  |

| Gain Error <sup>(2)</sup>                           | After Calibration                                         |             | 0.005                        |                        | %                    |  |

| Gain Error Drift(1)                                 | Before Calibration                                        |             | 0.5                          |                        | ppm/°C               |  |

| System Gain Calibration Range                       |                                                           | 80          |                              | 120                    | % of FS              |  |

| System Offset Calibration Range                     |                                                           | -50         |                              | 50                     | % of FS              |  |

| Common-Mode Rejection                               | At DC                                                     | 100         | 115                          | 00                     | dB                   |  |

| Common Mode Projection                              | $f_{CM} = 60Hz$ , $f_{DATA} = 10Hz$                       | 100         | 130                          |                        | dB                   |  |

|                                                     | $f_{CM} = 50Hz$ , $f_{DATA} = 50Hz$                       |             | 120                          |                        | dB                   |  |

|                                                     |                                                           |             |                              |                        |                      |  |

| N IM I B : e                                        | $f_{CM} = 60Hz$ , $f_{DATA} = 60Hz$                       |             | 120                          |                        | dB                   |  |

| Normal Mode Rejection                               | $f_{SIG} = 50Hz$ , $f_{DATA} = 50Hz$                      |             | 100                          |                        | dB                   |  |

| Davier Cumply Dejection                             | $f_{SIG} = 60Hz, f_{DATA} = 60Hz$                         |             | 100                          |                        | dB                   |  |

| Power-Supply Rejection                              | At DC, dB = $-20\log(\Delta V_{OUT}/\Delta V_{DD})^{(3)}$ |             | 88                           |                        | dB                   |  |

| VOLTAGE REFERENCE INPUTS                            |                                                           |             |                              |                        |                      |  |

| Reference Input Range                               | REF IN+, REF IN-                                          | 0.0         |                              | $AV_{DD}^{(2)}$        | V                    |  |

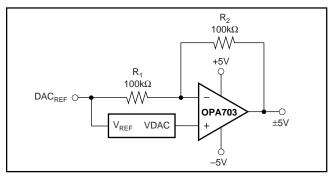

| ADC V <sub>REF</sub>                                | $V_{REF} \equiv (REF IN+) - (REF IN-)$                    | 0.3         | 2.5                          | $AV_DD$                | V                    |  |

| Common-Mode Rejection                               | At DC                                                     |             | 110                          |                        | dB                   |  |

| Input Current <sup>(4)</sup>                        | V <sub>REF</sub> = 2.5V, ADC Only                         |             | 10                           |                        | μΑ                   |  |

| DAC Reference Current                               | For Each DAC, 5V Reference                                |             | 25                           |                        | μΑ                   |  |

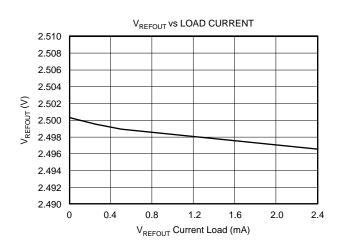

| ON-CHIP VOLTAGE REFERENCE                           |                                                           |             |                              |                        |                      |  |

| Output Voltage                                      | \/DEEH = 1 at 125°C DCA = 1 2 4 9                         | 2.495       | 2.5                          | 2.505                  | V                    |  |

| Output Voltage                                      | VREFH = 1 at +25°C, PGA = 1, 2, 4, 8<br>VREFH = 0         | 2.495       |                              | 2.505                  |                      |  |

| D 0 1 D : # D #                                     | VREFH = U                                                 |             | 1.25                         |                        | V                    |  |

| Power-Supply Rejection Ratio                        |                                                           |             | 65                           |                        | dB                   |  |

| Short-Circuit Current Source                        |                                                           |             | 8                            |                        | mA                   |  |

| Short-Circuit Current Sink                          |                                                           |             | 50                           |                        | μΑ                   |  |

| Short-Circuit Duration                              | Sink or Source                                            | İ           | Indefinite                   |                        | 1                    |  |

| Drift                                               |                                                           | 1           | 5                            |                        | ppm/°C               |  |

| Output Impedance                                    | Sourcing 100μA                                            | İ           | 3                            |                        | Ω                    |  |

| Startup Time from Power ON                          | $C_{REFOUT} = 0.1 \mu F$                                  | İ           | 8                            |                        | ms                   |  |

| Temperature Sensor                                  | 1.2.331                                                   | 1           |                              |                        | 1                    |  |

| Temperature Sensor Voltage                          | T = +25°C                                                 | 1           | 115                          |                        | mV                   |  |

| Temperature Sensor Coefficient                      | 1                                                         |             | 375                          |                        | μV/°C                |  |

| VOLTAGE DAC STATIC PERFORMANCE (5)                  |                                                           |             |                              |                        |                      |  |

| Resolution                                          |                                                           | 16          |                              |                        | Bits                 |  |

|                                                     |                                                           | "           | +0.05                        | +0 446                 |                      |  |

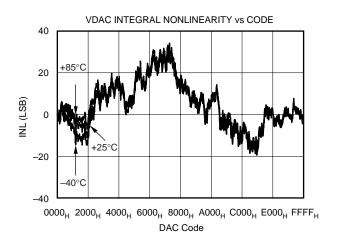

| Relative Accuracy                                   |                                                           | İ           | ±0.05                        | ±0.146                 | %<br>LCD             |  |

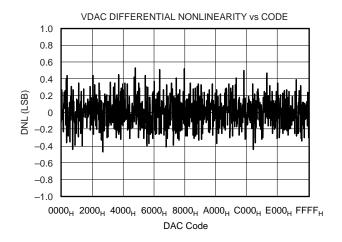

| Differential Nonlinearity                           | All On Louis BAG South                                    | I           | 40                           | ±1                     | LSB                  |  |

| Zero Code Error                                     | All 0s Loaded to DAC Register                             |             | +13                          | +35                    | mV                   |  |

| Full-Scale Error                                    | All 1s Loaded to DAC Register                             | -1.25       | 0                            |                        | % of FSR             |  |

| Gain Error                                          |                                                           | -1.25       | 0                            | +1.25                  | % of FSR             |  |

|                                                     |                                                           |             |                              |                        |                      |  |

| Zero Code Error Drift Gain Temperature Coefficient  |                                                           |             | ±20<br>±5                    |                        | μV/°C<br>ppm of FSR/ |  |

## ELECTRICAL CHARACTERISTICS: AV<sub>DD</sub> = 5V (Cont.)

All specifications from  $T_{MIN}$  to  $T_{MAX}$ ,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 15.625kHz, PGA = 1, Buffer ON,  $f_{DATA}$  = 10Hz, Bipolar, and  $V_{REF}$  = (REF IN+) – (REF IN-) = +2.5V, unless otherwise noted. For  $V_{DAC}$ ,  $V_{REF}$  = AV $_{DD}$ ,  $R_{LOAD}$  = 10k $\Omega$ , and  $C_{LOAD}$  = 200pF, unless otherwise noted.

|                                                   |                                                     |      | MSC1211Yx              |                  |          |

|---------------------------------------------------|-----------------------------------------------------|------|------------------------|------------------|----------|

| PARAMETER                                         | CONDITION                                           | MIN  | TYP                    | MAX              | UNITS    |

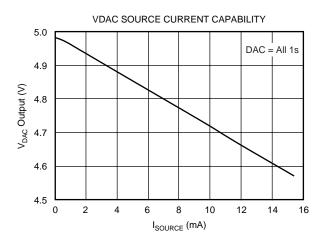

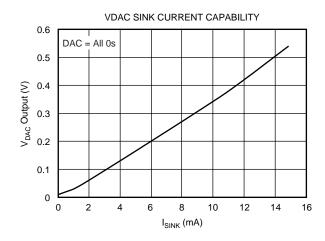

| VOLTAGE DAC OUTPUT CHARACTERISTICS(6)             |                                                     |      |                        |                  |          |

| Output Voltage Range                              |                                                     | AGND |                        | AV <sub>DD</sub> | V        |

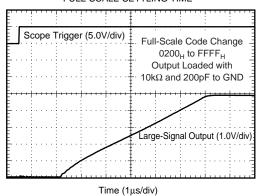

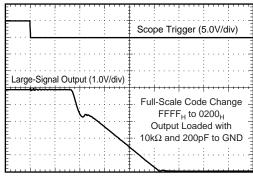

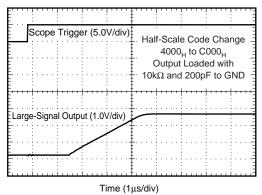

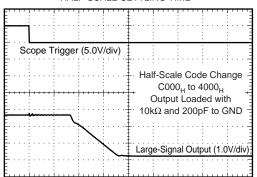

| Output Voltage Settling Time                      | To $\pm 0.003\%$ FSR, $0200_H$ to FD00 <sub>H</sub> |      | 8                      |                  | μs       |

| Slew Rate                                         |                                                     |      | 1                      |                  | V/μs     |

| DC Output Impedance                               |                                                     |      | 7                      |                  | Ω        |

| Short-Circuit Current                             | All 1s Loaded to DAC Register                       |      | 20                     |                  | mA       |

| IDAC OUTPUT CHARACTERISTICS                       |                                                     |      |                        |                  |          |

| Full-Scale Output Current                         | Maximum $V_{REF} = 2.5V$                            |      | 25                     |                  | mA       |

| Maximum Short-Circuit Current Duration            |                                                     |      | Indefinite             |                  |          |

| Compliance Voltage                                |                                                     |      | AV <sub>DD</sub> - 1.5 |                  | V        |

| Relative Accuracy                                 | Over Full Range                                     |      | 0.185                  |                  | % of FSR |

| Zero Code Error                                   |                                                     |      | 0.5                    |                  | % of FSR |

| Full-Scale Error                                  |                                                     |      | -0.4                   |                  | % of FSR |

| Gain Error                                        |                                                     |      | -0.6                   |                  | % of FSR |

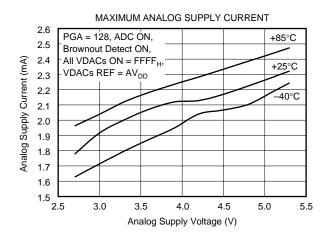

| ANALOG POWER-SUPPLY REQUIREMENTS                  |                                                     |      |                        |                  |          |

| Power-Supply Voltage                              | AV <sub>DD</sub>                                    | 4.75 |                        | 5.25             | V        |

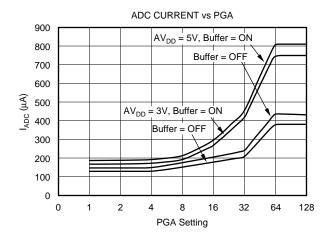

| Analog Current $I_{ADC} + I_{VREF}$               | Analog OFF, PDAD = 1                                |      | < 1                    |                  | nA       |

| ADC Current I <sub>ADC</sub>                      | PGA = 1, Buffer OFF                                 |      | 200                    |                  | μΑ       |

|                                                   | PGA = 128, Buffer OFF                               |      | 500                    |                  | μΑ       |

|                                                   | PGA = 1, Buffer ON                                  |      | 240                    |                  | μΑ       |

|                                                   | PGA = 128, Buffer ON                                |      | 850                    |                  | μΑ       |

| VDAC Current I <sub>VDAC</sub>                    | Excluding Load Current External Reference           |      | 250                    |                  | μΑ       |

| V <sub>REF</sub> Supply Current I <sub>VREF</sub> | ADC ON, V <sub>DAC</sub> OFF                        |      | 250                    |                  | μΑ       |

NOTES: (1) Calibration can minimize these errors. (2) The gain calibration cannot have a REF IN+ of more than  $AV_{DD} - 1.5V$  with buffer ON. To calibrate gain, turn buffer off. (3)  $DV_{OUT}$  is change in digital result. (4) 12pF switched capacitor at  $f_{SAMP}$  clock frequency (see Figure 6). (5) Linearity calculated using a reduced code range of 512 to 65024; output unloaded. (6) Ensured by design and characterization, not production tested.

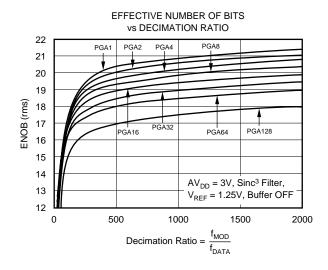

## ELECTRICAL CHARACTERISTICS: $AV_{DD} = 3V$

All specifications from T<sub>MIN</sub> to T<sub>MAX</sub>, AV<sub>DD</sub> = +3V, DV<sub>DD</sub> = +2.7V to 5.25V, f<sub>MOD</sub> = 15.625kHz, PGA = 1, Buffer ON, f<sub>DATA</sub> = 10Hz, Bipolar, and V<sub>REF</sub>  $\equiv$  (REF IN+) - (REF IN-) = +1.25V, unless otherwise noted.

|                                  |                                    |             | MSC1211Yx                    |                        |              |

|----------------------------------|------------------------------------|-------------|------------------------------|------------------------|--------------|

| PARAMETER                        | CONDITION                          | MIN         | TYP                          | MAX                    | UNITS        |

| ANALOG INPUT (AINO-AIN7, AINCOM) |                                    |             |                              |                        |              |

| Analog Input Range               | Buffer OFF                         | AGND - 0.1  |                              | AV <sub>DD</sub> + 0.1 | V            |

|                                  | Buffer ON                          | AGND + 50mV |                              | AV <sub>DD</sub> – 1.5 | V            |

| Full-Scale Input Voltage Range   | (In+) – (In–) See Figure 4         |             |                              | ±V <sub>REF</sub> /PGA | V            |

| Differential Input Impedance     | Buffer OFF                         |             | 5/PGA                        |                        | ΜΩ           |

| Input Current                    | Buffer ON                          |             | 0.5                          |                        | nA           |

| Bandwidth                        |                                    |             |                              |                        |              |

| Fast Settling Filter             | −3dB                               |             | 0.469 • f <sub>DATA</sub>    |                        |              |

| Sinc <sup>2</sup> Filter         | -3dB                               |             | 0.318 • f <sub>DATA</sub>    |                        |              |

| Sinc <sup>3</sup> Filter         | -3dB                               |             | 0.262 • f <sub>DATA</sub>    |                        |              |

| Programmable Gain Amplifier      | User-Selectable Gain Ranges        | 1           |                              | 128                    | _            |

| Input Capacitance                | Buffer On                          |             | 4                            |                        | pF           |

| Input Leakage Current            | Multiplexer Channel Off, T = +25°C |             | 0.5                          |                        | pA           |

| Burnout Current Sources          | Sensor Input Open Circuit          |             | ±2                           |                        | μΑ           |

| ADC OFFSET DAC                   |                                    |             |                              |                        |              |

| Offset DAC Range                 |                                    |             | ±V <sub>REF</sub> /(2 • PGA) |                        | V            |

| Offset DAC Monotonicity          |                                    | 8           |                              |                        | Bits         |

| Offset DAC Gain Error            |                                    |             | ±1.5                         |                        | % of Range   |

| Offset DAC Gain Error Drift      |                                    |             | 1                            |                        | ppm/°C       |

| SYSTEM PERFORMANCE               |                                    |             |                              |                        |              |

| Resolution                       |                                    | 24          |                              |                        | Bits         |

| ENOB                             |                                    |             | 22                           |                        | Bits         |

| Output Noise                     |                                    | See 7       | Typical Characte             | eristics               |              |

| No Missing Codes                 | Sinc <sup>3</sup> Filter           | 24          | <br>                         | Ì                      | Bits         |

| Integral Nonlinearity            | End Point Fit, Differential Input  |             |                              | ±0.0015                | %FSR         |

| Offset Error                     | After Calibration                  |             | 7.5                          |                        | ppm of FS    |

| Offset Drift <sup>(1)</sup>      | Before Calibration                 |             | 0.02                         |                        | ppm of FS/°C |

| Gain Error <sup>(2)</sup>        | After Calibration                  |             | 0.005                        |                        | %            |

| Gain Error Drift <sup>(1)</sup>  | Before Calibration                 |             | 1.0                          |                        | ppm/°C       |

| System Gain Calibration Range    |                                    | 80          |                              | 120                    | % of FS      |

| System Offset Calibration Range  |                                    | -50         |                              | 50                     | % of FS      |

## ELECTRICAL CHARACTERISTICS: AV<sub>DD</sub> = 3V (Cont.)

All specifications from  $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD}$  = +3V,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 15.625kHz, PGA = 1, Buffer ON,  $f_{DATA}$  = 10Hz, and Bipolar,  $V_{REF}$   $\equiv$  (REF IN+) – (REF IN-) = +1.25V, unless otherwise noted. For  $V_{DAC}$ ,  $V_{REF}$  =  $AV_{DD}$ ,  $V_{REF}$  =  $AV_{DD}$ ,  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$ , and  $V_{REF}$  = 10H $\Omega$

|                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                           | MSC1211Yx            |                                                                            |                                                     | _                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                                                              | CONDITION                                                                                                                                                                                                                                 | MIN                  | TYP MAX                                                                    |                                                     | UNITS                                                    |  |

| SYSTEM PERFORMANCE (Cont.) Common-Mode Rejection  Normal Mode Rejection  Power-Supply Rejection                                                                                                                                                                                        | At DC $f_{CM} = 60Hz$ , $f_{DATA} = 10Hz$ $f_{CM} = 50Hz$ , $f_{DATA} = 50Hz$ $f_{CM} = 60Hz$ , $f_{DATA} = 60Hz$ $f_{SIG} = 50Hz$ , $f_{DATA} = 60Hz$ $f_{SIG} = 60Hz$ , $f_{DATA} = 60Hz$ At DC, $dB = -20log(DV_{OLIT}/DV_{DD})^{(3)}$ | 100                  | 115<br>130<br>120<br>120<br>100<br>100<br>85                               |                                                     | dB<br>dB<br>dB<br>dB<br>dB<br>dB                         |  |

| VOLTAGE REFERENCE INPUTS                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           |                      |                                                                            |                                                     |                                                          |  |

| Reference Input Range ADC V <sub>REF</sub> Common-Mode Rejection Input Current <sup>(4)</sup> DAC Reference Current                                                                                                                                                                    | REF IN+, REF IN-<br>$V_{REF} \equiv (REF IN+) - (REF IN-)$<br>At DC<br>$V_{REF} = 1.25V$ , ADC Only<br>For each DAC, 3V Reference                                                                                                         | 0.0<br>0.3           | 1.25<br>110<br>10<br>25                                                    | AV <sub>DD</sub> <sup>(2)</sup><br>AV <sub>DD</sub> | V<br>V<br>dB<br>μA<br>μA                                 |  |

| ON-CHIP VOLTAGE REFERENCE  Output Voltage  Power-Supply Rejection Ratio Short-Circuit Current Source Short-Circuit Current Sink Short-Circuit Duration Drift  Output Impedance Startup Time from Power ON Temperature Sensor Temperature Sensor Voltage Temperature Sensor Coefficient | VREFH = 0 at +25°C, PGA = 1, 2, 4, 8  Sink or Source  Sourcing 100 $\mu$ A $C_{REFOUT} = 0.1\mu$ F $T = +25$ °C                                                                                                                           | 1.245                | 1.25<br>65<br>2.6<br>50<br>Indefinite<br>5<br>3<br>8                       | 1.255                                               | V<br>dB<br>mA<br>μA<br>ppm/°C<br>Ω<br>ms<br>mV<br>μV/°C  |  |

| VOLTAGE DAC STATIC PERFORMANCE (5) Resolution Relative Accuracy Differential Nonlinearity Zero Code Error Full-Scale Error Gain Error Zero Code Error Drift Gain Temperature Coefficient                                                                                               | Ensured Monotonic by Design<br>All 0s Loaded to DAC Register<br>All 1s Loaded to DAC Register                                                                                                                                             | 16<br>-1.25<br>-1.25 | ±0.05<br>+13<br>0<br>0<br>±20<br>±5                                        | ±0.146<br>±1<br>+35<br>±1.25                        | Bits % of FSR LSB mV % of FSR % of FSR µV/°C ppm of FSR/ |  |

| VOLTAGE DAC OUTPUT CHARACTERISTICS <sup>(t)</sup> Output Voltage Range Output Voltage Settling Time Slew Rate DC Output Impedance Short-Circuit Current                                                                                                                                | To ±0.003% FSR, 0200 <sub>H</sub> to FD00 <sub>H</sub> All 1s Loaded to DAC Register                                                                                                                                                      | AGND                 | 8<br>1<br>7<br>16                                                          | AV <sub>DD</sub>                                    | V<br>μs<br>V/μs<br>Ω<br>mA                               |  |

| IDAC OUTPUT CHARACTERISTICS Full-Scale Output Current Maximum Short-Circuit Current Duration Compliance Voltage Relative Accuracy Zero Code Error Full-Scale Error Gain Error                                                                                                          | Maximum V <sub>REF</sub> = 2.5V<br>Over Full Range                                                                                                                                                                                        |                      | 25<br>Indefinite<br>AV <sub>DD</sub> - 1.5<br>0.185<br>0.5<br>-0.4<br>-0.6 |                                                     | mA % of FSR % of FSR % of FSR % of FSR                   |  |

| POWER-SUPPLY REQUIREMENTS  Power-Supply Voltage  Analog Current  ADC Current  VDAC Current $I_{ADC} + I_{VREF}$ $I_{ADC}$ $I_{VDAC}$ $I_{VREF}$ $I_{VREF}$ $I_{VREF}$                                                                                                                  | AV <sub>DD</sub> Analog OFF, PDAD = 1 PGA = 1, Buffer OFF PGA = 128, Buffer OFF PGA = 1, Buffer ON PGA = 128, Buffer ON Excluding Load Current External Reference                                                                         | 2.7                  | < 1<br>200<br>500<br>240<br>850<br>250<br>250                              | 3.6                                                 | V<br>nA<br>µA<br>µA<br>µA<br>µA<br>µA                    |  |

NOTES: (1) Calibration can minimize these errors. (2) The gain calibration cannot have a REF IN+ of more than  $AV_{DD} - 1.5V$  with buffer ON. To calibrate gain, turn buffer off. (3)  $DV_{OUT}$  is change in digital result. (4) 12pF switched capacitor at  $f_{SAMP}$  clock frequency (see Figure 6). (5) Linearity calculated using a reduced code range of 512 to 65024; output unloaded. (6) Ensured by design and characterization, not production tested.

## DIGITAL CHARACTERISTICS: $DV_{DD} = 2.7V$ to 5.25V

All specifications from  $\mathsf{T}_{\mathsf{MIN}}$  to  $\mathsf{T}_{\mathsf{MAX}},$  unless otherwise specified.

|                                                             |                                                    | MSC1211Yx              |                        |                        |       |

|-------------------------------------------------------------|----------------------------------------------------|------------------------|------------------------|------------------------|-------|

| PARAMETER                                                   | CONDITION                                          | MIN                    | TYP                    | MAX                    | UNITS |

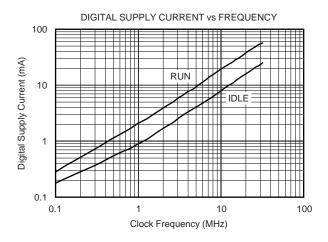

| POWER-SUPPLY REQUIREMENTS                                   |                                                    |                        |                        |                        |       |

|                                                             | DV <sub>DD</sub>                                   | 2.7                    |                        | 3.6                    | V     |

|                                                             | Normal Mode, f <sub>OSC</sub> = 1MHz               |                        | 1.3                    |                        | mA    |

|                                                             | Normal Mode, f <sub>OSC</sub> = 8MHz               |                        | 6                      |                        | mA    |

|                                                             | Stop Mode                                          |                        | 100                    |                        | nA    |

|                                                             | DV <sub>DD</sub>                                   | 4.75                   |                        | 5.25                   | V     |

|                                                             | Normal Mode, f <sub>OSC</sub> = 1MHz               |                        | 2.2                    |                        | mA    |

|                                                             | Normal Mode, f <sub>OSC</sub> = 8MHz               |                        | 14                     |                        | mA    |

|                                                             | Stop Mode                                          |                        | 100                    |                        | nA    |

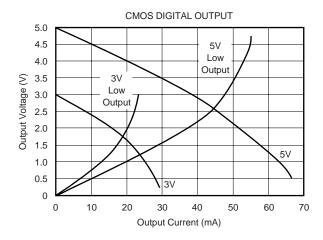

| DIGITAL INPUT/OUTPUT (CMOS)                                 |                                                    |                        |                        |                        |       |

| Logic Level: V <sub>IH</sub> (except XIN pin)               |                                                    | 0.6 • DV <sub>DD</sub> |                        | DV <sub>DD</sub>       | V     |

| V <sub>II.</sub> (except XIN pin)                           |                                                    | DGND                   |                        | 0.2 • DV <sub>DD</sub> | V     |

| Ports 0-3, Input Leakage Current, Input Mode                | $V_{IH} = DV_{DD}$ or $V_{IH} = 0V$                | -10                    | 0                      | +10                    | μΑ    |

| Pins EA, XIN Input Leakage Current                          |                                                    |                        | 0                      |                        | μΑ    |

| V <sub>OL</sub> , ALE, PSEN, Ports 0-3, All Output Modes    | I <sub>OL</sub> = 1mA                              | DGND                   |                        | 0.4                    | V     |

| V <sub>OL</sub> , ALE, PSEN, Ports 0-3, All Output Modes    | $I_{OL} = 30 \text{mA}, 3 \text{V} (20 \text{mA})$ |                        | 1.5                    |                        | V     |

| V <sub>OH</sub> , ALE, PSEN, Ports 0-3, Strong Drive Output | I <sub>OH</sub> = 1mA                              | $DV_{DD} - 0.4$        | $DV_{DD} - 0.1$        | DV <sub>DD</sub>       | V     |

| V <sub>OH</sub> , ALE, PSEN, Ports 0-3, Strong Drive Output | $I_{OH} = 30 \text{mA}, 3V (20 \text{mA})$         |                        | DV <sub>DD</sub> - 1.5 |                        | V     |

| Ports 0-3 Pull-Up Resistors                                 |                                                    |                        | 9                      |                        | kΩ    |

| Pins ALE, PSEN, Pull-Up Resistors                           | Flash Programming Mode Only                        |                        | 9                      |                        | kΩ    |

| Pin RST, Pull-Down Resistor                                 |                                                    |                        | 200                    |                        | kΩ    |

## FLASH MEMORY CHARACTERISTICS: $DV_{DD} = 2.7V$ to 5.25V

$t_{USEC}$  = 1 $\mu$ s,  $t_{MSEC}$  = 1ms

|                                                      |                             | MSC1211Yx |           |     |             |

|------------------------------------------------------|-----------------------------|-----------|-----------|-----|-------------|

| PARAMETER                                            | CONDITION                   | MIN       | TYP       | MAX | UNITS       |

| Flash Memory Endurance                               |                             | 100,000   | 1,000,000 |     | cycles      |

| Flash Memory Data Retention Mass and Page Erase Time | Set with FER Value in FTCON | 100<br>10 |           |     | Years<br>ms |

| Flash Memory Data Retention                          | Set with FWR Value in FTCON | 30        |           | 40  | μs          |

## AC ELECTRICAL CHARACTERISTICS<sup>(1)(2)</sup>: $DV_{DD} = 2.7V$ to 5.25V

|                                 |        |                                                                                      | 2.7V 1                   | to 3.6V                                    | 4.75V                   | to 5.25V                                    |       |

|---------------------------------|--------|--------------------------------------------------------------------------------------|--------------------------|--------------------------------------------|-------------------------|---------------------------------------------|-------|

| SYMBOL                          | FIGURE | PARAMETER                                                                            | MIN                      | MAX                                        | MIN                     | MAX                                         | UNITS |

| System Clock                    |        |                                                                                      |                          |                                            |                         |                                             |       |

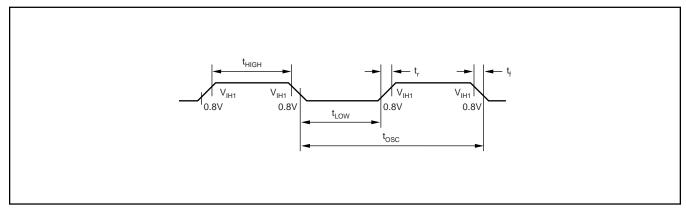

| f <sub>OSC</sub> <sup>(3)</sup> | D      | External Crystal Frequency (f <sub>OSC</sub> )                                       | 1                        | 16                                         | 1                       | 30                                          | MHz   |

| 1/t <sub>OSC</sub> (3)          | D      | External Clock Frequency (f <sub>OSC</sub> )                                         | 0                        | 16                                         | 1                       | 30                                          | MHz   |

| f <sub>OSC</sub> (3)            | D      | External Ceramic Resonator Frequency (f <sub>OSC</sub> )                             | 1                        | 12                                         | 1                       | 12                                          | MHz   |

| Program Memory                  |        |                                                                                      |                          |                                            |                         |                                             |       |

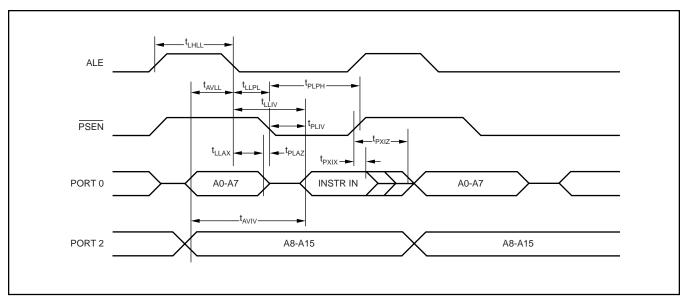

| t <sub>LHLL</sub>               | Α      | ALE Pulse Width                                                                      | 1.5t <sub>CLK</sub> - 5  |                                            | 1.5t <sub>CLK</sub> - 5 |                                             | ns    |

| t <sub>AVLL</sub>               | Α      | Address Valid to ALE LOW                                                             | 0.5t <sub>CLK</sub> - 10 |                                            | 0.5t <sub>CLK</sub> - 7 |                                             | ns    |

| t <sub>LLAX</sub>               | Α      | Address Hold After ALE LOW                                                           | 0.5t <sub>CLK</sub>      |                                            | 0.5t <sub>CLK</sub>     |                                             | ns    |

| t <sub>LLIV</sub>               | Α      | ALE LOW to Valid Instruction In                                                      |                          | 2.5t <sub>CLK</sub> - 35                   |                         | 2.5t <sub>CLK</sub> – 25                    | ns    |

| t <sub>LLPL</sub>               | Α      | ALE LOW to PSEN LOW                                                                  | 0.5t <sub>CLK</sub>      |                                            | 0.5t <sub>CLK</sub>     |                                             | ns    |

| t <sub>PLPH</sub>               | Α      | PSEN Pulse Width                                                                     | 2t <sub>CLK</sub> - 5    |                                            | 2t <sub>CLK</sub> - 5   |                                             | ns    |

| t <sub>PLIV</sub>               | Α      | PSEN LOW to Valid Instruction In                                                     |                          | 2t <sub>CLK</sub> - 40                     |                         | 2t <sub>CLK</sub> - 30                      | ns    |

| t <sub>PXIX</sub>               | Α      | Input Instruction Hold After PSEN                                                    | 5                        |                                            | <del>-</del> 5          |                                             | ns    |

| t <sub>PXIZ</sub>               | Α      | Input Instruction Float After PSEN                                                   |                          | t <sub>CLK</sub> - 5                       |                         | t <sub>CLK</sub>                            | ns    |

| t <sub>AVIV</sub>               | Α      | Address to Valid Instruction In                                                      |                          | 3t <sub>CLK</sub> - 40                     |                         | 3t <sub>CLK</sub> - 25                      | ns    |

| t <sub>PLAZ</sub>               | Α      | PSEN LOW to Address Float                                                            |                          | 0                                          |                         | 0                                           | ns    |

| Data Memory                     |        |                                                                                      |                          |                                            |                         |                                             |       |

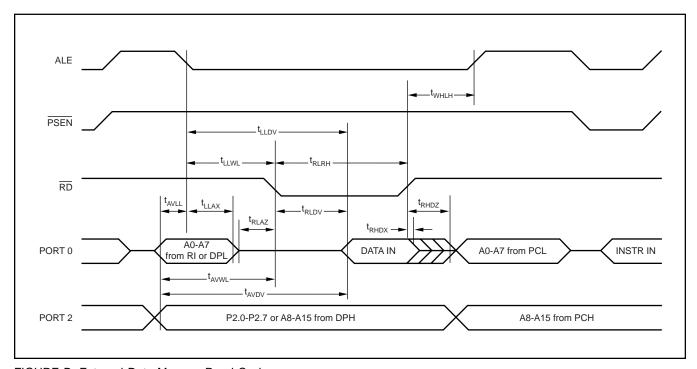

| t <sub>RLRH</sub>               | В      | $\overline{RD}$ Pulse Width $(t_{MCS} = 0)^{(4)}$                                    | 2t <sub>CLK</sub> - 5    |                                            | 2t <sub>CLK</sub> - 5   |                                             | ns    |

|                                 | В      | $\overline{RD}$ Pulse Width $(t_{MCS} > 0)^{(4)}$                                    | $t_{MCS} - 5$            |                                            | $t_{MCS} - 5$           |                                             | ns    |

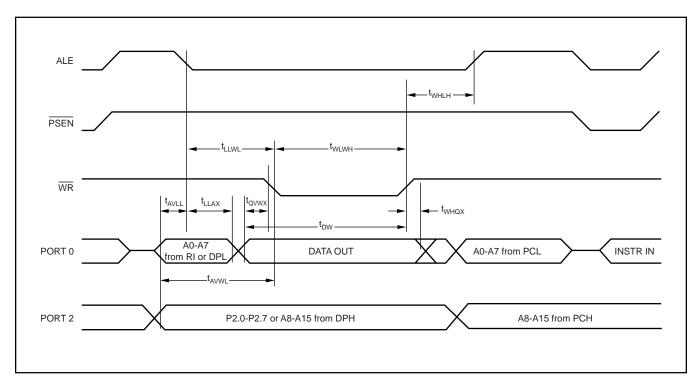

| t <sub>WLWH</sub>               | С      | $\overline{\text{WR}}$ Pulse Width $(t_{\text{MCS}} = 0)^{(4)}$                      | 2t <sub>CLK</sub> - 5    |                                            | 2t <sub>CLK</sub> - 5   |                                             | ns    |

|                                 | С      | Pulse Width $(t_{MCS} > 0)^{(4)}$                                                    | $t_{MCS} - 5$            |                                            | $t_{MCS} - 5$           |                                             | ns    |

| $t_{RLDV}$                      | В      | $\overline{RD}$ LOW to Valid Data In $(t_{MCS} = 0)^{(4)}$                           |                          | 2t <sub>CLK</sub> - 40                     |                         | 2t <sub>CLK</sub> - 30                      | ns    |

|                                 | В      | $\overline{RD}$ LOW to Valid Data In $(t_{MCS} > 0)^{(4)}$                           |                          | t <sub>MCS</sub> - 40                      |                         | t <sub>MCS</sub> - 30                       | ns    |

| t <sub>RHDX</sub>               | В      | Data Hold After Read                                                                 | -5                       |                                            | <b>-</b> 5              |                                             | ns    |

| t <sub>RHDZ</sub>               | В      | Data Float After Read (t <sub>MCS</sub> = 0) <sup>(4)</sup>                          |                          | t <sub>CLK</sub>                           |                         | t <sub>CLK</sub>                            | ns    |

|                                 | В      | Data Float After Read $(t_{MCS} > 0)^{(4)}$                                          |                          | 2t <sub>CLK</sub>                          |                         | 2t <sub>CLK</sub>                           | ns    |

| t <sub>LLDV</sub>               | В      | ALE LOW to Valid Data In $(t_{MCS} = 0)^{(4)}$                                       |                          | 2.5t <sub>CLK</sub> - 40                   |                         | 2.5t <sub>CLK</sub> - 25                    | ns    |

|                                 | В      | ALE LOW to Valid Data In $(t_{MCS} > 0)^{(4)}$                                       |                          | $t_{CLK} + t_{MCS} - 40$                   |                         | $t_{CLK} + t_{MCS} - 25$                    | ns    |

| t <sub>AVDV</sub>               | В      | Address to Valid Data In $(t_{MCS} = 0)^{(4)}$                                       |                          | 3t <sub>CLK</sub> - 40                     |                         | 3t <sub>CLK</sub> - 25                      | ns    |

|                                 | В      | Address to Valid Data In $(t_{MCS} > 0)^{(4)}$                                       |                          | 1.5t <sub>CLK</sub> +t <sub>MCS</sub> - 40 |                         | 1.5t <sub>CLK</sub> + t <sub>MCS</sub> - 25 | ns    |

| t <sub>LLWL</sub>               | B, C   | ALE LOW to $\overline{RD}$ or $\overline{WR}$ LOW $(t_{MCS} = 0)^{(4)}$              | 0.5t <sub>CLK</sub> - 5  | 0.5t <sub>CLK</sub> + 5                    | 0.5t <sub>CLK</sub> - 5 | 0.5t <sub>CLK</sub> + 5                     | ns    |

|                                 | B, C   | ALE LOW to $\overline{RD}$ or $\overline{WR}$ LOW $(t_{MCS} > 0)^{(4)}$              | t <sub>CLK</sub> - 5     | t <sub>CLK</sub> + 5                       | t <sub>CLK</sub> - 5    | t <sub>CLK</sub> + 5                        | ns    |

| t <sub>AVWL</sub>               | B, C   | Address to $\overline{RD}$ or $\overline{WR}$ LOW $(t_{MCS} = 0)^{(4)}$              | t <sub>CLK</sub> - 5     |                                            | t <sub>CLK</sub> - 5    |                                             | ns    |

|                                 | B, C   | Address to $\overline{RD}$ or $\overline{WR}$ LOW $(t_{MCS} > 0)^{(4)}$              | 2t <sub>CLK</sub> - 5    |                                            | 2t <sub>CLK</sub> – 5   |                                             | ns    |

| t <sub>QVWX</sub>               | С      | Data Valid to WR Transition                                                          | -8                       |                                            | <b>-</b> 5              |                                             | ns    |

| $t_{WHQX}$                      | С      | Data Hold After WR                                                                   | t <sub>CLK</sub> - 8     |                                            | t <sub>CLK</sub> - 5    |                                             | ns    |

| t <sub>RLAZ</sub>               | В      | RD LOW to Address Float                                                              |                          | -0.5t <sub>CLK</sub> - 5                   |                         | -0.5t <sub>CLK</sub> - 5                    | ns    |

| t <sub>WHLH</sub>               | В, С   | $\overline{RD}$ or $\overline{WR}$ HIGH to ALE HIGH $(t_{MCS} = 0)^{(4)}$            | <b>-</b> 5               | 5                                          | <b>-</b> 5              | 5                                           | ns    |

|                                 | B, C   | $\overline{RD}$ or $\overline{WR}$ HIGH to ALE HIGH ( $t_{MCS} > 0$ ) <sup>(4)</sup> | t <sub>CLK</sub> - 5     | t <sub>CLK</sub> + 5                       | t <sub>CLK</sub> - 5    | t <sub>CLK</sub> + 5                        | ns    |

| External Clock                  |        |                                                                                      |                          |                                            |                         |                                             |       |

| t <sub>HIGH</sub>               | D      | HIGH Time <sup>(5)</sup>                                                             | 15                       |                                            | 10                      |                                             | ns    |

| t <sub>LOW</sub>                | D      | LOW Time <sup>(5)</sup>                                                              | 15                       |                                            | 10                      |                                             | ns    |

| t <sub>R</sub>                  | D      | Rise Time <sup>(5)</sup>                                                             |                          | 5                                          |                         | 5                                           | ns    |

| t <sub>F</sub>                  | D      | Fall Time <sup>(5)</sup>                                                             |                          | 5                                          |                         | 5                                           | ns    |

|                                 | ı -    |                                                                                      |                          | 1                                          |                         | 1                                           |       |

NOTES: (1) Parameters are valid over operating temperature range, unless otherwise specified. (2) Load capacitance for Port 0, ALE, and  $\overline{\text{PSEN}} = 100\text{pF}$ , load capacitance for all other outputs = 80pF. (3)  $t_{\text{CLK}} = 1/t_{\text{OSC}} = 0$  ne oscillator clock period for clock divider = 1. (4)  $t_{\text{MCS}}$  is a time period related to the Stretch MOVX selection. The following table shows the value of  $t_{\text{MCS}}$  for each stretch selection. (5) These values are characterized but not 100% production tested.

| MD2 | MD1 | MD0 | MOVX DURATION              | t <sub>MCS</sub>   |

|-----|-----|-----|----------------------------|--------------------|

| 0   | 0   | 0   | 2 Machine Cycles           | 0                  |

| 0   | 0   | 1   | 3 Machine Cycles (default) | 4t <sub>CLK</sub>  |

| 0   | 1   | 0   | 4 Machine Cycles           | 8t <sub>CLK</sub>  |

| 0   | 1   | 1   | 5 Machine Cycles           | 12t <sub>CLK</sub> |

| 1   | 0   | 0   | 6 Machine Cycles           | 16t <sub>CLK</sub> |

| 1   | 0   | 1   | 7 Machine Cycles           | 20t <sub>CLK</sub> |

| 1   | 1   | 0   | 8 Machine Cycles           | 24t <sub>CLK</sub> |

| 1   | 1   | 1   | 9 Machine Cycles           | 28t <sub>CLK</sub> |

#### **EXPLANATION OF THE AC SYMBOLS**

Each Timing Symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designators are:

I—Instruction (program memory contents)

X—No Longer a Valid Logic Level

L—Logic Level LOW, or ALE

P—PSEN

Examples: (1) t<sub>AVLL</sub> = Time for address valid to ALE LOW. (2) t<sub>LLPL</sub> = Time for ALE LOW to PSEN LOW.

FIGURE A. External Program Memory Read Cycle.

FIGURE B. External Data Memory Read Cycle.

FIGURE C. External Data Memory Write Cycle.

FIGURE D. External Clock Drive CLK.

#### **RESET AND POWER-ON TIMING**

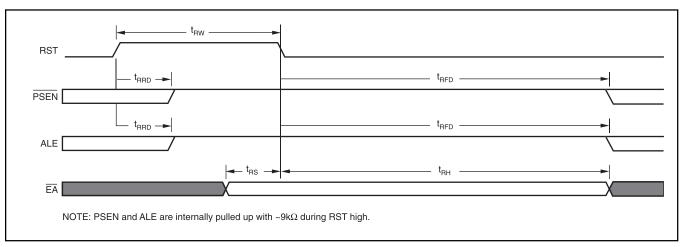

FIGURE E. Reset Timing.

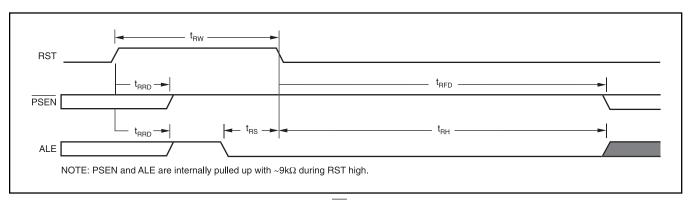

FIGURE F. Parallel Flash Programming Power-On Timing ( $\overline{\mathsf{EA}}$  is ignored).

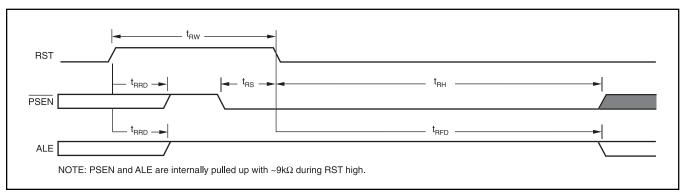

FIGURE G. Serial Flash Programming Power-On Timing (EA is ignored).

| SYMBOL           | PARAMETER                               | MIN                                      | MAX                      | UNIT |

|------------------|-----------------------------------------|------------------------------------------|--------------------------|------|

| t <sub>RW</sub>  | RST width                               | 2 t <sub>OSC</sub>                       | _                        | ns   |

| t <sub>RRD</sub> | RST rise to PSEN ALE internal pull high | _                                        | 5                        | μs   |

| t <sub>RFD</sub> | RST falling to PSEN and ALE start       | _                                        | $(2^{17} + 512) t_{OSC}$ | ns   |

| t <sub>RS</sub>  | Input signal to RST falling setup time  | tosc                                     | _                        | ns   |

| t <sub>RH</sub>  | RST falling to input signal hold time   | (2 <sup>17</sup> + 512) t <sub>OSC</sub> | _                        | ns   |

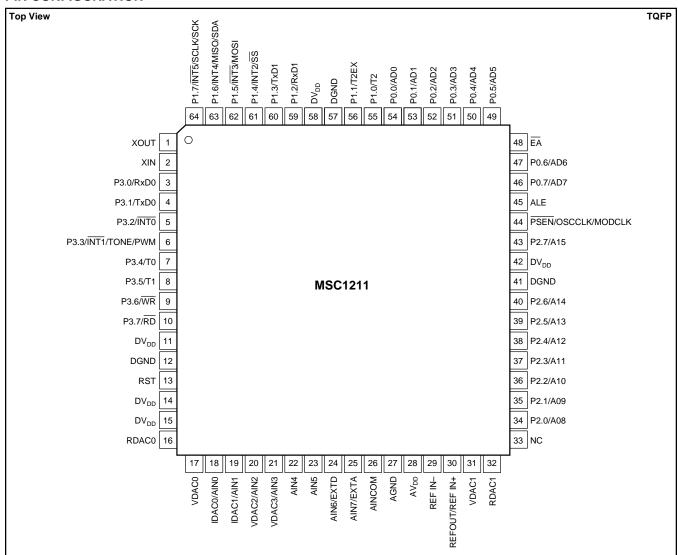

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN #              | NAME       | DESCRIPTION                                                                                                                                                                           |                                                                                                                      |                                      |  |  |  |  |

|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| 1                  | XOUT       | The crystal oscillator pin XOUT supports parallel resonant AT cut crystals and ceramic resonators. XOUT serves as the output of the crystal amplifier.                                |                                                                                                                      |                                      |  |  |  |  |

| 2                  | XIN        | The crystal oscillator pin XIN supports parallel resonant AT cut crystals and ceramic resonators. XIN can also be an input if there is an external clock source instead of a crystal. |                                                                                                                      |                                      |  |  |  |  |

| 3-10               | P3.0-P3.7  | Port 3 is a bidirectional I/O port. The alter Port 3—Alternate Functions:                                                                                                             | Port 3 is a bidirectional I/O port. The alternate functions for Port 3 are listed below. Port 3—Alternate Functions: |                                      |  |  |  |  |

|                    |            | PORT                                                                                                                                                                                  | ALTERNATE                                                                                                            | MODE                                 |  |  |  |  |

|                    |            | P3.0                                                                                                                                                                                  | RxD0                                                                                                                 | Serial Port 0 Input                  |  |  |  |  |

|                    |            | P3.1                                                                                                                                                                                  | TxD0                                                                                                                 | Serial Port 0 Output                 |  |  |  |  |

|                    |            | P3.2                                                                                                                                                                                  | ĪNT0                                                                                                                 | External Interrupt 0                 |  |  |  |  |

|                    |            | P3.3   Ī                                                                                                                                                                              | NT1/TONE/PWM                                                                                                         | External Interrupt 1/TONE/PWM Output |  |  |  |  |

|                    |            | P3.4                                                                                                                                                                                  | T0                                                                                                                   | Timer 0 External Input               |  |  |  |  |

|                    |            | P3.5                                                                                                                                                                                  | T1                                                                                                                   | Timer 1 External Input               |  |  |  |  |

|                    |            | P3.6                                                                                                                                                                                  | WR                                                                                                                   | External Data Memory Write Strobe    |  |  |  |  |

|                    |            | P3.7                                                                                                                                                                                  | RD                                                                                                                   | External Data Memory Read Strobe     |  |  |  |  |

| 11, 14, 15, 42, 58 | $DV_DD$    | Digital Power Supply                                                                                                                                                                  |                                                                                                                      |                                      |  |  |  |  |

| 12, 41, 57         | DGND       | Digital Ground                                                                                                                                                                        |                                                                                                                      |                                      |  |  |  |  |

| 13                 | RST        | A HIGH on the reset input for two tosc pe                                                                                                                                             | eriods will reset the                                                                                                | e device.                            |  |  |  |  |

| 16                 | RDAC0      | RDAC0 Output                                                                                                                                                                          |                                                                                                                      |                                      |  |  |  |  |

| 17                 | VDAC0      | VDAC0 Output                                                                                                                                                                          |                                                                                                                      |                                      |  |  |  |  |

| 27                 | AGND       | Analog Ground                                                                                                                                                                         |                                                                                                                      |                                      |  |  |  |  |

| 18                 | IDAC0/AIN0 | IDAC0 Output/Analog Input Channel 0                                                                                                                                                   |                                                                                                                      |                                      |  |  |  |  |

| 19                 | IDAC1/AIN1 | IDAC1 Output/Analog Input Channel 1                                                                                                                                                   |                                                                                                                      |                                      |  |  |  |  |

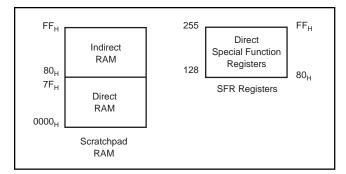

#### **PIN DESCRIPTIONS (Cont.)**